Микропроцессоры Токхайм / 8.1. СХЕМА И НАЗНАЧЕНИЕ ВЫВОДОВ

.docГлава 8

МИКРОПРОЦЕССОРЫ INTEL 8080/8085

Первый МП был выпущен фирмой Intel в 1971 г. Тогда фирма изготовила и реализовала 4-разрядные МП 4004 и 8-разрядные МП 8008. В 1974 г. пришла очередь МП Intel 8080, который обрабатывает 8-разрядные слова и имеет 16-разрядные адресную шину и указатель стека. Его улучшенным вариантом является МП Intel 8085, в котором содержатся генератор тактовых импульсов, система управления и устройство определения приоритета прерываний, интеграция которых снижает число составляющих микропроцессорную систему ИС. Микропроцессор Intel 8085 работает также с единственным уровнем питающего напряжения +5 В. Он использует те же команды, что и МП Intel 8080, что делает оба устройства совместимыми. Наконец, Intel 8085 имеет две дополнительные команды, располагая, таким образом, большими возможностями благодаря содержащимся в нем дополнительным аппаратным средствам.

Типовой МП (см. гл. 5—7), был упрощенной версией МП Intel 8080/8085, поэтому довольно просто понять его действия.

Более глубокая функциональная интеграция с меньшим числом ИС является эволюционным свойством МП. Совсем недавно простая система могла содержать до 20— 30 ИС. Представленная на рис. 8.1 система содержит их только три. В ней использован МП Intel 8085, который управляет шиной системы и двумя другими специальными ИС интерфейса с периферией.

Составляющие

интерфейса, представленные на рис. 8.1,

являются ИС Intel 8155 и 8355.

Микросхема 8155 содержит

Микросхема 8155 содержит

![]()

2048 бит памяти статического ОЗУ, организованного в память 256x8 бит; она содержит также три порта ВВ и синхронизатор. Два порта ВВ являются универсальными по 8 бит каждый. Третий (6 бит) может быть использован как порт ввода, вывода или в качестве системы сигналов управления для двух других 8-разрядных портов. Схема 8155 программируема и содержит регистр состояния и 14-разрядный счетчик-синхронизатор.

Другое устройство, представленное на рис. 8.1, является ИС интерфейса периферии 8355. Она содержит ПЗУ емкостью 16 384 бит, организованное в память 2048X6 бит, и два универсальных порта ВВ по 8 бит каждый.

8.1. СХЕМА И НАЗНАЧЕНИЕ ВЫВОДОВ

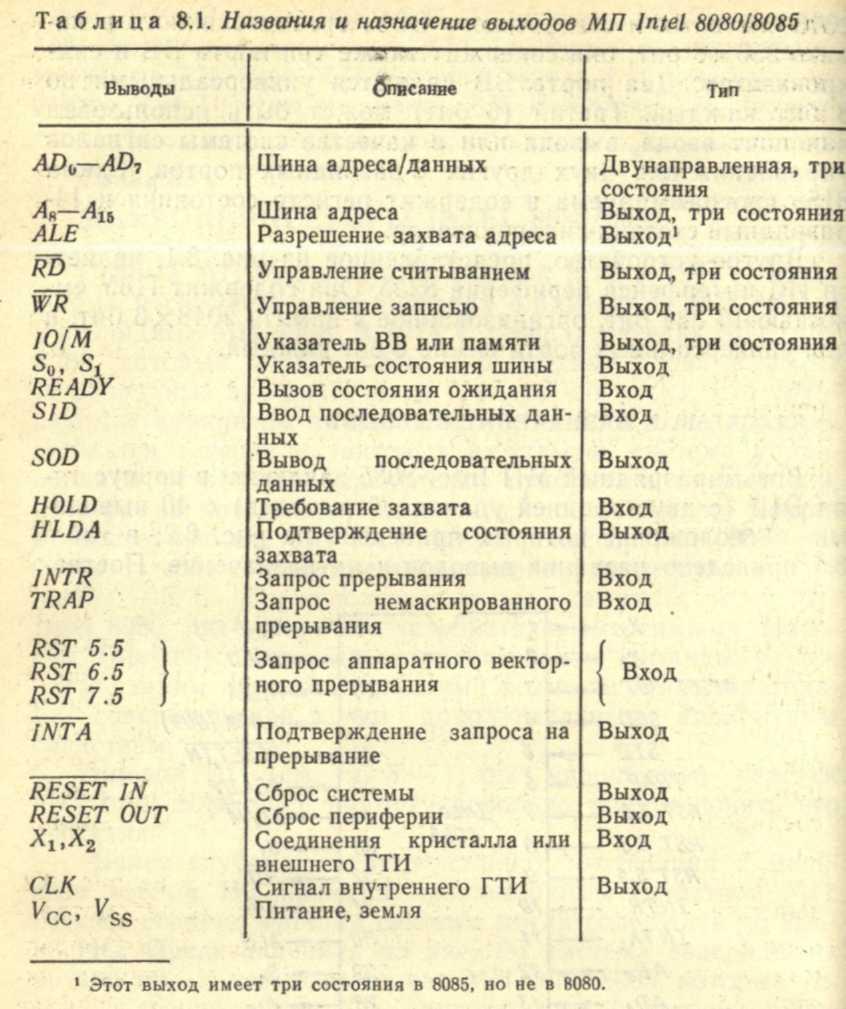

Восьмиразрядный

МП Intel 8085 заключен в корпус типа DIP (с

двусторонней упаковкой выводов) с 40

выводами, расположение которых

приведено на рис. 8.2; в табл. 8.1 приведено

название выводов и их назначение.

Наш типовой МП имел 16 выводов адресных линий и восемь для подсоединения шины данных. Располагая дополнительными возможностями Intel 8085 в DIP-корпусе с 40 выводами не требует дополнительных выводов для обеспечения всех входов и выходов; по этой причине выводы 12— 19 использованы как равноценные линии шины адреса/

/данных (AD0—AD7). Поэтому этот микропроцессор называется устройством с мультиплексированной шиной данных/адреса. Адресные линии восьми младших разрядов разделяют выводы с линиями шины данных. Мультиплексировать — значит выбирать линии поочередно.

При таких определениях мультиплексировать шину адреса/данных означает использовать сначала шину для передачи адреса, затем использовать ее же для выдачи или получения данных. Микропроцессор Intel 8085 снабжен специальным сигналом для того, чтобы информировать периферийные устройства, производит ли мультиплексированная шина операции на адресной шине или на шине данных. Это специальный сигнал, называемый сигналом разрешения захвата адреса (ALE). Заметим, что выводы мультиплексированной шины двунаправлены или могут быть в положении трех состояний. Вывод управления ALE является выходным.

Микропроцессор Intel 8085 (как и типовой процессор) имеет 16 адресных линий. Восемь старших разрядов выведены на выводы А8—А15 (см. рис. 8.2). Как и в случае типового МП, подсоединение к шинам прямое. Эти выводы являются выходами или могут быть в состоянии высокого сопротивления (в третьем состоянии). Другие выводы, идентичные выводам типового МП, являются выводами питания Vcc и Vss, подсоединенными к источнику +5 В. Микропроцессор Intel 8085 снабжен внутренним генератором тактовых импульсов, входы которого Х1 и Х2 обычно соединены с кристаллом. Внутренняя частота МП является половиной частоты кристалла.

Многие выводы МП

Intel 8085, показанные на рис. 8.2, выполняют

функции управления. Аналогичные

рассмотренным для типового МП![]() используются для информации устройства

памяти или УВВ, т.е. определяют, наступило

ли время послать или принять данные по

шине данных (в этом случае — по

мультиплексированной шине). Вход сброса

используются для информации устройства

памяти или УВВ, т.е. определяют, наступило

ли время послать или принять данные по

шине данных (в этом случае — по

мультиплексированной шине). Вход сброса

![]() действует

так же, как это было в типовом МП при

сбросе в 0000Н счетчика команд. Шины

адреса, данных и линии управления

находятся в состоянии высокого

сопротивления в ходе сброса. Когда МП

сбрасывается, вывод RESET OUT (относится

к операции сброса) выдает сигнал в

периферийные устройства, информируя

их, что операция сброса закончена.

действует

так же, как это было в типовом МП при

сбросе в 0000Н счетчика команд. Шины

адреса, данных и линии управления

находятся в состоянии высокого

сопротивления в ходе сброса. Когда МП

сбрасывается, вывод RESET OUT (относится

к операции сброса) выдает сигнал в

периферийные устройства, информируя

их, что операция сброса закончена.

Выход генератора тактовых импульсов CLK МП Intel 8085 функционирует, как и в типовом МП. Вход запроса

прерывания INTR в

МП Intel 8085 является универсальным

прерыванием (как в типовом МП), однако

существует различие в том смысле,

что прерывание INTR в МП Intel 8085 может быть

разрешено или запрещено командами

программы. Кроме входа нормального

запроса на прерывание (INTR) МП Intel 8085

снабжен четырьмя другими входами

прерывания: TRAP, RST7.5, RST6.5, RST5.5. Вход TRAP

является входом прерывания наивысшего

приоритета; следующими по порядку

являются RST7.5, RST6.5, RST5.5 и, наконец, INTR —

самый низкий приоритет. Сигнал TRAP

или один из трех сигналов (RST7.5, RST6.5,

RST5.5) влечет за собой ветвление МП по

вызываемому специальному адресу.

Команды рестартов RST могут быть разрешены

или запрещены программно, но прерывания

по входу TRAP таким образом запрещены

быть не могут. Запрос на прерывание

INTR вызывает переход к новому адресу,

указанному специальной командой,

выданной периферией, когда активизируется

выход, подтверждающий получение

запроса на прерывание![]()

Микропроцессор Intel 8085 снабжен слаборазвитыми вводом и выводом последовательных данных — SID (ввод последовательных данных) и SOD (вывод последовательных данных) (см. рис. 8.2). Отдельный бит данных на выводах SID загружается в наиболее значимый разряд (бит 7) аккумулятора командой RIM в МП Intel 8085. Вывод выхода SOD активизируется или сбрасывается командой SIM в МП.

Рассмотрим вход READY на рис. 8.2. Этот вход информирует МП, что периферия готова выдать или принять данные. Если READY имеет L-уровень в цикле считывания или записи, МП его интерпретирует как требование перейти в состояние ожидания. В этих условиях МП будет ждать до тех пор, пока периферия не просигнализирует, что она готова передать или получить данные. Затем будет продолжаться выполнение цикла записи или считывания. Вход READY удобен при использовании очень медленных по сравнению со скоростью обработки данных в МП устройств памяти или периферии.

Рассмотрим теперь

вход HOLD (входной сигнал требования

захвата) и выход HLDA (подтверждение

состояния захвата), выводы которых

показаны на рис. 8.2. Вход HOLD оповещает

МП, что другое устройство хочет

использовать шины адреса и данных

(это может производиться в ходе ПДП).

По получении сигнала HOLD МП завершает

текущую операцию, затем выводы данных

и адреса![]() ;

;

![]() и

и![]() переводятся в третье состояние, т. е.

исключается взаимодействие с передачами

данных на шинах. Выход HLDA указывает

периферии, что запрос HOLD был получен и

микропроцессор не будет управлять

шинами в следующем цикле тактовых

импульсов.

переводятся в третье состояние, т. е.

исключается взаимодействие с передачами

данных на шинах. Выход HLDA указывает

периферии, что запрос HOLD был получен и

микропроцессор не будет управлять

шинами в следующем цикле тактовых

импульсов.

Выходы![]() ,

S0 и S1 являются сигналами управления,

которые информируют периферию о типе

машинного цикла, выполняемого МП.

Эти типы записаны в табл. 8.2, соответствующие

сочетания выходных сигналов на выводах

,

S0 и S1 являются сигналами управления,

которые информируют периферию о типе

машинного цикла, выполняемого МП.

Эти типы записаны в табл. 8.2, соответствующие

сочетания выходных сигналов на выводах

![]() , S0 и S1 подробно показаны в левых колонках.

, S0 и S1 подробно показаны в левых колонках.

Упражнения

8.1. Intel 8085 представляет собой микропроцессор на

_______ бит, потому что таков размер слов, которыми он

манипулирует.

8.2. Восемь линий ____ (старших, младших) разрядов используют адресную шину, тогда как восемь линий ______(старших, младших) разрядов используют шину _______.

8.3. Шина адреса/данных называется ______ (декодированной мультиплексированной), потому что она функционирует попеременно как шина адреса и как шина данных.

8.4. См. рис. 8.2. Выход ____ служит для оповещения

периферии, что мультиплексированные шины функционируют как адресные.

См. рис. 8.2. Intel 8085 питается напряжением _______.

См. рис. 8.2. Если

входы IO/М и![]() оба

в L-состоянии, МП занят выполнением ______

(считывания, записи)

оба

в L-состоянии, МП занят выполнением ______

(считывания, записи)

в _____ (порт УВВ, память).

8.7. См. рис. 8.2. Если МП находится в цикле записи

(вход READY в L-состоянии), то он ________ (завершает

сразу, переходит в состояние ожидания до тех пор, пока периферия станет готова, и затем завершает) цикл считывания.

8.8. См. табл. 8.2. В ходе машинного цикла извлечения

КОП сигналы управления 5о= ______ (0,1), S1= ______

(0,1) и![]() = ________ (0,1).

= ________ (0,1).

8.9. См. рис. 8.2. Перечислить выводы входов прерывания МП Intel 8085.

8.10. См. рис. 8.2. Выводы ВВ последовательных данных обозначены _______.

Решения

8.1. 8 бит. 8.2. Старших;

младших; мультиплексированную

(данных/адреса). 8.3. Мультиплексированной.

8.4. ALE. 8.5. +5 В. 8.6. Вы-

ходы

![]() имеют L-уровень, МП записывает в память.

Черта

сверху букв означает, что

L-сигнал на выходе

имеют L-уровень, МП записывает в память.

Черта

сверху букв означает, что

L-сигнал на выходе![]() активизирует па-

мять М, а на выходе

активизирует па-

мять М, а на выходе

![]() —

запись. 8.7. Переходит в состояние ожидания

и т.д. 8.8. S0=1, S1 = l,

—

запись. 8.7. Переходит в состояние ожидания

и т.д. 8.8. S0=1, S1 = l,![]() . 8.9. INTR, TRAP, RST7.5, RST6.5,

RST5.5. Но можно

рассматривать также сигнал RESET IN как

прерывание, так как он является причиной,

вызванной внешним устройством,

и

ветвит счетчик команд на новый адрес

программы. 8.10. SID и SOD.

. 8.9. INTR, TRAP, RST7.5, RST6.5,

RST5.5. Но можно

рассматривать также сигнал RESET IN как

прерывание, так как он является причиной,

вызванной внешним устройством,

и

ветвит счетчик команд на новый адрес

программы. 8.10. SID и SOD.