Микропроцессоры Токхайм / 7.3. ОСНОВНЫЕ ЭЛЕМЕНТЫ ИНТЕРФЕЙСА ПОРТОВ ВВОДА-ВЫВОДА

.doc7.3. ОСНОВНЫЕ ЭЛЕМЕНТЫ ИНТЕРФЕЙСА ПОРТОВ ВВОДА/ВЫВОДА

Операция ввода или вывода включает в себя передачу данных из (или) требуемой периферии. Микропроцессор является ядром всех операций. Ввод соответствует потоку данных в МП, вывод — из МП. Ячейки, куда данные входят или выходят, называются обычно портами ввода или вывода.

Согласно табл. 6.5 оказывается, что наш МП использует команды IN или OUT для передачи данных посредством портов ВВ. Реализация этих команд показана на рис. 7.9, а.

Мнемониками

являются IN и OUT для вводов и выводов

соответственно; рис. 7.9, а дает форматы

и КОП этих команд, которые соответствуют

номеру периферии или адресу порта. Адрес

порта (1 байт) позволяет выбрать один

из 256 (28) портов, и адрес передается

восемью адресными линиями младших

разрядов (А0—А7). На рис. 7.9, а представлены

также два дополнительных выхода сигналов

управления. При операции OUT используется

особый сигнал ВВ запись, т.е.

![]() ;

в случае операции IN — ВВ считывание,

т.е.

;

в случае операции IN — ВВ считывание,

т.е.

![]() .

Это два L-активных сигнала. Использование

специального управления, такого, как

.

Это два L-активных сигнала. Использование

специального управления, такого, как![]() и

и![]() ,

соответствует изолированному ВВ или

,

соответствует изолированному ВВ или

вводу/выводу через аккумулятор.

Передача данных, выполняемая на основе команд IN и OUT, классифицируется как программно-контролируемый ВВ, т.е. ею управляют команды программы. Передача данных может быть вызвана периферией, выдающей сообщение типа «Я готова выдать (или принять) данные». Чтобы вовлечь МП, периферия использует прерывания (вспомним, что когда МП получает запрос на прерывание, он завершает выполнение текущей команды, затем ветвится на подпрограмму обслуживания прерывания, эта подпрограмма может содержать или не содержать операции ВВ).

Программно-управляемый ВВ может быть выполнен двумя способами: первый — изолированный ВВ (см. рис. 7.9, а) выполняется посредством команд IN и OUT; по второму — положение входов и выходов определяется как адреса обычной памяти. Второй способ ВВ реализуется по принципу доступа в память, и тогда используются обычные команды. Обратимся к рис. 7.9, б, где мы использовали команду прямого размещения содержимого аккумулятора STA при выводе данных в порт вывода; на том же рисунке тот же тип команды использован затем и для ввода данных (команда LDA). Мы видим здесь, что адресные линии должны быть декодированы и служат для выбора адреса порта ввода или порта вывода.

Используются также

обычные сигналы управления![]() и

и![]() .

Таким образом, для ввода и вывода данных

по принципу доступа в память могут

быть использованы все команды обращения.

.

Таким образом, для ввода и вывода данных

по принципу доступа в память могут

быть использованы все команды обращения.

Последний способ, очевидно, наиболее распространен и может быть применим в любом МП. Метод изолированного ВВ применим только в МП, снабженных как командами IN и OUT, так и специальными выводами управления ВВ при записи и считывании.

Обычно под выводом подразумевают вывод на периферию. Однако на практике выводы попадают не сразу на периферию, а в устройство памяти, где помещаются данные для периферии (см. рис. 7.1, где мы ввели адаптеры интерфейса ввода и вывода, которые являются ни чем

иным, как устройствами памяти, и которые обладают всеми их свойствами).

На рис. 7.10, а

изображен интерфейс МП с периферией.

Отметим, что в качестве индикатора

выхода здесь стоит фотодиод, а адаптер

интерфейса вывода содержит D-триггер.

Предположим, что МП выполняет команду

прямого размещения содержимого

аккумулятора (Л) =0000 0001. Если предположить

также адрес 8000Н, то линия A15 будет

находиться в Н-активном состоянии и

активизирует нижний вход элемента И.

Некоторое время спустя Н-активный

сигнал появляется на линии D0 шины

данных. Сигнал управления записью![]() переходит к L-уровню и активизирует

элемент И, который запирает 1 в D-триггере.

На выходе D-триггера Н-сигналом зажигается

фотодиод (или индикатор бита). В качестве

примера на рис. 7.10, а показан процесс

индикации единственного бита данных.

переходит к L-уровню и активизирует

элемент И, который запирает 1 в D-триггере.

На выходе D-триггера Н-сигналом зажигается

фотодиод (или индикатор бита). В качестве

примера на рис. 7.10, а показан процесс

индикации единственного бита данных.

Интерфейс вывода на рис. 7.10,б несколько сложнее. Он передает 8 бит данных МП в адаптер интерфейса вывода через шину данных. Адаптер помещает данные в

8-разрядную защелку

обычным способом. Заметим, что адресная

линия A15 должна быть в Н-состоянии, тогда

как вывод управления записью![]() должен быть в L-состоянии в течение

времени, необходимого для того, чтобы

запереть данные в семисегментном

индикаторе. Каждый сегмент индикатора

(а—g и десятичная точка) работает так

же, как отдельный диод на рис. 7.10, а.

Запертый в любом выводе защелки Н-сигнал

вызывает свечение соответствующего

сегмента.

должен быть в L-состоянии в течение

времени, необходимого для того, чтобы

запереть данные в семисегментном

индикаторе. Каждый сегмент индикатора

(а—g и десятичная точка) работает так

же, как отдельный диод на рис. 7.10, а.

Запертый в любом выводе защелки Н-сигнал

вызывает свечение соответствующего

сегмента.

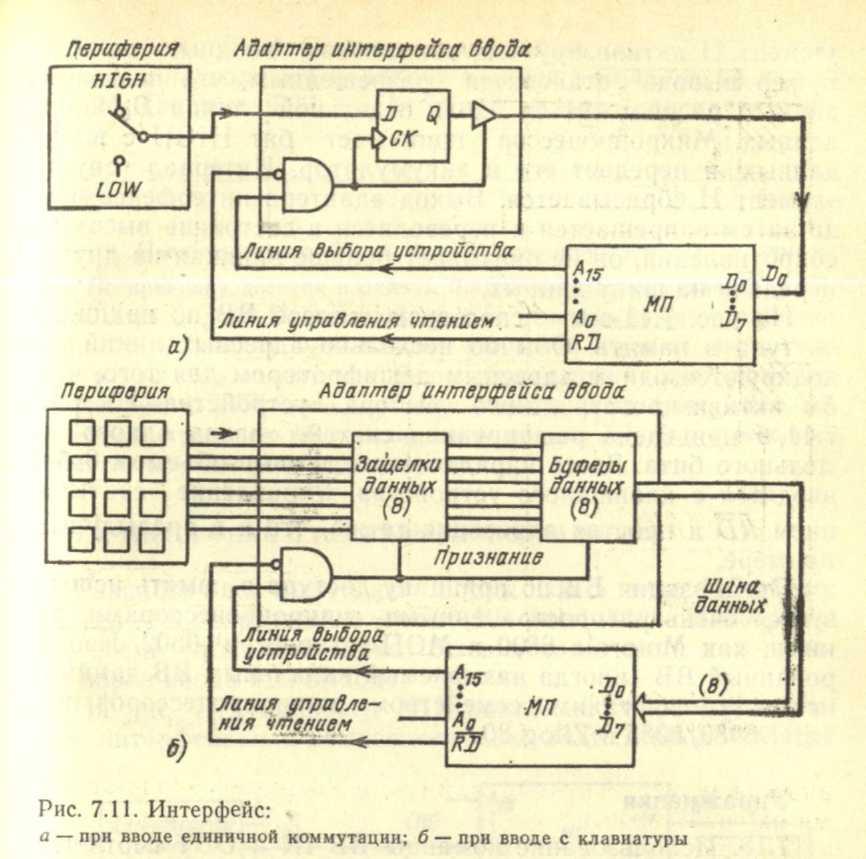

На рис. 7.11, а представлено другое периферийное устройство и его интерфейс с МП. Здесь речь идет о простом коммутаторе, позволяющем выбрать логический L- или Н-уровень. Отдельная линия данных соединена с вводом D-триггера внутри адаптера. Когда МП выполняет команду типа ЗАГРУЗИТЬ А прямо из ячейки памяти 8000Н,

На рис. 7.11 мы

используем способ ВВ по принципу доступа

в память. Обычно несколько адресных

линий декодируются одним адресным

дешифратором для того, чтобы

активизировать линию выбора устройства.

На рис. 7.11,б приведена расширенная

система ввода одного отдельного

бита. Здесь параллельные данные объемом

8 бит вводятся с клавишного устройства.

Управление считыванием![]() и

простая адресация те же, что и в предыдущем

примере.

и

простая адресация те же, что и в предыдущем

примере.

Организация ВВ по принципу доступа в память используется очень распространенными микропроцессорами, такими, как Motorola 6800 и МОП-технологии1 6502. Изолированный ВВ (иногда называемый канальным ВВ данных) используется таким семейством микропроцессоров, как Intel 8080/8085 и Zilog 80.

Упражнения

Использование команды ВВ 1N и OUT соответствует способу ______ (изолированного ВВ, ВВ по принципу доступна в память).

Способ, по которому УВВ обрабатывается, как обычные адреса памяти, называется ______.

Когда выводы

управления считыванием![]() соединяются с адаптером интерфейса

ВВ, используется способ _______.

соединяются с адаптером интерфейса

ВВ, используется способ _______.

См. рис. 7.11,б. Данные передаются в аккумулятор, после чего на адресную линию А15 поступает ________

(Н-, L-) сигнал, на линию управления считыванием поступает ________ (Н-, L-) сигнал, что в свою очередь разрешает защелки и триггеры.

7.22. См. рис. 7.11,б. В ходе операции ввода МП выполняет, вероятно, команду ____ (IN, OUT).

1 МОП — металл — окисел — полупроводник. — Прим. ред.

Когда буферы шины разрешены, они _____ (запрещают, позволяют) передачу данных с защелок на шину.

См. рис. 7.11,б. На какой адрес ответит интерфейс?

Решения

7.18. Изолированного

ВВ. 7.19. По принципу доступа в память.

7.20. По принципу доступа в память. 7.21.

Н-сигнал; на линии![]() устанавливается

L-. 7.22. По принципу доступа в память,

команда передачи LDA. 7.23. Позволяют. 7.24.

Каждый раз, когда адресная линия

старшего разряда А15 находится в

Н-состоянии, линия выбора устройства

активизируется. Этот метод адресации

непрактичен в случае, когда 32К памяти

(8 страниц по 4К каждая снизу на рис. 7.3)

будут использоваться только этим

устройством вывода.

устанавливается

L-. 7.22. По принципу доступа в память,

команда передачи LDA. 7.23. Позволяют. 7.24.

Каждый раз, когда адресная линия

старшего разряда А15 находится в

Н-состоянии, линия выбора устройства

активизируется. Этот метод адресации

непрактичен в случае, когда 32К памяти

(8 страниц по 4К каждая снизу на рис. 7.3)

будут использоваться только этим

устройством вывода.