Микропроцессоры Токхайм / 7.1. ИНТЕРФЕЙС С ПЗУ

.docГлава 7

ИНТЕРФЕЙС МИКРОПРОЦЕССОРА

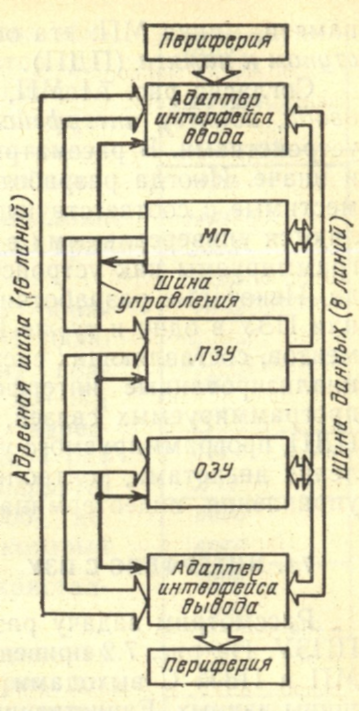

Большинство микропроцессоров сами по себе функционально ограничены. Большая часть из них содержит память и немногие порты ввода/вывода, которые напрямую соединяют их с периферией. Микропроцессоры функционируют как элементы системы. Соединения между элементами внутри системы составляют интерфейс. Обычно интерфейс является общей границей между двумя или несколькими устройствами, т.е. тем, что влечет за собой раздел информации Среди прочих свойств интерфейса отметим

1 Согласно [1] под интерфейсом понимается: совокупность унифицированных технических и программных средств, необходимых для подключения данных устройств к системе или одной системы к другой. — Прим. ред.

![]()

решение им задач синхронизации, выбора направления передачи данных и иногда приведения в соответствие уровней или форм сигналов.

Рассмотрим схему простой системы на рис. 7.1. Мы будем изучать интерфейс (или взаимные присоединения) между каждым из показанных устройств и МП; подробно рассмотрим также интерфейс МП с ПЗУ, ОЗУ и УВВ; приведем подробную информацию о некоторых периферийных устройствах Согласно рис. 7.1 очевидно, что шины адресов, данных и управления играют важную роль во взаимных связях элементов системы, и, следовательно, нас будут интересовать как аппаратные, так и программные средства.

Обычно передача данных от и в МП через шины осуществляется в следующих формах:

1. Считывание из памяти.

Запись в память.

Считывание из УВВ.

Запись в УВВ.

5. Управление прерыванием или сбросом.

Когда говорят, что данные введены с другого устройства, это означает вступить в отношения с МП. Аналогично вывод данных — это уход из МП. Обычно МП является ядром всех операций. Однако некоторые МП оставляют на время управление шинами данных и адресов, чтобы периферийное устройство могло получить доступ к центральной

1 Периферийное устройство [1] —устройство, входящее в состав внешнего оборудования микро-ЭВМ, обеспечивающего ввод и вывод данных, организацию промежуточного и длительного хранения данных. — Прим. ред.

памяти, минуя МП: эта операция называется прямым доступом к памяти (ПДП).

Согласно рис. 7.1 МП, ПЗУ, ОЗУ, адаптер интерфейса ввода, адаптер интерфейса вывода являются различными устройствами. В рассматриваемой системе это может быть и иначе. Иногда разработчики создают интерфейсы, совместимые с соответствующими устройствами МП. Они являются универсальными в том смысле, что могут быть программируемы как устройства интерфейса ввода или вывода. Некоторые разработчики встраивают ОЗУ и порты ВВ или ПЗУ в одну и ту же ИС с целью снижения числа элементов, составляющих систему. Они производят также специализированные интерфейсы в форме ИС: интерфейсы программируемых связей, программируемого управления ПДП, программируемого управления прерываниями, управления дискетами, контролерами связи синхронных данных, управления видеотерминалом и клавишным устройством.

7.1. ИНТЕРФЕЙС С ПЗУ

Рассмотрим задачу

разработки интерфейса с ПЗУ или ППЗУ.

На рис. 7.2 приведена часть системы,

включающая МП и ПЗУ. С выходами О0—O7

ПЗУ соединены 8 линий шины данных.

Единственный выход управления

считыванием![]() идет

из МП на вход активизации

идет

из МП на вход активизации![]() ПЗУ.

ПЗУ.

С постоянным запоминающим устройством емкостью 4 Кбайт соединены 12 линий адресной шины младших разрядов (A0—А11). Дешифратор, встроенный в ИС ПЗУ, может получить доступ к любому из 4096 (212=4096) 8-разрядных слов ПЗУ. Адресные линии четырех старших раз-

рядов (A 11—A 15) идут

в устройство комбинированной логики

— дешифратор адреса. Для доступа в

ПЗУ и считывания из него данных МП

должен: активизировать линии адреса

A0—А11; установить L-сигнал на линии

управления считыванием![]() ; установить L-сигнал на линии дешифратора

адреса и выбора кристалла.

; установить L-сигнал на линии дешифратора

адреса и выбора кристалла.

Предположим, что МП нужно обратиться в память по адресу 0000Н (0000 0000 0000 00002). Младших 12 бит подключаются по адресным линиям A0—А 11 к контуру дешифратора ПЗУ. К адресным принадлежат также старших 4 бит A12—A15. Они декодируются дешифратором адреса. Если (A12—A15) =00002, дешифратор адреса выдает сигнал, который

активизирует

вход![]() выбора

кристалла ПЗУ (рис. 7.2).

выбора

кристалла ПЗУ (рис. 7.2).

Воображаемая память, приведенная на рис. 7.3, может помочь понять роль дешифратора адреса. Она представляет собой устройство емкостью 64К (т.е. 65 536 ячеек памяти), разделенное на 16 сегментов по 4 К каждый. Роль дешифратора адреса состоит в том, чтобы обеспечить МП доступ только к одному из этих сегментов одновременно. Если имеется четыре входа в дешифратор 0000, то доступным будет нулевой сегмент (пространство памяти 0000—0FFFH). Если на этих входах 0001, доступен первый сегмент (пространство памяти 1000— 1FFFH) и т.д. Таким образом, старших 4 бит (передающих линии) выбирают сегмент памяти, а младших 12 бит определяют нужную ячейку памяти в этом сегменте.

В интерфейсе с ПЗУ важное значение имеют способы адресации и синхронизации. Адресацию мы сейчас рассмотрели, обратимся теперь к синхронизации.

На рис. 7.4 приведена временная диаграмма сигналов МП, управляющих считыванием 8-разрядного слова из ПЗУ.

Верхняя линия диаграммы представляет переход адресных линий A0—А15 на их соответствующий логический уровень. Согласно рис. 7.2 адресные линии A0—A11 активизируют адресные входы ПЗУ, тогда как адресные линии A12—A15 декодируются дешифратором адреса и активизируют вход CS выбора кристалла ПЗУ. Спустя некоторое время выход управления считыванием RD МП активизирует процесс вывода данных из ПЗУ. Расположенные здесь данные помещаются на шину данных и принимаются МП.

На рис. 7.4 показаны критические ограничения синхронизации. После того как на адресных линиях установился

соответствующий

логический уровень и активизировался

вход![]() ПЗУ,

нужен определенный отрезок времени

для извлечения слова данных. Это время

необходимо внутренним дешифраторам

ПЗУ для нахождения требуемого байта

в памяти.

ПЗУ,

нужен определенный отрезок времени

для извлечения слова данных. Это время

необходимо внутренним дешифраторам

ПЗУ для нахождения требуемого байта

в памяти.

Обратим внимание

на использование на рис. 7.4 кружков

и стрелок. Эти индикаторы используются

для обозначения соотношений причины

и следствия на временной диаграмме.

В качестве примера на рис. 7.4 переход

от Н- к L-уровню (от HIGH к LOW) на выходе

считывания осуществит переключение

тристабильных выводов шины данных МП

из состояния высокого сопротивления

для приема данных на входе. Штриховая

часть временной диаграммы по линии

ввода соответствует состоянию высокого

сопротивления. При переходе от L- к

Н-уровню выхода![]() выводы

шины данных МП снова переключатся в

третье состояние и не примут данные с

шины. Временная диаграмма на рис. 7.4

представляет собой только сигналы МП

и не содержит сигналов входа и выхода

ПЗУ.

выводы

шины данных МП снова переключатся в

третье состояние и не примут данные с

шины. Временная диаграмма на рис. 7.4

представляет собой только сигналы МП

и не содержит сигналов входа и выхода

ПЗУ.

Упражнения

Постоянное запоминающее устройство на рис. 7.2 может содержать ____ слов емкостью _____ бит каждое.

Постоянное запоминающее устройство емкостью 4 К требует _______ адресных входов для декодирования адресов 4096 содержащихся в нем ячеек памяти.

7.3. См. рис. 7.2. Дешифратором ________ (адреса, ПЗУ)

декодируются четыре старшие линии.

См. рис. 7.3. Какой сегмент памяти будет доступен, если МП выдает 0010 0000 0000 11112 на адресную шину?

См. рис. 7.4. В ходе

считывания из памяти последней будет

активизироваться линия МП ________ (A0—A15,![]() ).

).

Когда сигнал на

выходе![]() МП

переходит к L-уровню, он активизирует

вход

МП

переходит к L-уровню, он активизирует

вход ![]() ______

ПЗУ и приводит

______

ПЗУ и приводит

выводы шины данных МП в состояние _______(приема данных с шины, отказа от данных с шины, исходя из условия трех состояний).

7.7. Оценка ПЗУ, относящаяся к необходимому времени декодирования адреса и доступа в память по заданному адресу, составляет время ________.

Решения

7.1. 4096 (4К); 8. 7.2. 12.

7.3. Адреса. Это линии (A12—A15). 7.4.

00102 =

2ю, сегмент 2, содержащий 4096 ячеек памяти

с адресами от

2000Н до 2FFFH. 7.5.![]() . 7.6.

. 7.6.![]() ; приема данных с шин. 7.7. Доступа

к

чтению в ПЗУ.

; приема данных с шин. 7.7. Доступа

к

чтению в ПЗУ.