- •Комп’ютерна електроніка

- •1 Вступ

- •2 Дискретизація аналогових сигналів

- •2.1 Квантування за рівнем

- •2.2 Квантування за часом

- •2.3 Квантування за рівнем і за часом

- •2.3.1 Розмір похибки ацп

- •2.3.2 Вибір величини кроку квантування за часом

- •3 Застосування алгебри логіки (булевої алгебри) при аналізі і синтезі цифрових електронних пристроїв

- •3.1 Визначення і способи задання перемикальних функцій

- •3.4 Базисні логічні функції

- •3.5 Принцип двоїстості булевої алгебри

- •3.6 Основні тотожності булевої алгебри

- •3.7 Основні закони булевої алгебри

- •3.8 Досконала диз’юнктивна нормальна форма (дднф) запису булевих виразів

- •3.9 Диз’юнктивна нормальна форма

- •3.10 Досконала кон’юнктивна нормальна форма (дкнф) запису булевих виразів

- •3.11 Кон’юнктивна нормальна форма (кнф)

- •3.12 Мінімізація логічних функцій

- •3.12.1 Алгебраїчний спосіб мінімізації пф

- •3.12.2 Мінімізація пф із використанням діаграм Вейча (карт Карно)

- •3.12.2.1 Мінімізація пф за допомогою діаграм Вейча

- •3.12.2.1.1 Загальне правило мінімізації

- •3.12.2.1.2 Приклади мінімізації пф за допомогою діаграм Вейча

- •3.12.2.2 Мінімізація пф за допомогою карт Карно

- •4 Логічні елементи

- •4.1 Інвертор (логічний елемент ні)

- •4.2 Кон’юнктор (логічний елемент і)

- •4.3 Диз’юнктор (логічний елемент або)

- •4.4 Повторювач

- •4.7 Виключаюче або

- •4.8 Додавання по модулю два (непарність)

- •4.9 Додавання по модулю два з запереченням (парність)

- •4.10 Еквівалентність

- •4.11 Нееквівалентність

- •4.13 Заборона

- •4.14 Логічні елементи з відкритим колектором

- •4.15 Логічні елементи з третім станом

- •5 Реалізація логічних функцій у різних базисах

- •5.1 Базисні набори ле і їх взаємозв'язок

- •5.2 Реалізація логічних функцій у різноманітних базисах

- •5.2.1 Реалізація елемента “Рівнозначність” (виключаюче або - ні)

- •5.2.2 Реалізація елемента “нерівнозначність” (виключаюче або, сума по модулю два)

- •5.2.3 Реалізація елемента “Заборона”

- •5.2.4 Реалізація багатолітерних логічних функцій на елементах з невеликою кількістю входів

- •6 Параметри і характеристики цифрових інтегральних мікросхем (імс)

- •6.1 Коефіцієнт об'єднання по входу (Коб)

- •6.2 Коефіцієнт розгалуження по виходу (Кроз)

- •6.3 Статичні характеристики

- •6.4 Завадостійкість

- •6.5 Динамічні характеристики і параметри

- •6.6 Вигляд реалізованої логічної функції

- •6.7 Споживані струм і потужність

- •6.8 Вхідні і вихідні струми, напруги

- •6.9 Порогові напруги

- •6.10 Допустимі значення основних параметрів

- •7 Базові логічні елементи

- •7.1 Базовий ттл (ттлш) - елемент і - ні

- •7.2 Базовий езл - елемент або/або-ні

- •7.3 Базовий кмон елемент або-ні

- •8 Генератори тактових імпульсів (гті) на логічних елементах

- •8.1 Гті на двох інверторах

- •8.2 Гті на 3-х інверторах.

4.13 Заборона

Елемент реалізує логічну функцію

__

F = A. B . (4.13)

Нижче показані його позначення на електричних схемах (рисунок 4.14) і таблиця істинності (таблиця 4.12).

-

Рисунок 4.14

Таблиця 4.12

-

N набору

В

А

F

0

0

0

0

1

0

1

1

2

1

0

0

3

1

1

0

На виході такого елемента логічна одиниця буде лише в тому випадку, якщо на основному вході - логічна одиниця (А=1), а на вході , що забороняє - нуль (В=0).

В позначенні елемента на електричних схемах вхід, що забороняє, позначений як інверсний - кругом. Сигналом, що забороняє на цьому вході, буде логічна одиниця.

4.14 Логічні елементи з відкритим колектором

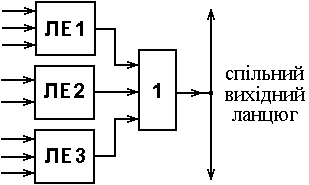

При побудові цифрових пристроїв часто виникає необхідність об'єднання виходів декількох логічних елементів з метою переходу на спільний вихідний ланцюг. Цю задачу можна вирішити за допомогою елемента АБО (рисунок 4.15).

-

Рисунок 4.15

При цьому доводиться миритися з додатковими схемними витратами і збільшенням сумарної затримки проходження цифрових сигналів через пристрій.

Інший

спосіб заснований на застосуванні

логічних елементів з відкритим колектором,

у полі

функціонального позначення яких є

спеціальний

символ

![]() ,

що вказує, що колектор вихідного

транзистора відкритий (обірваний,

“висить у повітрі”).

,

що вказує, що колектор вихідного

транзистора відкритий (обірваний,

“висить у повітрі”).

На рисунку 4.16 показане об'єднання декількох логічних елементів із відкритим колектором на спільний вихід.

-

Рисунок 4.16

Для нульових сигналів на виході логічних елементів ЛЕ1...ЛЕ3 (відповідний транзистор відкритий) подана схема виконує функцію “монтажне АБО”: якщо з'явиляється логічний нуль хоча б на одному із виходів логічних елементів, вихідний сигнал також буде дорівнювати нулю.

Для одиничних сигналів на виходах логічних елементів ЛЕ1...ЛЕ3 (відповідний транзистор закритий) схема виконує функцію “монтажне I”: вихідний сигнал схеми дорівнює одиниці лише при одночасній появі логічних одиниць на виходах усіх логічних елементів.

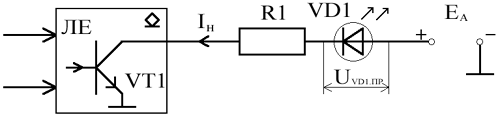

Елементи з відкритим колектором мають більш високу навантажувальну спроможність, нiж звичайні ЛЕ, тому можуть використовуватися для підключення навантажень типу тиристорів, реле, індикаторів (світлодіодів) і т.п. (рисунок 4.17).

-

Рисунок 4.17

При цьому необхідно забезпечити виконання умови:

![]() ,

(4.14)

,

(4.14)

де

Iн

- струм

навантаження;

![]() -

значення максимального

струму,

що може протікати через відкритий

вихідний транзистор логічного елемента.

-

значення максимального

струму,

що може протікати через відкритий

вихідний транзистор логічного елемента.

На рисунку 4.18 наведений приклад підключення до ЛЕ з відкритим колектором світлодіода VD1.

Рисунок

4.18

Рисунок

4.18

Коли на виході логічного елементу з’являється логічний 0 (вихідний транзистор VT1 відкритий), світлодіод буде підключений до джерела струму EA у прямому напрямку. Коли через світлодіод VD1 протікає прямий струм, він засвічується. Струм IН дорівнює струму засвічування світлодіода, який складає: Iзасв. VD1≤20мА. Падіння напруги на відкритому діоді UVD1.ПР складає: (1,7...2) В. Резистор R1 обмежує величину прямого струму і обчислюється за формулою:

![]() .

(4.15)

.

(4.15)

Наприклад, EA= 5 В, UVD1.ПР = 2 В, Iзасв. VD1 = 20 мА.

Тоді

![]() Ом.

Ом.