- •Комп’ютерна електроніка

- •1 Вступ

- •2 Дискретизація аналогових сигналів

- •2.1 Квантування за рівнем

- •2.2 Квантування за часом

- •2.3 Квантування за рівнем і за часом

- •2.3.1 Розмір похибки ацп

- •2.3.2 Вибір величини кроку квантування за часом

- •3 Застосування алгебри логіки (булевої алгебри) при аналізі і синтезі цифрових електронних пристроїв

- •3.1 Визначення і способи задання перемикальних функцій

- •3.4 Базисні логічні функції

- •3.5 Принцип двоїстості булевої алгебри

- •3.6 Основні тотожності булевої алгебри

- •3.7 Основні закони булевої алгебри

- •3.8 Досконала диз’юнктивна нормальна форма (дднф) запису булевих виразів

- •3.9 Диз’юнктивна нормальна форма

- •3.10 Досконала кон’юнктивна нормальна форма (дкнф) запису булевих виразів

- •3.11 Кон’юнктивна нормальна форма (кнф)

- •3.12 Мінімізація логічних функцій

- •3.12.1 Алгебраїчний спосіб мінімізації пф

- •3.12.2 Мінімізація пф із використанням діаграм Вейча (карт Карно)

- •3.12.2.1 Мінімізація пф за допомогою діаграм Вейча

- •3.12.2.1.1 Загальне правило мінімізації

- •3.12.2.1.2 Приклади мінімізації пф за допомогою діаграм Вейча

- •3.12.2.2 Мінімізація пф за допомогою карт Карно

- •4 Логічні елементи

- •4.1 Інвертор (логічний елемент ні)

- •4.2 Кон’юнктор (логічний елемент і)

- •4.3 Диз’юнктор (логічний елемент або)

- •4.4 Повторювач

- •4.7 Виключаюче або

- •4.8 Додавання по модулю два (непарність)

- •4.9 Додавання по модулю два з запереченням (парність)

- •4.10 Еквівалентність

- •4.11 Нееквівалентність

- •4.13 Заборона

- •4.14 Логічні елементи з відкритим колектором

- •4.15 Логічні елементи з третім станом

- •5 Реалізація логічних функцій у різних базисах

- •5.1 Базисні набори ле і їх взаємозв'язок

- •5.2 Реалізація логічних функцій у різноманітних базисах

- •5.2.1 Реалізація елемента “Рівнозначність” (виключаюче або - ні)

- •5.2.2 Реалізація елемента “нерівнозначність” (виключаюче або, сума по модулю два)

- •5.2.3 Реалізація елемента “Заборона”

- •5.2.4 Реалізація багатолітерних логічних функцій на елементах з невеликою кількістю входів

- •6 Параметри і характеристики цифрових інтегральних мікросхем (імс)

- •6.1 Коефіцієнт об'єднання по входу (Коб)

- •6.2 Коефіцієнт розгалуження по виходу (Кроз)

- •6.3 Статичні характеристики

- •6.4 Завадостійкість

- •6.5 Динамічні характеристики і параметри

- •6.6 Вигляд реалізованої логічної функції

- •6.7 Споживані струм і потужність

- •6.8 Вхідні і вихідні струми, напруги

- •6.9 Порогові напруги

- •6.10 Допустимі значення основних параметрів

- •7 Базові логічні елементи

- •7.1 Базовий ттл (ттлш) - елемент і - ні

- •7.2 Базовий езл - елемент або/або-ні

- •7.3 Базовий кмон елемент або-ні

- •8 Генератори тактових імпульсів (гті) на логічних елементах

- •8.1 Гті на двох інверторах

- •8.2 Гті на 3-х інверторах.

- •9 Функціональні пристроїкомп'ютерної (цифрової) електроніки

- •9.1 Комбінаційні цифрові пристрої (кцп)

- •9.1.1 Аналіз і синтез кцп

- •9.1.1.1 Аналіз кцп

- •9.1.1.2 Синтез кцп

- •9.1.2 Типові кцп

- •9.1.2.1 Шифратори та дешифратори

- •9.1.2.1.1 Шифратори двійкового коду

- •9.1.2.1.2 Шифратори двійково-десяткового коду

- •9.1.2.1.3 Дешифратори двійкового коду

- •9.1.2.1.4 Дешифратор bcd - коду всемисегментний код

- •9.1.2.1.4.1 Семисегментні індикатори на світлодіодах

- •9.1.2.2 Мультиплексори й демультиплексори

- •9.1.2.2.1 Мультиплексори

- •9.1.2.2.2 Демультиплексори

- •9.1.2.2.3 Мультиплексори-селектори (мультиплексори-демультиплексори)

- •9.1.2.3 Cуматори і напівсуматори

- •9.1.2.4 Пристрої контролю парності (пкп)

- •9.1.2.5 Цифрові компаратори

- •9.1.3 Використання для проектування кцп мультиплексорів, дешифраторів і постійного запам’ятовуючого пристрою

- •9.1.3.1 Побудова кцп на мультиплексорах

- •9.1.3.2 Побудова кцп на дешифраторах

- •9.1.3.3 Побудова кцп на постійному запам’ятовуючому пристрої (пзп)

- •9.2 Послідовні цифрові пристрої

- •9.2.1 Тригери

- •9.2.1.1 Тригери на логічних елементах

- •9.2.1.1.1 Rs - тригери

- •9.2.1.1.1.1 Асинхронні rs - тригери

- •9.2.1.1.1.2 Синхронні rs - тригери

- •9.2.1.1.2 Т-тригери (тригери з лічильним входом)

- •9.2.1.1.3 D - тригери (тригери затримки)

- •9.2.1.1.4 Jk - тригери

- •9.2.1.2 Тригери у інтегральному виконанні

- •9.2.2 Регістри

- •9.2.2.1 Паралельні регістри

- •9.2.2.2 Послідовні (зсуваючі) регістри

- •9.2.2.3 Регістри зсуву

- •9.2.2.4 Послідовно-паралельні і паралельно-послідовні регістри

- •9.2.2.5 Регістри у інтегральному виконанні

- •9.2.3 Лічильники

- •9.2.3.1 Асинхронний двійковий лічильник, що підсумовує, з послідовним перенесенням

- •9.2.3.2 Асинхронний двійковий лічильник, що віднімає, із послідовним перенесенням

- •9.2.3.3 Асинхронні реверсивні двійкові лічильники з послідовним перенесенням

- •9.2.3.4 Синхронний лічильник з наскрізним перенесенням

- •9.2.3.5 Десяткові лічильники

- •9.2.3.6 Лічильники в інтегральному виконанні

- •9.2.4 Подільники частоти

- •9.2.5 Розподілювачі

- •10 Зв'язок мп-ра і омеом з аналоговим об'єктом управління і з пк

- •10.1 Структура типової локальної мікропроцесорної системи управління (лмпсу)

- •10.1.1 Призначення і схемна реалізація окремих вузлів лмпсу

- •10.1.1.1 Аналоговий мультиплексор (ампс)

- •10.1.1.2 Пристрій вибірки-зберігання (пвз)

- •10.1.1.3 Аналого-цифровий перетворювач (ацп)

- •10.1.1.4 Ведена однокристальна мікроЕом (омеом)

- •10.1.1.5 Шинний формувач (шф)

- •10.1.1.6 Регістри (Рг1...Рг3)

- •10.1.1.7 Схеми узгодження рівнів (сур1...Сур3)

- •10.1.1.8 Цифро-аналогові перетворювачі (цап1...Цап3)

- •10.2 Застосування ацп і пвз при введенні аналогової інформації в мпс

- •10.2.1 Розрахунок ацп

- •10.2.2.1 Опис мікросхеми к1113 пв1

- •10.2.2.2 Розрахунок мікросхеми к1113 пв1

- •10.2.2.3 Введення даних від ацп в мпс через ппі в режимі 0

- •10.2.3 Пристрій вибірки і зберігання (пвз)

- •10.2.3.1 Обґрунтування застосування пвз

- •10.2.3.2 Принцип дії, схема й основні параметри пвз

- •Р Рисунок 10.17исунок 10.17

- •10.2.3.3 Функціональні можливості і схема включення мікросхеми пвз к1100ск2 (кр 1100ск2)

- •10.2.4.1Опис мікросхеми max154. Часові діаграми і режими роботи

- •10.2.4.1.1 Опис роботи паралельного 4-х розрядного ацп

- •10.2.4.2 Розрахунок ацп max154

- •10.3 Застосування цап прививодіцифрової інформації з мпс

- •10.3.1 РозрахунокЦап на матриці r-2Rзпідсумовуваннямструмів

- •10.3.2.1 Опис мікросхеми к 572 па1

- •10.3.2.2 Розрахунок цап к 572 па1

- •10.3.3.1 Опис мікросхеми max506

- •10.3.3.2 Розрахунок цап max506

- •10.4 Особливості апаратної і програмної реалізації модуля ацп- цап мпс

- •10.4.1 Апаратний рівень

- •10.4.2 Програмний рівень

- •10.5 Обмін між мп-м (омеом) і пк по послідовному каналузв'язку за допомогою інтерфейсу rs-232с

- •10.5.1 Універсальний асинхронний послідовний програмований приймач – передавач (уапп)

- •10.5.2 Пристрій перетворення рівнів (ппр)

- •10.5.4 Буферний регістр адреси rs– 232с

- •10.5.5 Шинний формувач

- •10.6 Вибір і розрахунок датчиків, нормуючих перетворювачів і фільтрів нижніх частот (фнч)

- •10.6.1 Вибір і розрахунок датчиків і нормуючих перетворювачів

- •10.6.1.1 Вибір датчиків

- •10.6.1.2 Вибір і розрахунок нормуючих перетворювачів

- •10.6.3 Розрахунок фнч

- •10.7 Розробка схеми алгоритму і керуючої програми

- •11 Список літератури

10.6.3 Розрахунок фнч

Вихідні дані для розрахунку:

АЧХ ФНЧ повинна бути монотонною в смузі пропускання і смузі затримки.

Коефіцієнт підсилення К=1.

Частота зрізу fз=10Гц.

Максимальне загасання в смузі пропускання

1=3дБ.

1=3дБ.Мінімальне загасання в смузі затримування

2=20дБ.

2=20дБ.Ширина перехідної області Тwнч = 10Гц.

Ці дані були введені в програму розрахунку фільтра, яка визначила, що заданим значенням задовольняє фільтр Баттерворта 4-го порядку. Його принципова схема показана на рисунку 10.55 і включає дві ланки 2-го порядку, які реалізовані на ІМС ОП: DA1,DA2.

Р озрахунковий

порядок фільтра = 4.

озрахунковий

порядок фільтра = 4.

Добротність: ланка1 = 0.541196, ланка2 = 1.306563

Значення елементів :

ланка1: R1 =34,8кОм; R2 = 34,8кОм; R3 = 1,74 кОм ;

С1 = 422нФ; С2 = 1мкФ;

ланка2: R4 = 82,5кОм; R5 = 82,5кОм; R6 = 41,2кОм ;C3 = 73,2нФ;

C4 = 1 мкФ.

На рисунку 10.56 наведені характеристики: окремих ланок ФНЧ; АЧХ ідеального ФНЧ, що відповідає розрахунковим значенням його компонентів без їхнього округлення; АЧХ реального ФНЧ, що відповідає реальним значенням компонентів схеми, отриманим після їхнього округлення до конкретного стандартного ряду електронних елементів Е96.

10.7 Розробка схеми алгоритму і керуючої програми

Невід'ємною частиною будь-якої мікропроцесорної системи є керуюча програма, що забезпечує виконання системою заданих функцій.

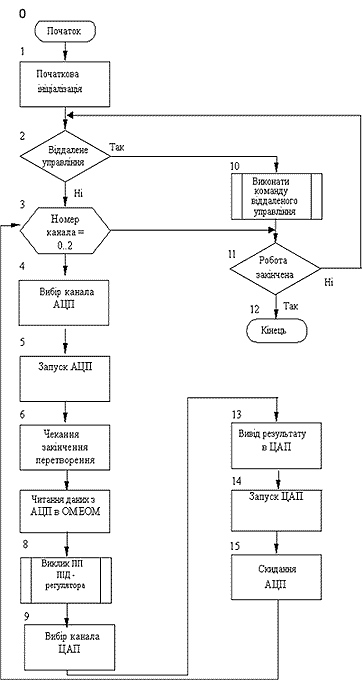

На рисунку 10.57 наведена схема алгоритму роботи ЛМПСУ, структура якої показана на рисунку 10.1.

|

|

|

Рисунок 10.57 – Схема алгоритму роботи ЛМПСУ |

Потім обробляється перший (індекс 0) канал триканальної системи збору, обробки інформації і керування. Це відбувається в тому випадку, якщо відсутнє переривання від встановлення прапорця RI=1 веденої ОМЕОМ (вхідний буфер приймача послідовного каналу повний). RI=0 відбиває відсутність необхідності віддаленого керування, що полягає в одержанні веденою ОМЕОМ команди від мікроЕОМ більш високої ступені ієрархії. Значення контрольованого параметру 1-го каналу (у нашому випадку – витрата газу) через аналоговий мультиплексор і пристрій вибірки-зберігання, вбудовані в мікросхему MAX154, надійде на вхід АЦП цієї мікросхеми.

Потім формується сигнал запуску АЦП, очікується закінчення перетворення і після його завершення інформація про поточне значення контрольованого параметру вводиться в ОМЕОМ. Тут це значення порівнюється з заданим, у результаті чого виробляється сигнал непогодження, що надходить на цифровий ПІД-регулятор, реалізований програмно, і призначений для забезпечення необхідної якості процесу керування.

З

виходу регулятора знімається керуючий

вплив, що через паралельний

порт ОМЕОМ виводиться сигналом

![]() - запис у попередньо обраний регістр –

клямку

чотирьохканального

ЦАП MAX506.

- запис у попередньо обраний регістр –

клямку

чотирьохканального

ЦАП MAX506.

Цифрове значення, збережене в регістрі, безпосередньо цифро-аналоговим перетворювачем, який виконаний на матриці R-2R і операційному підсилювачі, перетворюється в аналогову величину – напругу, яка видається на відповідний виконавчий елемент.

Після завершення обробки першого каналу формується сигнал скидання для АЦП і аналогічно обробляються другий канал – виміру тиску, а потім, третій – виміру температури.

Якщо після цього робота системи не завершена, то керування знову передається обробці 1-го каналу і т.д.

Якщо перед черговим циклом обробки з'являється сигнал необхідності віддаленого управління, то основна програма переривається і керування передається підпрограмі, що здійснює взаємодію з мікро ЕОМ більш високого рівня.

Робоча керуюча програма, що реалізує даний алгоритм мовою Ассемблер ОМЕОМ МК51 приведена в таблиці 10.7.

Таблиця 10.7 – Робоча керуюча програма

|

Блок |

Мітка |

Команда |

Коментар |

|

1 |

|

SETB P2.6 |

Подача високого рівня на WR |

|

2 |

MAIN: |

JB P3.2, REMCONTROL |

Перехід до підпрограми віддаленого керування при наявності сигналу ВУ |

|

3 |

|

MOV R0, 0 |

Установка початкового каналу контролю |

|

4 |

LOOP: |

MOV A, P2 AND A, #11111100b OR A, R0 MOV P2, A |

Читання інформації з порту P2 Маскування бітів номера каналу АЦП Запис номера каналу Вивід номера каналу в порт P2 |

|

5 |

|

CLR P2.2 |

Подача низького рівня на CS, RD |

|

6 |

|

NOP NOP |

Затримка для закінчення перетворення АЦП |

Продовження таблиці 10.7

|

7 |

|

MOV A, P1 |

Читання даних з АЦП |

|

8 |

|

ACALL REG_PROC MOV R1, A |

Виклик підпрограми ПІД – регулятора. ПП повертає результат в акумуляторі |

|

9 |

|

MOV A, R0 MOV C, ACC.0 MOV P2.4, C MOV C, ACC.1 MOV P2.5, C SJMP CONTINUE: |

Завантаження номера каналу в акумулятор Побітовий вивід номера каналу в ЦАП

|

|

10 |

REMCONTROL: |

|

Виконання команди віддаленого керування |

|

11 |

CHECKEXIT: |

JNB P3.5, MAIN |

Перехід до початку програми |

|

12 |

|

RET |

Вихід із програми |

|

13 |

CONTINUE: |

MOV A, R1 MOV P0, A |

Завантаження сигналу керування в акумулятор Вивід сигналу керування в ЦАП |

|

14 |

|

CLR P2.6 SETB P2.6 |

Подача переходу 0->1 на ЦАП (запуск) |

|

15 |

|

SETB P2.2 |

Подача високого рівня на CS, RD |

|

3 |

|

INC R0 CJNE A, #3, LOOP SJMP CHECKEXIT |

Перехід до наступного каналу Виконати для 0..2 канали Перехід до наступної ітерації |

На рисунку 10.58 зображена схема електрична принципова ЛМПСУ, що реалізує задачу, яка описана вище.