- •Комп’ютерна електроніка

- •1 Вступ

- •2 Дискретизація аналогових сигналів

- •2.1 Квантування за рівнем

- •2.2 Квантування за часом

- •2.3 Квантування за рівнем і за часом

- •2.3.1 Розмір похибки ацп

- •2.3.2 Вибір величини кроку квантування за часом

- •3 Застосування алгебри логіки (булевої алгебри) при аналізі і синтезі цифрових електронних пристроїв

- •3.1 Визначення і способи задання перемикальних функцій

- •3.4 Базисні логічні функції

- •3.5 Принцип двоїстості булевої алгебри

- •3.6 Основні тотожності булевої алгебри

- •3.7 Основні закони булевої алгебри

- •3.8 Досконала диз’юнктивна нормальна форма (дднф) запису булевих виразів

- •3.9 Диз’юнктивна нормальна форма

- •3.10 Досконала кон’юнктивна нормальна форма (дкнф) запису булевих виразів

- •3.11 Кон’юнктивна нормальна форма (кнф)

- •3.12 Мінімізація логічних функцій

- •3.12.1 Алгебраїчний спосіб мінімізації пф

- •3.12.2 Мінімізація пф із використанням діаграм Вейча (карт Карно)

- •3.12.2.1 Мінімізація пф за допомогою діаграм Вейча

- •3.12.2.1.1 Загальне правило мінімізації

- •3.12.2.1.2 Приклади мінімізації пф за допомогою діаграм Вейча

- •3.12.2.2 Мінімізація пф за допомогою карт Карно

- •4 Логічні елементи

- •4.1 Інвертор (логічний елемент ні)

- •4.2 Кон’юнктор (логічний елемент і)

- •4.3 Диз’юнктор (логічний елемент або)

- •4.4 Повторювач

- •4.7 Виключаюче або

- •4.8 Додавання по модулю два (непарність)

- •4.9 Додавання по модулю два з запереченням (парність)

- •4.10 Еквівалентність

- •4.11 Нееквівалентність

- •4.13 Заборона

- •4.14 Логічні елементи з відкритим колектором

- •4.15 Логічні елементи з третім станом

- •5 Реалізація логічних функцій у різних базисах

- •5.1 Базисні набори ле і їх взаємозв'язок

- •5.2 Реалізація логічних функцій у різноманітних базисах

- •5.2.1 Реалізація елемента “Рівнозначність” (виключаюче або - ні)

- •5.2.2 Реалізація елемента “нерівнозначність” (виключаюче або, сума по модулю два)

- •5.2.3 Реалізація елемента “Заборона”

- •5.2.4 Реалізація багатолітерних логічних функцій на елементах з невеликою кількістю входів

- •6 Параметри і характеристики цифрових інтегральних мікросхем (імс)

- •6.1 Коефіцієнт об'єднання по входу (Коб)

- •6.2 Коефіцієнт розгалуження по виходу (Кроз)

- •6.3 Статичні характеристики

- •6.4 Завадостійкість

- •6.5 Динамічні характеристики і параметри

- •6.6 Вигляд реалізованої логічної функції

- •6.7 Споживані струм і потужність

- •6.8 Вхідні і вихідні струми, напруги

- •6.9 Порогові напруги

- •6.10 Допустимі значення основних параметрів

- •7 Базові логічні елементи

- •7.1 Базовий ттл (ттлш) - елемент і - ні

- •7.2 Базовий езл - елемент або/або-ні

- •7.3 Базовий кмон елемент або-ні

- •8 Генератори тактових імпульсів (гті) на логічних елементах

- •8.1 Гті на двох інверторах

- •8.2 Гті на 3-х інверторах.

- •9 Функціональні пристроїкомп'ютерної (цифрової) електроніки

- •9.1 Комбінаційні цифрові пристрої (кцп)

- •9.1.1 Аналіз і синтез кцп

- •9.1.1.1 Аналіз кцп

- •9.1.1.2 Синтез кцп

- •9.1.2 Типові кцп

- •9.1.2.1 Шифратори та дешифратори

- •9.1.2.1.1 Шифратори двійкового коду

- •9.1.2.1.2 Шифратори двійково-десяткового коду

- •9.1.2.1.3 Дешифратори двійкового коду

- •9.1.2.1.4 Дешифратор bcd - коду всемисегментний код

- •9.1.2.1.4.1 Семисегментні індикатори на світлодіодах

- •9.1.2.2 Мультиплексори й демультиплексори

- •9.1.2.2.1 Мультиплексори

- •9.1.2.2.2 Демультиплексори

- •9.1.2.2.3 Мультиплексори-селектори (мультиплексори-демультиплексори)

- •9.1.2.3 Cуматори і напівсуматори

- •9.1.2.4 Пристрої контролю парності (пкп)

- •9.1.2.5 Цифрові компаратори

- •9.1.3 Використання для проектування кцп мультиплексорів, дешифраторів і постійного запам’ятовуючого пристрою

- •9.1.3.1 Побудова кцп на мультиплексорах

- •9.1.3.2 Побудова кцп на дешифраторах

- •9.1.3.3 Побудова кцп на постійному запам’ятовуючому пристрої (пзп)

- •9.2 Послідовні цифрові пристрої

- •9.2.1 Тригери

- •9.2.1.1 Тригери на логічних елементах

- •9.2.1.1.1 Rs - тригери

- •9.2.1.1.1.1 Асинхронні rs - тригери

- •9.2.1.1.1.2 Синхронні rs - тригери

- •9.2.1.1.2 Т-тригери (тригери з лічильним входом)

- •9.2.1.1.3 D - тригери (тригери затримки)

- •9.2.1.1.4 Jk - тригери

- •9.2.1.2 Тригери у інтегральному виконанні

- •9.2.2 Регістри

- •9.2.2.1 Паралельні регістри

- •9.2.2.2 Послідовні (зсуваючі) регістри

- •9.2.2.3 Регістри зсуву

- •9.2.2.4 Послідовно-паралельні і паралельно-послідовні регістри

- •9.2.2.5 Регістри у інтегральному виконанні

- •9.2.3 Лічильники

- •9.2.3.1 Асинхронний двійковий лічильник, що підсумовує, з послідовним перенесенням

- •9.2.3.2 Асинхронний двійковий лічильник, що віднімає, із послідовним перенесенням

- •9.2.3.3 Асинхронні реверсивні двійкові лічильники з послідовним перенесенням

- •9.2.3.4 Синхронний лічильник з наскрізним перенесенням

- •9.2.3.5 Десяткові лічильники

- •9.2.3.6 Лічильники в інтегральному виконанні

- •9.2.4 Подільники частоти

- •9.2.5 Розподілювачі

- •10 Зв'язок мп-ра і омеом з аналоговим об'єктом управління і з пк

- •10.1 Структура типової локальної мікропроцесорної системи управління (лмпсу)

- •10.1.1 Призначення і схемна реалізація окремих вузлів лмпсу

- •10.1.1.1 Аналоговий мультиплексор (ампс)

- •10.1.1.2 Пристрій вибірки-зберігання (пвз)

- •10.1.1.3 Аналого-цифровий перетворювач (ацп)

- •10.1.1.4 Ведена однокристальна мікроЕом (омеом)

- •10.1.1.5 Шинний формувач (шф)

- •10.1.1.6 Регістри (Рг1...Рг3)

- •10.1.1.7 Схеми узгодження рівнів (сур1...Сур3)

- •10.1.1.8 Цифро-аналогові перетворювачі (цап1...Цап3)

- •10.2 Застосування ацп і пвз при введенні аналогової інформації в мпс

- •10.2.1 Розрахунок ацп

- •10.2.2.1 Опис мікросхеми к1113 пв1

- •10.2.2.2 Розрахунок мікросхеми к1113 пв1

- •10.2.2.3 Введення даних від ацп в мпс через ппі в режимі 0

- •10.2.3 Пристрій вибірки і зберігання (пвз)

- •10.2.3.1 Обґрунтування застосування пвз

- •10.2.3.2 Принцип дії, схема й основні параметри пвз

- •Р Рисунок 10.17исунок 10.17

- •10.2.3.3 Функціональні можливості і схема включення мікросхеми пвз к1100ск2 (кр 1100ск2)

- •10.2.4.1Опис мікросхеми max154. Часові діаграми і режими роботи

- •10.2.4.1.1 Опис роботи паралельного 4-х розрядного ацп

- •10.2.4.2 Розрахунок ацп max154

- •10.3 Застосування цап прививодіцифрової інформації з мпс

- •10.3.1 РозрахунокЦап на матриці r-2Rзпідсумовуваннямструмів

- •10.3.2.1 Опис мікросхеми к 572 па1

- •10.3.2.2 Розрахунок цап к 572 па1

- •10.3.3.1 Опис мікросхеми max506

- •10.3.3.2 Розрахунок цап max506

- •10.4 Особливості апаратної і програмної реалізації модуля ацп- цап мпс

- •10.4.1 Апаратний рівень

- •10.4.2 Програмний рівень

- •10.5 Обмін між мп-м (омеом) і пк по послідовному каналузв'язку за допомогою інтерфейсу rs-232с

- •10.5.1 Універсальний асинхронний послідовний програмований приймач – передавач (уапп)

- •10.5.2 Пристрій перетворення рівнів (ппр)

- •10.5.4 Буферний регістр адреси rs– 232с

- •10.5.5 Шинний формувач

- •10.6 Вибір і розрахунок датчиків, нормуючих перетворювачів і фільтрів нижніх частот (фнч)

- •10.6.1 Вибір і розрахунок датчиків і нормуючих перетворювачів

- •10.6.1.1 Вибір датчиків

- •10.6.1.2 Вибір і розрахунок нормуючих перетворювачів

- •10.6.3 Розрахунок фнч

- •10.7 Розробка схеми алгоритму і керуючої програми

- •11 Список літератури

9.2.2 Регістри

Регістрами називають послідовні цифрові пристрої, призначені для запам'ятовування багаторозрядних цифрових кодів і виконання над ними деяких логічних перетворень. Основу регістрів складають тригери, кількість яких дорівнює кількості розрядів цифрового коду. Один тригер зберігає 1 біт інформації (один двійковий розряд), відповідно N-розрядний регістр спроможний зберігати N біт інформації. Крім тригерів, регістри містять допоміжні схеми, що забезпечують прийом коду в регістр, видачу коду з регістру, зсув коду вправо або вліво на необхідну кількість розрядів, перетворення паралельного коду в послідовний і навпаки, виконання над окремими розрядами регістру логічних операцій, наприклад, І, АБО, ВИЛУЧАЮЧЕ АБО, установлення регістра в початковий стан (“СКИДАННЯ”) та ін.

В залежності від способу введення і виведення розрядів числа, регістри поділяються на :

паралельні ;

послідовні ;

послідовно-паралельні ;

паралельно-послідовні .

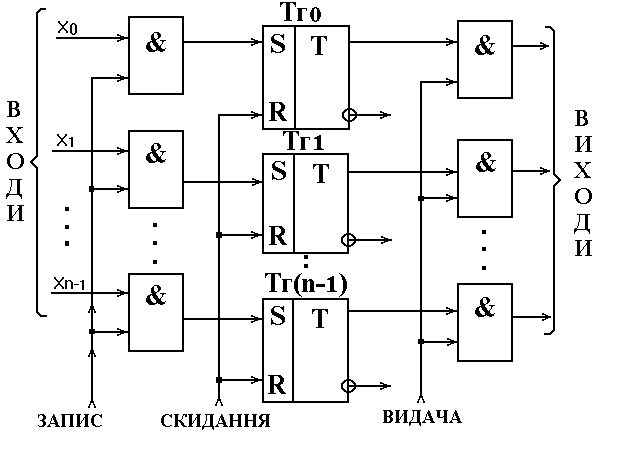

9.2.2.1 Паралельні регістри

В таких регістрах введення і виведення інформації здійснюється в паралельній формі - одночасно усіх розрядів.

В залежності від кількості вхідних і вихідних каналів, паралельні регістри поділяються на однофазні (кожний розряд передається по одному каналу в прямому коді) і парафазні (розряди передаються двома каналами в прямому та інверсному кодах).

Рисунок 9.43

При парафазному обміні інформацією, на R, S входах будь-якого тригера завжди присутня комбінація сигналів Хі = 1, Xi = 0, або Хі = 0, Xi = 1, що встановлює його в необхідний стан незалежно від того, у якому стані цей тригер знаходився до цього, тобто встановлення регістра у початковий стан не потрібно.

Під дією сигналу ПРМ Рг 1 ( прийом до регістру 1) n-розрядний код записується в регістр Рг 1, а сигналом ПД Рг2 (передача до регістру 2) - передається в Рг 2.

На рисунку 9.44 показаний паралельний регістр, з однофазним обміном інформації, виконаний на асинхронних RS-тригерах і кон’юнкторах.

Завдяки тому, що інформаційні сигнали, що надходять тільки на S входи, не можуть встановити відповідні тригери в стан 0 (через що число може бути записане з помилкою), перед записом, усі тригери регістра встановлюються у нульовий стан сигналом “СКИДАННЯ”.

Слід зазначити, що ця особливість характерна тільки для регістрів з однофазним записом, виконаних на RS-тригерах. Якщо в якості елемента пам'яті використовувати D-тригери, то їх попереднє встановлення у нульовий стан при однофазному записі не потрібне (рисунок 9.45).