- •Комп’ютерна електроніка

- •1 Вступ

- •2 Дискретизація аналогових сигналів

- •2.1 Квантування за рівнем

- •2.2 Квантування за часом

- •2.3 Квантування за рівнем і за часом

- •2.3.1 Розмір похибки ацп

- •2.3.2 Вибір величини кроку квантування за часом

- •3 Застосування алгебри логіки (булевої алгебри) при аналізі і синтезі цифрових електронних пристроїв

- •3.1 Визначення і способи задання перемикальних функцій

- •3.4 Базисні логічні функції

- •3.5 Принцип двоїстості булевої алгебри

- •3.6 Основні тотожності булевої алгебри

- •3.7 Основні закони булевої алгебри

- •3.8 Досконала диз’юнктивна нормальна форма (дднф) запису булевих виразів

- •3.9 Диз’юнктивна нормальна форма

- •3.10 Досконала кон’юнктивна нормальна форма (дкнф) запису булевих виразів

- •3.11 Кон’юнктивна нормальна форма (кнф)

- •3.12 Мінімізація логічних функцій

- •3.12.1 Алгебраїчний спосіб мінімізації пф

- •3.12.2 Мінімізація пф із використанням діаграм Вейча (карт Карно)

- •3.12.2.1 Мінімізація пф за допомогою діаграм Вейча

- •3.12.2.1.1 Загальне правило мінімізації

- •3.12.2.1.2 Приклади мінімізації пф за допомогою діаграм Вейча

- •3.12.2.2 Мінімізація пф за допомогою карт Карно

- •4 Логічні елементи

- •4.1 Інвертор (логічний елемент ні)

- •4.2 Кон’юнктор (логічний елемент і)

- •4.3 Диз’юнктор (логічний елемент або)

- •4.4 Повторювач

- •4.7 Виключаюче або

- •4.8 Додавання по модулю два (непарність)

- •4.9 Додавання по модулю два з запереченням (парність)

- •4.10 Еквівалентність

- •4.11 Нееквівалентність

- •4.13 Заборона

- •4.14 Логічні елементи з відкритим колектором

- •4.15 Логічні елементи з третім станом

- •5 Реалізація логічних функцій у різних базисах

- •5.1 Базисні набори ле і їх взаємозв'язок

- •5.2 Реалізація логічних функцій у різноманітних базисах

- •5.2.1 Реалізація елемента “Рівнозначність” (виключаюче або - ні)

- •5.2.2 Реалізація елемента “нерівнозначність” (виключаюче або, сума по модулю два)

- •5.2.3 Реалізація елемента “Заборона”

- •5.2.4 Реалізація багатолітерних логічних функцій на елементах з невеликою кількістю входів

- •6 Параметри і характеристики цифрових інтегральних мікросхем (імс)

- •6.1 Коефіцієнт об'єднання по входу (Коб)

- •6.2 Коефіцієнт розгалуження по виходу (Кроз)

- •6.3 Статичні характеристики

- •6.4 Завадостійкість

- •6.5 Динамічні характеристики і параметри

- •6.6 Вигляд реалізованої логічної функції

- •6.7 Споживані струм і потужність

- •6.8 Вхідні і вихідні струми, напруги

- •6.9 Порогові напруги

- •6.10 Допустимі значення основних параметрів

- •7 Базові логічні елементи

- •7.1 Базовий ттл (ттлш) - елемент і - ні

- •7.2 Базовий езл - елемент або/або-ні

- •7.3 Базовий кмон елемент або-ні

- •8 Генератори тактових імпульсів (гті) на логічних елементах

- •8.1 Гті на двох інверторах

- •8.2 Гті на 3-х інверторах.

- •9 Функціональні пристроїкомп'ютерної (цифрової) електроніки

- •9.1 Комбінаційні цифрові пристрої (кцп)

- •9.1.1 Аналіз і синтез кцп

- •9.1.1.1 Аналіз кцп

- •9.1.1.2 Синтез кцп

- •9.1.2 Типові кцп

- •9.1.2.1 Шифратори та дешифратори

- •9.1.2.1.1 Шифратори двійкового коду

- •9.1.2.1.2 Шифратори двійково-десяткового коду

- •9.1.2.1.3 Дешифратори двійкового коду

- •9.1.2.1.4 Дешифратор bcd - коду всемисегментний код

- •9.1.2.1.4.1 Семисегментні індикатори на світлодіодах

- •9.1.2.2 Мультиплексори й демультиплексори

- •9.1.2.2.1 Мультиплексори

- •9.1.2.2.2 Демультиплексори

- •9.1.2.2.3 Мультиплексори-селектори (мультиплексори-демультиплексори)

- •9.1.2.3 Cуматори і напівсуматори

- •9.1.2.4 Пристрої контролю парності (пкп)

- •9.1.2.5 Цифрові компаратори

- •9.1.3 Використання для проектування кцп мультиплексорів, дешифраторів і постійного запам’ятовуючого пристрою

- •9.1.3.1 Побудова кцп на мультиплексорах

- •9.1.3.2 Побудова кцп на дешифраторах

- •9.1.3.3 Побудова кцп на постійному запам’ятовуючому пристрої (пзп)

- •9.2 Послідовні цифрові пристрої

- •9.2.1 Тригери

- •9.2.1.1 Тригери на логічних елементах

- •9.2.1.1.1 Rs - тригери

- •9.2.1.1.1.1 Асинхронні rs - тригери

- •9.2.1.1.1.2 Синхронні rs - тригери

- •9.2.1.1.2 Т-тригери (тригери з лічильним входом)

- •9.2.1.1.3 D - тригери (тригери затримки)

- •9.2.1.1.4 Jk - тригери

- •9.2.1.2 Тригери у інтегральному виконанні

- •9.2.2 Регістри

- •9.2.2.1 Паралельні регістри

- •9.2.2.2 Послідовні (зсуваючі) регістри

- •9.2.2.3 Регістри зсуву

- •9.2.2.4 Послідовно-паралельні і паралельно-послідовні регістри

- •9.2.2.5 Регістри у інтегральному виконанні

- •9.2.3 Лічильники

- •9.2.3.1 Асинхронний двійковий лічильник, що підсумовує, з послідовним перенесенням

- •9.2.3.2 Асинхронний двійковий лічильник, що віднімає, із послідовним перенесенням

- •9.2.3.3 Асинхронні реверсивні двійкові лічильники з послідовним перенесенням

- •9.2.3.4 Синхронний лічильник з наскрізним перенесенням

- •9.2.3.5 Десяткові лічильники

- •9.2.3.6 Лічильники в інтегральному виконанні

- •9.2.4 Подільники частоти

- •9.2.5 Розподілювачі

- •10 Зв'язок мп-ра і омеом з аналоговим об'єктом управління і з пк

- •10.1 Структура типової локальної мікропроцесорної системи управління (лмпсу)

- •10.1.1 Призначення і схемна реалізація окремих вузлів лмпсу

- •10.1.1.1 Аналоговий мультиплексор (ампс)

- •10.1.1.2 Пристрій вибірки-зберігання (пвз)

- •10.1.1.3 Аналого-цифровий перетворювач (ацп)

- •10.1.1.4 Ведена однокристальна мікроЕом (омеом)

- •10.1.1.5 Шинний формувач (шф)

- •10.1.1.6 Регістри (Рг1...Рг3)

- •10.1.1.7 Схеми узгодження рівнів (сур1...Сур3)

- •10.1.1.8 Цифро-аналогові перетворювачі (цап1...Цап3)

- •10.2 Застосування ацп і пвз при введенні аналогової інформації в мпс

- •10.2.1 Розрахунок ацп

- •10.2.2.1 Опис мікросхеми к1113 пв1

- •10.2.2.2 Розрахунок мікросхеми к1113 пв1

- •10.2.2.3 Введення даних від ацп в мпс через ппі в режимі 0

- •10.2.3 Пристрій вибірки і зберігання (пвз)

- •10.2.3.1 Обґрунтування застосування пвз

- •10.2.3.2 Принцип дії, схема й основні параметри пвз

- •Р Рисунок 10.17исунок 10.17

- •10.2.3.3 Функціональні можливості і схема включення мікросхеми пвз к1100ск2 (кр 1100ск2)

- •10.2.4.1Опис мікросхеми max154. Часові діаграми і режими роботи

- •10.2.4.1.1 Опис роботи паралельного 4-х розрядного ацп

- •10.2.4.2 Розрахунок ацп max154

- •10.3 Застосування цап прививодіцифрової інформації з мпс

- •10.3.1 РозрахунокЦап на матриці r-2Rзпідсумовуваннямструмів

- •10.3.2.1 Опис мікросхеми к 572 па1

- •10.3.2.2 Розрахунок цап к 572 па1

- •10.3.3.1 Опис мікросхеми max506

- •10.3.3.2 Розрахунок цап max506

- •10.4 Особливості апаратної і програмної реалізації модуля ацп- цап мпс

- •10.4.1 Апаратний рівень

- •10.4.2 Програмний рівень

- •10.5 Обмін між мп-м (омеом) і пк по послідовному каналузв'язку за допомогою інтерфейсу rs-232с

- •10.5.1 Універсальний асинхронний послідовний програмований приймач – передавач (уапп)

- •10.5.2 Пристрій перетворення рівнів (ппр)

- •10.5.4 Буферний регістр адреси rs– 232с

- •10.5.5 Шинний формувач

- •10.6 Вибір і розрахунок датчиків, нормуючих перетворювачів і фільтрів нижніх частот (фнч)

- •10.6.1 Вибір і розрахунок датчиків і нормуючих перетворювачів

- •10.6.1.1 Вибір датчиків

- •10.6.1.2 Вибір і розрахунок нормуючих перетворювачів

- •10.6.3 Розрахунок фнч

- •10.7 Розробка схеми алгоритму і керуючої програми

- •11 Список літератури

2 Дискретизація аналогових сигналів

У інформаційно-управляючих системах часто виникає задача обробки аналогових повідомлень, знятих з аналогових датчиків. Для введення такої інформації в комп'ютер, що веде обробку в цифровому вигляді, здійснюється дискретизація (квантування) аналогових сигналів.

Розрізняють 3-и види дискретизації:

за рівнем;

за часом;

за рівнем і часом (комбінована).

Розглянемо кожний з названих видів квантування більш докладно.

2.1 Квантування за рівнем

Припустимо, що інформація відображається аналоговою (безперевною) напругою U(t), що повільно змінюється за законом, поданим на рисунку 2.1.

|

|

|

Рисунок 2.1 |

Миттєві значення цієї напруги лежать у діапазоні ((Umin=0)..Umax)). При виконанні операції квантування за рівнем діапазон зміни значень безперервної величини розбивається на ряд рівнів Nр, включаючи нульовий. Число Nр визначається з виразу

![]() ,

(

2.1 )

,

(

2.1 )

де U - величина кроку квантування за рівнем. Остання є постійною величиною (U=const), і визначається необхідною похибкою дискретизації. У нашому прикладі Nр = 5. Кожний рівень пронумерований у десятковій системі числення. Робота квантувача зводиться до слідуючого: він визначає моменти часу, коли вхідний аналоговий сигнал досягає чергового дискретного рівня. Ці моменти позначені t0, t1, t2, t3... Очевидно, що при нелінійному вхідному сигналі інтервал між сусідніми часовими відліками є змінною величиною (t = var). Прикладом пристроїв, у яких здійснюється квантування за рівнем є релейні (граничні) пристрої.

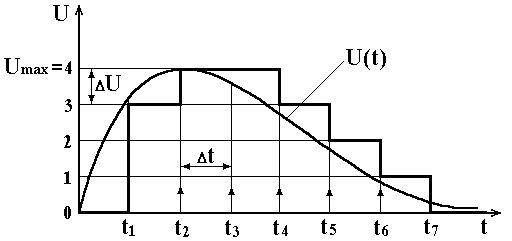

2.2 Квантування за часом

При виконанні операції квантування за часом (рисунок 2.2.) аналоговий вхідний сигнал замінюється дискретним, що знімається з виходу квантувача в дискретні моменти часу t1, t2, t3,... Інтервал між сусідніми моментами часу t=t1-t0=t2-t1=...=const. Очевидно, що різниця сусідніх значень вхідного сигналу при нелінійному законі зміни вхідної напруги є змінною величиною (U=var).

|

|

|

Рисунок 2.2 |

Прикладом пристроїв, у яких здійснюється квантування за часом є імпульсні системи автоматичного керування.

2.3 Квантування за рівнем і за часом

Робота такого перетворювача (рисунок 2.3.) зводиться до того, що з безперевного сигналу періодично проводяться вибірки миттєвих значень. Часовий інтервал між сусідніми вибірками t = const. Кожна вибірка округляється перетворювачем до найближчого рівня квантування, отриманого від дискретизації за рівнем. Інтервал між сусідніми рівнями U = const. Значення рівня представляється в десятковій або двійковій системі числення (десятковим або двійковим кодом).

|

|

|

Рисунок 2.3 |

Код рівня в свою чергу представляється цифровим сигналом. Вихідний сигнал має східчасту форму і з визначеним ступенем точності відповідає перетворюваній аналоговій напрузі. За таким принципом працюють електронні аналогово-цифрові перетворювачі (АЦП) [10,13].