- •Комп’ютерна електроніка

- •1 Вступ

- •2 Дискретизація аналогових сигналів

- •2.1 Квантування за рівнем

- •2.2 Квантування за часом

- •2.3 Квантування за рівнем і за часом

- •2.3.1 Розмір похибки ацп

- •2.3.2 Вибір величини кроку квантування за часом

- •3 Застосування алгебри логіки (булевої алгебри) при аналізі і синтезі цифрових електронних пристроїв

- •3.1 Визначення і способи задання перемикальних функцій

- •3.4 Базисні логічні функції

- •3.5 Принцип двоїстості булевої алгебри

- •3.6 Основні тотожності булевої алгебри

- •3.7 Основні закони булевої алгебри

- •3.8 Досконала диз’юнктивна нормальна форма (дднф) запису булевих виразів

- •3.9 Диз’юнктивна нормальна форма

- •3.10 Досконала кон’юнктивна нормальна форма (дкнф) запису булевих виразів

- •3.11 Кон’юнктивна нормальна форма (кнф)

- •3.12 Мінімізація логічних функцій

- •3.12.1 Алгебраїчний спосіб мінімізації пф

- •3.12.2 Мінімізація пф із використанням діаграм Вейча (карт Карно)

- •3.12.2.1 Мінімізація пф за допомогою діаграм Вейча

- •3.12.2.1.1 Загальне правило мінімізації

- •3.12.2.1.2 Приклади мінімізації пф за допомогою діаграм Вейча

- •3.12.2.2 Мінімізація пф за допомогою карт Карно

- •4 Логічні елементи

- •4.1 Інвертор (логічний елемент ні)

- •4.2 Кон’юнктор (логічний елемент і)

- •4.3 Диз’юнктор (логічний елемент або)

- •4.4 Повторювач

- •4.7 Виключаюче або

- •4.8 Додавання по модулю два (непарність)

- •4.9 Додавання по модулю два з запереченням (парність)

- •4.10 Еквівалентність

- •4.11 Нееквівалентність

- •4.13 Заборона

- •4.14 Логічні елементи з відкритим колектором

- •4.15 Логічні елементи з третім станом

- •5 Реалізація логічних функцій у різних базисах

- •5.1 Базисні набори ле і їх взаємозв'язок

- •5.2 Реалізація логічних функцій у різноманітних базисах

- •5.2.1 Реалізація елемента “Рівнозначність” (виключаюче або - ні)

- •5.2.2 Реалізація елемента “нерівнозначність” (виключаюче або, сума по модулю два)

- •5.2.3 Реалізація елемента “Заборона”

- •5.2.4 Реалізація багатолітерних логічних функцій на елементах з невеликою кількістю входів

- •6 Параметри і характеристики цифрових інтегральних мікросхем (імс)

- •6.1 Коефіцієнт об'єднання по входу (Коб)

- •6.2 Коефіцієнт розгалуження по виходу (Кроз)

- •6.3 Статичні характеристики

- •6.4 Завадостійкість

- •6.5 Динамічні характеристики і параметри

- •6.6 Вигляд реалізованої логічної функції

- •6.7 Споживані струм і потужність

- •6.8 Вхідні і вихідні струми, напруги

- •6.9 Порогові напруги

- •6.10 Допустимі значення основних параметрів

- •7 Базові логічні елементи

- •7.1 Базовий ттл (ттлш) - елемент і - ні

- •7.2 Базовий езл - елемент або/або-ні

- •7.3 Базовий кмон елемент або-ні

- •8 Генератори тактових імпульсів (гті) на логічних елементах

- •8.1 Гті на двох інверторах

- •8.2 Гті на 3-х інверторах.

- •9 Функціональні пристроїкомп'ютерної (цифрової) електроніки

- •9.1 Комбінаційні цифрові пристрої (кцп)

- •9.1.1 Аналіз і синтез кцп

- •9.1.1.1 Аналіз кцп

- •9.1.1.2 Синтез кцп

- •9.1.2 Типові кцп

- •9.1.2.1 Шифратори та дешифратори

- •9.1.2.1.1 Шифратори двійкового коду

- •9.1.2.1.2 Шифратори двійково-десяткового коду

- •9.1.2.1.3 Дешифратори двійкового коду

- •9.1.2.1.4 Дешифратор bcd - коду всемисегментний код

- •9.1.2.1.4.1 Семисегментні індикатори на світлодіодах

- •9.1.2.2 Мультиплексори й демультиплексори

- •9.1.2.2.1 Мультиплексори

- •9.1.2.2.2 Демультиплексори

- •9.1.2.2.3 Мультиплексори-селектори (мультиплексори-демультиплексори)

- •9.1.2.3 Cуматори і напівсуматори

- •9.1.2.4 Пристрої контролю парності (пкп)

- •9.1.2.5 Цифрові компаратори

- •9.1.3 Використання для проектування кцп мультиплексорів, дешифраторів і постійного запам’ятовуючого пристрою

- •9.1.3.1 Побудова кцп на мультиплексорах

- •9.1.3.2 Побудова кцп на дешифраторах

- •9.1.3.3 Побудова кцп на постійному запам’ятовуючому пристрої (пзп)

- •9.2 Послідовні цифрові пристрої

- •9.2.1 Тригери

- •9.2.1.1 Тригери на логічних елементах

- •9.2.1.1.1 Rs - тригери

- •9.2.1.1.1.1 Асинхронні rs - тригери

- •9.2.1.1.1.2 Синхронні rs - тригери

- •9.2.1.1.2 Т-тригери (тригери з лічильним входом)

- •9.2.1.1.3 D - тригери (тригери затримки)

- •9.2.1.1.4 Jk - тригери

- •9.2.1.2 Тригери у інтегральному виконанні

- •9.2.2 Регістри

- •9.2.2.1 Паралельні регістри

- •9.2.2.2 Послідовні (зсуваючі) регістри

- •9.2.2.3 Регістри зсуву

- •9.2.2.4 Послідовно-паралельні і паралельно-послідовні регістри

- •9.2.2.5 Регістри у інтегральному виконанні

- •9.2.3 Лічильники

- •9.2.3.1 Асинхронний двійковий лічильник, що підсумовує, з послідовним перенесенням

- •9.2.3.2 Асинхронний двійковий лічильник, що віднімає, із послідовним перенесенням

- •9.2.3.3 Асинхронні реверсивні двійкові лічильники з послідовним перенесенням

- •9.2.3.4 Синхронний лічильник з наскрізним перенесенням

- •9.2.3.5 Десяткові лічильники

- •9.2.3.6 Лічильники в інтегральному виконанні

- •9.2.4 Подільники частоти

- •9.2.5 Розподілювачі

- •10 Зв'язок мп-ра і омеом з аналоговим об'єктом управління і з пк

- •10.1 Структура типової локальної мікропроцесорної системи управління (лмпсу)

- •10.1.1 Призначення і схемна реалізація окремих вузлів лмпсу

- •10.1.1.1 Аналоговий мультиплексор (ампс)

- •10.1.1.2 Пристрій вибірки-зберігання (пвз)

- •10.1.1.3 Аналого-цифровий перетворювач (ацп)

- •10.1.1.4 Ведена однокристальна мікроЕом (омеом)

- •10.1.1.5 Шинний формувач (шф)

- •10.1.1.6 Регістри (Рг1...Рг3)

- •10.1.1.7 Схеми узгодження рівнів (сур1...Сур3)

- •10.1.1.8 Цифро-аналогові перетворювачі (цап1...Цап3)

- •10.2 Застосування ацп і пвз при введенні аналогової інформації в мпс

- •10.2.1 Розрахунок ацп

- •10.2.2.1 Опис мікросхеми к1113 пв1

- •10.2.2.2 Розрахунок мікросхеми к1113 пв1

- •10.2.2.3 Введення даних від ацп в мпс через ппі в режимі 0

- •10.2.3 Пристрій вибірки і зберігання (пвз)

- •10.2.3.1 Обґрунтування застосування пвз

- •10.2.3.2 Принцип дії, схема й основні параметри пвз

- •Р Рисунок 10.17исунок 10.17

- •10.2.3.3 Функціональні можливості і схема включення мікросхеми пвз к1100ск2 (кр 1100ск2)

- •10.2.4.1Опис мікросхеми max154. Часові діаграми і режими роботи

- •10.2.4.1.1 Опис роботи паралельного 4-х розрядного ацп

- •10.2.4.2 Розрахунок ацп max154

- •10.3 Застосування цап прививодіцифрової інформації з мпс

- •10.3.1 РозрахунокЦап на матриці r-2Rзпідсумовуваннямструмів

- •10.3.2.1 Опис мікросхеми к 572 па1

- •10.3.2.2 Розрахунок цап к 572 па1

- •10.3.3.1 Опис мікросхеми max506

- •10.3.3.2 Розрахунок цап max506

- •10.4 Особливості апаратної і програмної реалізації модуля ацп- цап мпс

- •10.4.1 Апаратний рівень

- •10.4.2 Програмний рівень

- •10.5 Обмін між мп-м (омеом) і пк по послідовному каналузв'язку за допомогою інтерфейсу rs-232с

- •10.5.1 Універсальний асинхронний послідовний програмований приймач – передавач (уапп)

- •10.5.2 Пристрій перетворення рівнів (ппр)

- •10.5.4 Буферний регістр адреси rs– 232с

- •10.5.5 Шинний формувач

- •10.6 Вибір і розрахунок датчиків, нормуючих перетворювачів і фільтрів нижніх частот (фнч)

- •10.6.1 Вибір і розрахунок датчиків і нормуючих перетворювачів

- •10.6.1.1 Вибір датчиків

- •10.6.1.2 Вибір і розрахунок нормуючих перетворювачів

- •10.6.3 Розрахунок фнч

- •10.7 Розробка схеми алгоритму і керуючої програми

- •11 Список літератури

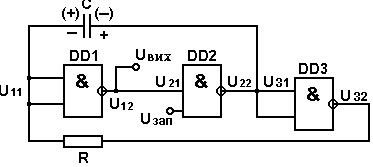

8.2 Гті на 3-х інверторах.

У схемі такого генератора (рисунок 8.3) резистор R відключений від виходу DD1 і залучений до виходу елемента DD3.

-

Рисунок 8.3

Перезаряд конденсатора С відбувається через резистор R і вихідні ланцюги DD2 і DD3. Оскільки елемент DD1 не навантажений ємністю, імпульси на його виході мають добру прямокутність. Принцип роботи схеми аналогічний до попередньої. Часова діаграма роботи показана на рисунку 8.4.

Значення опору резистора R вибирається за умови [12]

240 Ом < R < 1,5 кОм ( 8.5 )

![]()

9 Функціональні пристроїкомп'ютерної (цифрової) електроніки

9.1 Комбінаційні цифрові пристрої (кцп)

Логічні пристрої, вихідні функції котрих однозначно визначаються комбінацією вхідних логічних змінних в аналізований момент часу, називаються комбінаційними.

9.1.1 Аналіз і синтез кцп

У процесі проектування будь-якого пристрою виконується ряд дій, що можна віднести до задач аналізу й синтезу.

9.1.1.1 Аналіз кцп

Виконання задач аналізу КЦП припускає наявність готової функціональної схеми пристрою на логічних елементах заданого базису. У процесі аналізу оцінюються деякі характеристики наявної схеми КЦП. Наприклад, можна скласти булевий вираз і таблицю істинності, що визначають перетворення інформації в КЦП; мінімізувати логічну функцію, що виконує аналізована схема; оцінити апаратні витрати на реалізацію схеми; її швидкодію; споживану потужність; розглянути можливість утворення в схемі помилкових небезпечних станів у результаті змагань (гонок) і ін.

9.1.1.2 Синтез кцп

Синтез КЦП передбачає побудову функціональної схеми пристрою, тобто визначення складу необхідних логічних елементів і з'єднань між ними, при яких забезпечується перетворення вхідних цифрових сигналів у вихідні відповідно до заданих умов роботи пристрою. У процесі синтезу необхідно мінімізувати апаратні витрати на реалізацію пристрою. Роздивимося особливості синтезу КЦП з одним виходом. Послідовність синтезу доцільно розбити на ряд етапів.

Етап 1. Задання логічної функції, що визначає функціонування синтезованого КЦП. Як відзначалося раніше, це можна зробити словесно, за допомогою таблиць істинності або булевих виразів.

Етап 2. Мінімізація логічної функції, що здійснюється алгебраїчним або графічним методом (за допомогою діаграм Вейча, карт Карно).

Етап 3. Запис булевого виразу мінімізованої перемикальної функції.

Етап 4. Перетворення булевого виразу мінімізованої ПФ для реалізації її у заданому базисі І-НІ або АБО-НІ.

Етап 5. Складання функціональної схеми КЦП, тобто зображення потрібних логічних елементів і зв'язків між ними.

Проілюструємо етапи синтезу КЦП на прикладі.

Необхідно синтезувати на елементах І-НІ КЦП на три входи, вихідний сигнал якого збігається з більшістю вхідних сигналів.

Даний словесний опис задає логічну функцію мажоритарність. Її роботу відбиває таблиця істинності (таблиця 9.1).

Таблиця 9.1

-

№ набору

С

В

А

F

0

0

0

0

0

1

0

0

1

0

2

0

1

0

0

3

0

1

1

1

4

1

0

0

0

5

1

0

1

1

6

1

1

0

1

7

1

1

1

1

Булевий вираз ПФ у СДНФ має вигляд

|

|

( 9.1 ) |

Мінімізуючи даний вираз, використовуючи тотожності й теореми булевой алгебри, отримаємо

|

|

( 9.2 ) |

Перетворимо даний вираз для його реалізації у базисі І-НІ. Застосовуючи теорему де Моргана отримаємо

|

|

( 9.3 ) |

Функціональна схема синтезованого КЦП, що реалізує вираз (9.3) на елементах І-НІ , приведена на рисунку 9.1.

-

Рисунок 9.1

У практиці широко застосовуються КЦП, що мають декілька виходів. При проектуванні таких пристроїв можна скористатися розглянутими вище правилами синтезу, якщо уявити пристрій у вигляді сукупності декількох КЦП із загальними входами.

Функціонування КЦП із m виходами описується (задається) аналогічною кількістю перемикальних функцій, над кожною з яких у процесі синтезу виконуються дії, описані вище.