- •9 Функциональные устройства компьютерной (цифровой) электроники 3

- •9 Функциональные устройства компьютерной (цифровой) электроники

- •9.1 Комбинационные цифровые устройства (кцу)

- •9.1.1 Анализ и синтез кцу

- •9.1.1.1 Анализ кцу

- •9.1.1.2 Синтез кцу

- •9.1.2 Типовые кцу

- •9.1.2.1 Шифраторы и дешифраторы

- •9.1.2.1.1 Шифраторы двоичного кода

- •9.1.2.1.2 Шифраторы двоично-десятичного кода

- •9.1.2.1.3 Дешифраторы двоичного кода

- •9.1.2.1.4 Дешифратор bcd-кода в семисегментный код

- •9.1.2.1.4.1 Семисегментные индикаторы на светодиодах

- •9.1.2.2 Мультиплексоры и демультиплексоры

- •9.1.2.2.1 Мультиплексоры

- •9.1.2.2.2 Демультиплексоры

- •9.1.2.2.3 Мультиплексоры–селекторы (мультиплексоры-демультиплексоры)

- •9.1.2.3 Сумматоры и полусумматоры

- •9.1.2.4 Устройства контроля четности (укч)

- •9.1.2.5 Цифровые компараторы

- •9.1.3 Использование для проектирования кцу мультиплексоров, дешифраторов и постоянных запоминающих устройств

- •9.1.3.1 Построение кцу на мультиплексорах

- •9.1.3.2 Построение кцу на дешифраторах

- •9.1.3.3 Построение кцу на постоянном запоминающем устройстве (пзу)

- •9.2 Последовательностные цифровые устройства

- •9.2.1 Триггеры

- •9.2.1.1 Триггеры на логических элементах

- •9.2.1.1.1 Rs - триггеры

- •9.2.1.1.1.1 Асинхронные rs - триггеры

- •9.2.1.1.1.2 Синхронные rs - триггеры

- •9.2.1.1.2 Т-триггеры (триггеры со счетным входом)

- •9.2.1.1.3 D-триггеры (триггеры задержки)

- •9.2.1.1.4 Jk-триггеры

- •9.2.1.2 Триггеры в интегральном исполнении

- •9.2.2 Регистры

- •9.2.2.1 Параллельные регистры

- •9.2.2.2 Последовательные (сдвигающие) регистры

- •9.2.2.3 Регистры сдвига

- •9.2.2.4 Последовательно-параллельные и параллельно-последовательные регистры

- •9.2.2.5 Регистры в интегральном исполнении

- •9.2.3.1 Асинхронный суммирующий двоичный счетчик с последовательным переносом

- •9.2.3.2 Асинхронный вычитающий двоичный счетчик с последовательным переносом

- •9.2.3.3 Асинхронные реверсивные двоичные счетчики с последовательным переносом

- •9.2.3.4 Синхронный счетчик со сквозным переносом

- •9.2.3.5 Десятичные счетчики

- •9.2.3.6 Счетчики в интегральном исполнении

- •9.2.4 Делители частоты

- •9.2.5 Распределители

9.2.1.1.3 D-триггеры (триггеры задержки)

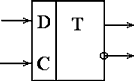

Содержат информационный (D) вход и тактовый (синхро, С) вход (рисунок 9.36).

|

а |

б |

|

Рисунок 9.36 | |

Существуют однотактные D-триггеры (рисунок 9.36, а), которые переключаются потенциалом или импульсом на тактовом входе, и двухтактные D-триггеры, которые переключаются динамическим сигналом (перепадом), например, из 1 в 0 (рисунок 9.36, б).

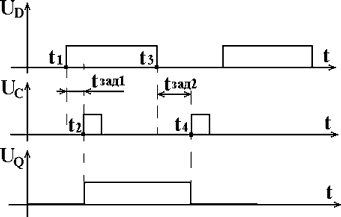

Ниже показаны: принципиальная схема (рисунок 9.37, а) и временные диаграммы работы (рисунок 9.37, б) однотактного D-триггера, выполненного на однотактном синхронном RS-триггере (RSC-триггере - DD1) и логическом элементе DD2.

|

а |

б |

|

Рисунок 9.37 | |

В момент прихода тактового импульса D-триггер переключается в состояние, определяемое сигналом на информационном входе D, т.е. схема запоминает сигнал на входе D в момент поступления синхроимпульса (Qt+1 = D) и хранит его до следующего тактового импульса. Задержка равна интервалу времени между моментами прихода информационного сигнала на D-вход и поступлением синхросигнала на С-вход: tзад1 = t2 - t1; tзад2 = t4 - t3 (рисунок 9.37, б). D-триггеры широко применяются в качестве элементов памяти, способных хранить 1 бит информации.

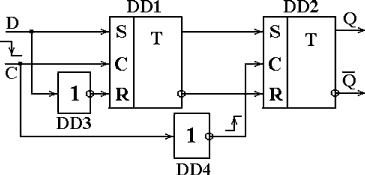

Ниже показаны: обозначение на электрических схемах (рисунок 9.38, а) и принципиальная схема (рисунок 9.38, б) двухтактного D-триггера, переключающегося перепадом из 1 в 0 на динамическом синхровходе С.

|

а |

б |

|

в | |

|

Рисунок 9.38 | |

Триггер выполнен на основе двух однотактных RSC-триггеров (DD1, DD2) и двух инверторов (DD3, DD4).

D-триггер можно использовать в качестве триггера со счетным входом (Т-триггера), если соединить его выводы как показано на рисунке 9.38, в.

9.2.1.1.4 Jk-триггеры

Является наиболее универсальным среди синхронных триггеров.

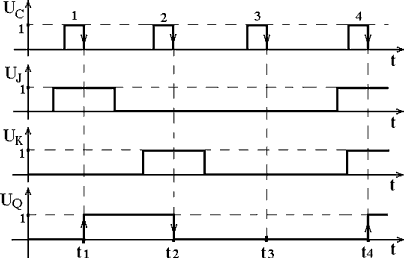

Ниже показаны: обозначение на электрических схемах (рисунок 9.40, а), принципиальная схема (рисунок 9.40, б), таблица истинности (таблица 9.13) и временные диаграммы работы (рисунок 9.40, в) двухтактного синхронного JK-триггера, переключающегося перепадом из 1 в 0 на динамическом синхровходе С.

|

а |

б |

|

в | |

|

Рисунок 9.40 | |

|

Таблица 9.13 | ||||

|

№ набора |

J |

K |

C |

Qt+1 |

|

0 |

0 |

0 |

|

Qt |

|

1 |

0 |

1 |

|

0 |

|

2 |

1 |

0 |

|

1 |

|

3 |

1 |

1 |

|

|

Рассмотрим работу

JK-триггера. Исходное состояние схемы -

нулевое (UQ

= 0) (рисунок

9.40, в). При поступлении среза первого

тактового импульса (момент t1)

сигнал на J-входе

равен 1, а на К-входе

- 0. Поэтому триггер переключается в

единичное состояние. Срезом второго

тактового импульса схема переключается

в нулевое состояние (момент t2),

т.к. в это время J=0, а К=1. В момент t3

оба управляющих сигнала J=K=0, поэтому

состояние схемы не изменяется (Qt+1

= Qt).

При поступлении среза 4-го синхроимпульса

(момент t4)

J=K=1, поэтому триггер переключается в

положение, противоположное исходному:

![]()

На основе универсального JK-триггера может быть построен ряд других триггеров.

Синхронный RS-триггер. Отождествим J=S и K=R. При запрете комбинации J=S=1 и K=R=1 таблица 9.13 сводится к таблице истинности RS-триггера (таблица 9.11). Поэтому рассмотренная схема (рисунок 9.40) может использоваться в качестве двухтактного синхронного RS-триггера.

Счетный Т-триггер. В нем используется только 4-я строка таблицы 9.13. Для этого входы J и K присоединяются к потенциалу, соответствующему логической единице: J=K=1 (рисунок 9.41, а).

|

а |

б |

|

Рисунок 9.41 | |

D-триггер.

В этом триггере

![]() ,

т.е. помимо тактового имеется только

один входD

(рисунок 9.41, б). Из таблицы 9.13 (2-я и 3-я

строки) видно, что в D-триггере Qt+1

= D, т.е.

последний запоминает сигнал на входе

D

в момент среза тактового импульса и

хранит его до следующего синхросигнала.

,

т.е. помимо тактового имеется только

один входD

(рисунок 9.41, б). Из таблицы 9.13 (2-я и 3-я

строки) видно, что в D-триггере Qt+1

= D, т.е.

последний запоминает сигнал на входе

D

в момент среза тактового импульса и

хранит его до следующего синхросигнала.