- •Мікропроцесорні системи зміст

- •2.1. Склад схем підтримки

- •2.2. Буферні регістри та шинні формувачі

- •2.3. Програмований паралельний інтерфейс 8255

- •5.3. Dsp сімейства tms320с1х

- •1. Однокристальні універсальні мікропроцесори

- •Класифікація мікропроцесорів (мп)

- •Восьмирозрядний мікропроцесор i8080

- •Восьмирозрядні мікропроцесори 8085 і z80

- •Шістнадцятирозрядний мікропроцесор 8086

- •Арифметичний співпроцесор 8087

- •Мікропроцесор Intel 8088

- •16-Розрядний мікропроцесор 80286

- •Мікропроцесор 80386

- •Арифметичні співпроцесори 80287 і 80387

- •Мікропроцесор 486 dx

- •Мікропроцесор Pentium

- •1.12 Мікропроцесор Pentium Pro, Pentium II

- •1.13. Мікропроцесор amd-k6

- •Оцінка продуктивності мп

- •2. Схеми підтримки. Контролери

- •2.1. Склад схем підтримки

- •2.2. Буферні регістри та шинні формувачі

- •2.3. Програмований паралельний інтерфейс 8255

- •2.4. Програмований послідовний інтерфейс 8251 (універсальний синхронно-асинхронний прийомо-передавач)

- •2.5. Програмований контролер переривання 8259а

- •2.6. Контролер прямого доступу до пам’яті 8237а

- •2.7. Інтервальний таймера 8254.

- •Сi – вхід лічильника;

- •2.8. Система реального часу

- •3. Процесори зі скороченою кількістю команд (risc-процесори)

- •3.1. Особливості risc-процесорів

- •3.2. Risc-процесор Alpha 21164 компанії dec

- •3.3. Risc-процесор PowerPc620

- •3.4. Risc-процесор mips-10000

- •3.5. Risc-процесор ра-8000

- •3.6. Risc-процесор UltraSparc іі

- •3.7. Risc-процесори UltraSparc ііі, UltraSparc іv

- •4.Системні ресурси та системні шини. Чипсети

- •4.1. Системні шини

- •4.2. Розподіл і організація пам'яті пк

- •4.3. Кеш пам’ять

- •4.4. Чипсети

- •Характеристика чипсетів

- •4.4.2. Чипсети серії 440

- •5. Цифрові сигнальні процесори (dsp)

- •5.1. Алгоритми обробки цифрової інформації та області застосування сигнальних процесорів

- •5.2. Особливості роботи сигнальних процесорів

- •5.3. Dsp сімейства tms320с1х

- •5.4. Сигнальні процесори сімейства tms320с2х

- •5.5. Процесори dsp сімейства tms320c5x

- •5.6. Сигнальні процесори tms320c2xx і 320с54х

- •5.7. Сигнальний процесор tms320с30

- •5.8. Сигнальні процесори сімейства tms320с4х

- •5.9. Сигнальні процесори сімейства tms320c8x

- •5.10. Процесор сімейства tms320c62xх

- •5.11. Dsp процесори сімейства tms320c67х

- •5.12. Сигнальні процесори dsp сімейства adsp21xx

- •5.13. Сигнальні процесори dsp сімейства аdsp 21ххх

- •6. Мультипроцесорні обчислювальні системи

- •6.1. Класифікація обчислюваних систем

- •6.2. Характеристика СуперЕом серії Cray

- •6.3. Системи з масовим паралелізмом

- •Закон Амдала

- •6.5. Закон Густафсона

- •6.6. Грід – система

- •6.6.1. Ресурси Грід

- •6.6.2. Архітектура Грід-систем

- •Протоколи глобального Гріда

Арифметичні співпроцесори 80287 і 80387

Математичний

співпроцесор 80287 призначений для

розширення функціональних можливостей

МП 80286, забезпечує можливості обробки

даних з плаваючою комою, двійково-десяткових

чисел і цілих чисел збільшеної довжини.

Функціонально він подібний співпроцесору

8087, але має можливість роботи як в

реальному, так і в захищеному режимі.

Співпроцесор 80287 виконує команди

паралельно з МП 80287. Всі режими адресації

пам'яті, фізична і віртуальна пам'ять

використовується аналогічно основному

процесору. На відміну від 8087 співпроцесора

287 співпроцесор не звертається до пам'яті

безпосередньо, залишаючи всі турботи

по адресації пам'яті основному процесору

286. Після апаратного скидання співпроцесор

встановлюється в реальний режим. У

режимі реальної адресації структура

80286/80287 повністю програмно сумісна з

8086/8087. Всі обміни даних відбуваються по

локальній шині даних і ініціюються

основним процесором за принципом ESCAPE.

Отримавши і декодувавши інструкцію,

співпроцесор виставляє свій запит PREQ,

отримавши який МП 286 виставляє сигнал

підтвердження

![]() .

Після закінчення пересилання даних МП

знімає сигнал

.

Після закінчення пересилання даних МП

знімає сигнал![]() .

.

Математичний співпроцесор призначений для розширення обчислювальних можливостей 32-розрядного основного процесора 386. Функціонально він нагадує співпроцесор 287. За рахунок поліпшення його архітектури підвищується продуктивність у порівнянні з 287. В режимах реальної адресації і віртуального 86МП-програми пари 80386/80387 повністю сумісні знизу вгору з програмами для систем 80286/80287. В захищеному режимі сумісні із захищеним режимом 80286/80287.

При проектуванні співпроцесора 80387 були внесені зміни з метою безпосередньої апаратної реалізації стандарту IЕЕЕ 754. У всіх мікропроцесорах починаючи з 486 співпроцесор інтегрований на кристал основного процесора.

Мікропроцесор 486 dx

Мікропроцесор 486 являє собою 32-розрядний процесор другого покоління, в якому на одному кристалі розташовуються сам процесор, математичний співпроцесор і кеш-пам'ять першого рівня L1. На чипі даного МП розташовується 1,2 млн. активних елементів, корпус МП має 168 виводів. У порівнянні з 386 МП даний процесор має ряд переваг:

в МП введений об'єднаний внутрішній кеш розміром 8Кб (для даних і команд) і передбачені засоби управління зовнішньою кеш-пам'яттю рівня L2.

на кристалі встановлений математичний співпроцесор, еквівалентний 387 МП.

Черга команд збільшена до 32Б.

Розширено засоби тестування, включені чотири додаткових регістра налагодження TR3, TR4, ТК5, ТК6.

У наступних моделях передбачається можливість підвищення тактової частоти: в 486DX2 в 3 рази, в 486DX4 в 2, 2.5 і 4 рази. УГЗ 486 МП представлено на рис. 1.21.

Рис. 1.21.

Де:

![]() –

двонаправлена шина даних

–

двонаправлена шина даних

![]()

![]() -

біти

паритету

байт

даних

-

біти

паритету

байт

даних

![]() –

шина адресу

–

шина адресу

![]()

![]() -

строб

даних

-

строб

даних

RST – скидання

C – синхронізація

HOLD – захоплення

AHOLD – захоплення адреси

![]() -

готовність

-

готовність

![]() -

перевід виводів МП в 3 стан

-

перевід виводів МП в 3 стан

![]() -

данні-управління

-

данні-управління

![]() -

запис-читання

-

запис-читання

LOCK – блокування шини

PLOCK – псевдо блокування (блокування данних, довжиною більше 32 біт)

![]() -

стан адреси

-

стан адреси

BREQ – запит шини

PWT – наскрізний запис сторінок в кеш-пам’ять

PCD – відсутність сторінки в кеш-пам’яті

![]() -

розширення пам’яті для кешування

-

розширення пам’яті для кешування

![]() -

доступ до кеш-пам’яті

-

доступ до кеш-пам’яті

![]() -

повне очищення кеш-пам’яті

-

повне очищення кеш-пам’яті

![]() -

остання передача пакетного режиму

-

остання передача пакетного режиму

![]() -

ігнорування помилки співпроцесора

-

ігнорування помилки співпроцесора

![]() -

дійсна адреса співпроцесора

-

дійсна адреса співпроцесора

![]() -

сигнал завершення пакетного шинного

циклу

-

сигнал завершення пакетного шинного

циклу

Структурна схема МП 486 приведена на рис. 1.22.

Рис. 1.22. Структурна схема МП 486

До складу 486-го МП входить операційне пристрій, що складається з процесора для обробки цілочисельних даних (подібного i386) і процесора для обробки чисел з плаваючою точкою (подібно співпроцесору i387).

Усередині кристала використовуються дві внутрішніх ШД (по 32 розряди).

До складу МП включена внутрішня об'єднана кеш-пам'ять з наскрізним записом ємністю 8 КБ.

Черга команд збільшена в 2 рази і становить 32 байта.

Дешифратор команд (ДК) за один такт дозволяє декодувати 1-7 байт команди.

Черга мікрокоманд відсутня.

Вихід дешифратора команд представляє собою адресу точки входу в відповідну мікропрограму.

Блок перетворення адреси подібний БПА мікропроцесора i386, тому й тут можливе використання чотирьох способів адресації. Структура кеш-пам'яті представлена на рис. 1.23.

Рис. 1.23. Структура кеш-пам’яті

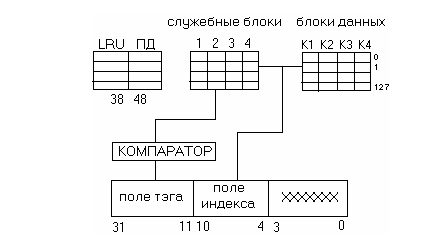

Вбудована кеш-пам'ять 486 МП представляє собою статичну RAM з часом звернення 30 нс. Вона розбита на рядки. Рядок містить 16 байт (і кожен рядок зберігає 4 подвійних слова). Загальна кількість рядків - 128. З кожним рядком пов'язана службова інформація-ТЕГ - інформація, яка має 21 розряд. Для кожного рядка є спеціальне поле достовірності (ПД) - 4 розряда, і поле алгоритму LRU (лінія найменшого опору - LRU) - 3 розряда. Інформація заноситься в кеш окремими пакетами по 16 байт (запис наскрізний).

Пошук інформації здійснюється наступним чином: 4 молодших розряди фізичної адреси вибирають відповідний блок даних довжиною 4 байти; 7 наступних розряди вибирають рядок і, відповідно, адресу відповідного тегу; 21 старший розряд називається полем Тега фізичної адреси. Якщо інформація цього поля збігається з обраним тегом з якимось рядком, вважається, що потрапили в кеш вдало - інформація з кеш буде зчитуватися. Якщо збігу немає - miss кеш (промахнулися) - інформація зчитується з ОП і дублюється в кеш. При цьому модифікують відповідні поля достовірності та алгоритму LRU.