- •Мікропроцесорні системи зміст

- •2.1. Склад схем підтримки

- •2.2. Буферні регістри та шинні формувачі

- •2.3. Програмований паралельний інтерфейс 8255

- •5.3. Dsp сімейства tms320с1х

- •1. Однокристальні універсальні мікропроцесори

- •Класифікація мікропроцесорів (мп)

- •Восьмирозрядний мікропроцесор i8080

- •Восьмирозрядні мікропроцесори 8085 і z80

- •Шістнадцятирозрядний мікропроцесор 8086

- •Арифметичний співпроцесор 8087

- •Мікропроцесор Intel 8088

- •16-Розрядний мікропроцесор 80286

- •Мікропроцесор 80386

- •Арифметичні співпроцесори 80287 і 80387

- •Мікропроцесор 486 dx

- •Мікропроцесор Pentium

- •1.12 Мікропроцесор Pentium Pro, Pentium II

- •1.13. Мікропроцесор amd-k6

- •Оцінка продуктивності мп

- •2. Схеми підтримки. Контролери

- •2.1. Склад схем підтримки

- •2.2. Буферні регістри та шинні формувачі

- •2.3. Програмований паралельний інтерфейс 8255

- •2.4. Програмований послідовний інтерфейс 8251 (універсальний синхронно-асинхронний прийомо-передавач)

- •2.5. Програмований контролер переривання 8259а

- •2.6. Контролер прямого доступу до пам’яті 8237а

- •2.7. Інтервальний таймера 8254.

- •Сi – вхід лічильника;

- •2.8. Система реального часу

- •3. Процесори зі скороченою кількістю команд (risc-процесори)

- •3.1. Особливості risc-процесорів

- •3.2. Risc-процесор Alpha 21164 компанії dec

- •3.3. Risc-процесор PowerPc620

- •3.4. Risc-процесор mips-10000

- •3.5. Risc-процесор ра-8000

- •3.6. Risc-процесор UltraSparc іі

- •3.7. Risc-процесори UltraSparc ііі, UltraSparc іv

- •4.Системні ресурси та системні шини. Чипсети

- •4.1. Системні шини

- •4.2. Розподіл і організація пам'яті пк

- •4.3. Кеш пам’ять

- •4.4. Чипсети

- •Характеристика чипсетів

- •4.4.2. Чипсети серії 440

- •5. Цифрові сигнальні процесори (dsp)

- •5.1. Алгоритми обробки цифрової інформації та області застосування сигнальних процесорів

- •5.2. Особливості роботи сигнальних процесорів

- •5.3. Dsp сімейства tms320с1х

- •5.4. Сигнальні процесори сімейства tms320с2х

- •5.5. Процесори dsp сімейства tms320c5x

- •5.6. Сигнальні процесори tms320c2xx і 320с54х

- •5.7. Сигнальний процесор tms320с30

- •5.8. Сигнальні процесори сімейства tms320с4х

- •5.9. Сигнальні процесори сімейства tms320c8x

- •5.10. Процесор сімейства tms320c62xх

- •5.11. Dsp процесори сімейства tms320c67х

- •5.12. Сигнальні процесори dsp сімейства adsp21xx

- •5.13. Сигнальні процесори dsp сімейства аdsp 21ххх

- •6. Мультипроцесорні обчислювальні системи

- •6.1. Класифікація обчислюваних систем

- •6.2. Характеристика СуперЕом серії Cray

- •6.3. Системи з масовим паралелізмом

- •Закон Амдала

- •6.5. Закон Густафсона

- •6.6. Грід – система

- •6.6.1. Ресурси Грід

- •6.6.2. Архітектура Грід-систем

- •Протоколи глобального Гріда

6.2. Характеристика СуперЕом серії Cray

Історія розвитку СуперЕОМ була почата з випуску ОС ІЛЛІАК-ІV, яка мала матричну структуру, була випущена в Університеті Ілінойса. Передбачалося, що в ній буде 1024 процесори, але в ній було тільки 256. Продуктивність:20 млн. операцій/хв.

У 1973 році Сеймур Крей організував компанію, у 1974 була випущена перша СуперЕОМ - CRAY-I. У ній вперше використовувалися команди "регістр-регістр"(Рис.6.9).

Рис.6.9. Структура суперкомп’ра Cray-1

Склад CRAY-I: ОП (від 1 до 4 мегаслів), великий набір процесорних регістрів, що складаються з групи векторних регістрів по 64 елементи, блок скалярних регістрів, блок адресних регістрів. Кожна група регістрів пов'язана зі своїм конвеєрним процесором

Дана система могла виконувати скалярні операції над векторними даними, над адресами, числами з плаваючою точкою (порядок - 15, мантиса - 49). У даній ОС використовуються команди завдовжки 16 або 32 розряди. У коротких команд 7 розрядів виділяється під код операції, 3 адресних поля по 3 розряди, визначали номер регістра для зберігання операндів. У довгих - 22 розряди для того, щоб можна було знайти операнд в загальному полі ОП. Один з регістрів визначає довжину вектора, другий - регістр маски.

У 1982 випускають CRAY-II, в якому тривалість циклу 4мс, ОП- 2ГБ, продуктивність - 250Мфлопс.

6.3. Системи з масовим паралелізмом

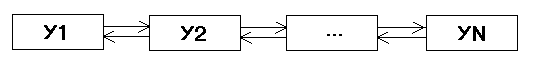

Ці системи відносяться, по класифікації Фліна, до систем типу MIMD і складають велику конкуренцію конвеєрно-векторним системам. Для створення таких систем, що складаються з декількох сотень зв'язаних процесорів, треба було вирішити ряд проблем, як в апаратних засобах, так і в програмних. Такі системи будуються з вузлів, які зв'язуються з сусідніми вузлами. До складу кожного вузла включаються процесор або група процесорів і власна пам'ять. Якщо використовується група процесорів, то в ній є векторні, скалярні і комутаційні процесори. Паралельні ОС будуються, використовуючи різні типи топологій. Найпростіша з них – лінійка (Рис.6.10).

Рис.6.10.

Недолік: максимальна довжина передачі повідомлень (діаметр системи) залежить від кількості процесорів, тому кількість тут обмежена.

Частіше використовують двовимірні грати, а ще краще – тор (Рис.6.11.).

Рис.6.11.

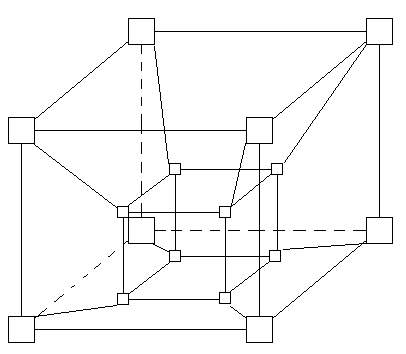

Найоптимальніша структура – n-мірний гіперкуб (Рис.6.12).

Рис.6.12.

Закон Амдала

Набуваючи для вирішення свого завдання паралельну обчислювальну систему, користувач розраховує на значне підвищення швидкості обчислень за рахунок розподілу обчислювального навантаження по безлічі паралельно працюючих процесорів. В ідеальному випадку система з n процесорів могла б прискорити обчислення в n разів. У реальності досягти такого показника з ряду причин не вдається. Головна з цих причин полягає в неможливості повного розпаралелювання жодної із задач. Як правило, в кожній програмі є фрагмент коду, який принципово повинен виконуватися послідовно і лише одним з процесорів. Це може бути частина програми, що відповідає за запуск задачі і розподіл розпаралельного коду по процесорах, або фрагмент програми, що забезпечує операції вводу/виводу. Можна привести і інші приклади, але головне полягає в тому, що про повне розпаралелювання задачі говорити не доводиться. Відомі проблеми виникають і з тією частиною задачі, яка піддається розпаралелюванню. Тут ідеальним був би варіант, коли паралельні гілки програми постійно завантажували б всі процесори системи, причому так, щоб навантаження на кожен процесор було однакове. На жаль, обидві ці умови на практиці важко реалізовуються. Таким чином, орієнтуючись на паралельну ОС, необхідно чітко усвідомлювати, що досягти прямо пропорційного числу процесорів збільшення продуктивності не вдасться, і, природно, встає питання про те, на яке реальне прискорення можна розраховувати. Відповідь на це питання в якійсь мірі дає закон Амдала.

Джин Амдал (Gene Amdahl) — один з розробників всесвітньо відомої системи IBM 360, в своїй роботі [48], опублікованій в 1967 році, запропонував формулу, що відображає залежність прискорення обчислень, що досягається на багатопроцесорній ОС, від числа процесорів і співвідношення між послідовною і паралельною частями програми. Показником скорочення часу обчислень служить така метрика, як «прискорення». Нагадаємо, що прискорення S — це відношення часу Ts, що витрачається на проведення обчислень на однопроцесорній ОС (у варіанті якнайкращого послідовного алгоритму), до часу Tp рішення тієї ж задачі на паралельній системі (при використанні якнайкращого паралельного алгоритму):

![]()

Обмовки щодо алгоритмів рішення задачі зроблені, щоб підкреслити той факт, що для послідовного і паралельного вирішення кращими можуть опинитися різні реалізації, а при оцінці прискорення необхідно виходити саме з якнайкращих алгоритмів.

Проблема розглядалася Амдалом в наступній постановці (Рис.6.13.). Перш за все, об'єм вирішуваної задачі із зміною числа процесорів, що беруть участь в її рішенні, залишається незмінним. Програмний код вирішуваної задачі складається з двох частин: послідовною і такою, що розпаралелює. Позначимо частку операцій, які повинні виконуватися послідовно одним з процесорів, через f,

де

![]() (тут частка розуміється не по числу

рядків коду, а по числу реально виконуваних

операцій). Звідси частка, що доводиться

на частину програми, що розпаралелює,

складе 1 -f.

Крайні випадки у значеннях віповідають

повністю паралельним (f

= 0) і повністю послідовним (f=1)

програмам. Частина програми, що

розпаралелюється, рівномірно розподіляється

по всіх процесорах.

(тут частка розуміється не по числу

рядків коду, а по числу реально виконуваних

операцій). Звідси частка, що доводиться

на частину програми, що розпаралелює,

складе 1 -f.

Крайні випадки у значеннях віповідають

повністю паралельним (f

= 0) і повністю послідовним (f=1)

програмам. Частина програми, що

розпаралелюється, рівномірно розподіляється

по всіх процесорах.

Рис.6.13. До постановки задачі в законі Амдала

З урахуванням приведеного формулювання маємо:

![]()

В результаті отримуємо формулу Амдала, що виражає прискорення, яке може бути досягнуте на системі з n процесорів:

![]()

Формула виражає просту і таку, що володіє великою спільністю залежність. Характер залежності прискорення від числа процесорів і частки послідовної частини програми показаний на рис.6.14.

Рис.6.14. Графіки залежності прискорення від: а — долі послідовних обчислень; б — числа процесорів

Якщо спрямувати число процесорів до нескінченності, то в границі отримуємо:

![]()

Це означає, що якщо у програмі 10% послідовних операцій (тобто f =0,1), то, скільки б процесорів не використовувалося, прискорення роботи програми більш ніж вдесятеро ніяк не отримати, да і то, 10 — це теоретична верхня оцінка самого кращого випадку, коли ніяких інших негативних чинників немає. Слід зазначити, що розпаралелювання веде до певних витрат, яких немає при послідовному виконанні програми. Як приклад таких витрат можна згадати додаткові операції, пов'язані з розподілом програм по процесорах, обмін інформацією між процесорами і так далі.