- •Триггеры с динамическим управлением

- •Триггеры с динамическим управлением

- •Триггеры с динамическим управлением22

- •Триггеры с динамическим управлением

- •Триггер со счетным входом. Т-

- •Триггер со счетным входом. Т-

- •Триггер со счетным входом. Т-

- •Функциональные блоки компьютера (прдлж).35 Регистры

- •Параллельно-последовательные регистры 45 (прдлж).

- •Выполнение поразрядных микроопераций в 50 регистрах

- •Логические операции OR и AND

- •Логические операции OR и AND (прдлж)

- •Логическая операция XOR

1

Классификация цифровых структур.

Информативным параметром сигналов в

цифровых устройствах являются интервалы времени, в пределах которых логическое состояние сигнала удерживается на уровне 1 или 0.

Информативным параметром сигналов в аналоговых устройствах является амплитуда сигнала в каждый момент времени.

Физика компьютеров 2011 Л.А.Золоторевич

2

Базовые логические элементы

Физика компьютеров 2011

Л.А.Золоторевич

3

Базовые

логические

элементы

Физика компьютеров 2011

Л.А.Золоторевич

4

Альтернативные

обозначения

элементов

Физика компьютеров 2011 Л.А.Золоторевич

|

|

|

|

Классификация цифровых структур. |

5 |

||

|

|||

Устройства комбинационного типа- это такие |

|

||

|

|

|

|

устройства, состояния выходов которых |

|

|

|

определяется состоянием входных сигналов в |

|

||

данный момент времени.

Комбинационная схема реализует систему из m булевых

функций, |

2,… |

входные |

переменные, |

,y2, |

. |

В вычислительной технике из всего множества комбинационных схем широко используются несколько типов, имеющих свои собственные названия: шифратор, дешифратор, мультиплексор, демультиплексор, комбинационный сумматор и т.д.

Вкомбинационной схеме значения функций зависят от одних

итех же переменных и комбинация значений переменных на выходах однозначно определена

комбинациейФизиказначенийкомпьютеровпеременных2011 на входах. При

реализации функций,Л.А.Золоторевичзависящих от одних и тех же

6

Устройства комбинационного типа

ПРИМЕРЫ:

Физика компьютеров 2011 Л.А.Золоторевич

7

Устройства последовательностного типа

Устройства последовательностного типа (иначе- устройства с обратными связями, или устройства с памятью)- это такие устройства, состояния выходов которых определяется не только состоянием входных сигналов в данный момент времени, но и от внутреннего состояния устройства, предистории входных состояний

ПРИМ |

|

|

Q |

|

|

1 |

|

||

|

1 |

|

||

R |

1 |

N |

||

1 |

||||

|

|

Q |

||

|

|

|

||

S |

|

|

|

Физика компьютеров 2011 Л.А.Золоторевич

|

|

|

|

|

|

8 |

Практическая реализация конечного |

||||||

автомата: |

|

|

|

|

||

Не устойчиваяx1 |

реализацияz1 |

|

|

|||

|

Тривиальный |

|

|

|

||

асинхроннойxk |

модели)zL |

|

|

|||

|

автомат – |

|

|

|

||

|

комбинационная |

|

|

|

||

y1 |

|

схема |

|

Y1 |

|

|

yM |

|

|

|

YM |

|

|

|

|

Рис |

|

|

|

|

x1 |

|

|

|

: |

z1 |

Для |

Устойчивая |

Т ривиальны й |

zL |

||||

xk |

|

автомат – |

|

|

||

обеспечения |

|

|

|

|

||

|

ком бинационная |

|

|

|||

y1 |

|

схем а |

|

Y 1 |

|

|

yM |

|

|

|

Y M |

|

|

|

|

|

|

устойчивости |

|

|

устройства |

|

|

|

|

||

|

|

Физика компьютеров 2011 |

|

|||

применяют синхронную модель. |

|

|||||

|

|

|

|

Л.А.Золоторевич |

|

|

9

Классификация элементов ЭВМ:

По своему назначению элементы делятся на:

–Логические

–Запоминающие

–Формирующие

К формирующим элементам относятся различные формирователи, усилители, усилители- формирователи и т.п.

Логические элементы преобразуют входные сигналы в соответствии с логическими функциями.

Запоминающим элементом называется элемент, который способен принимать и хранить код двоичной цифры (1 или 0).

Физика компьютеров 2011 Л.А.Золоторевич

10

Функциональные блоки компьютера. 1)Элементы памяти

По особенностям логического функционирования бывают

Триггеры с раздельной установкой состояний 0, 1.

Это RS – триггеры.

Триггеры задержки (защелки) с одним входом - D-

триггер.

Триггер с одним счетным входом - Т- триггер.Универсальные триггеры с раздельной установкой

состояний.

JK- триггер.

Комбинированные, в которых совмещаются

несколько типов.

Зачастую триггером называют последовательностную схему, в которой выходные сигналы изменяются только в моменты времени, задаваемые тактовым

сигналом. Физика компьютеров 2011

Последовательностную схему, выходы которой

Л.А.Золоторевич

11

Асинхронный RS-триггер (RS-защелка) на

логических элементах ИЛИ-НЕ

Асинхронный RS-триггер на логических элементах ИЛИ-НЕ (с прямыми входами) имеет следующее условное графическое обозначение, функционально логическую схему и функционирует согласно таблице состояний:

Разобраться, какая

таблица более точно отражает функционирование защелки!!!

Физика компьютеров 2011 Л.А.Золоторевич

12

Асинхронный RS-триггер (RS-защелка) на

логических элементах ИЛИ-НЕ (прдлж).

Перевод триггера в единичное состояние

путем воздействия на входы называется установкой – Set. Соответствующий вход

обозначают буквой S.

Перевод триггера в нулевое состояние

называется сбросом или гашением – Reset. Соответствующий вход обозначают буквой R.

Выход триггера Q называют прямым

выходом (условно). Состояние триггера связывают с состоянием данного выхода. Выход NQ называют инверсным выходом триггера.

Физика компьютеров 2011 Л.А.Золоторевич

13

Асинхронный RS-триггер (RS-защелка) на

логических элементах И-НЕ:

Асинхронный RS-триггер на логических элементах И-НЕ (с инверсными входами) имеет следующее условное графическое обозначение, функционально логическую схему и функционирует согласно таблице состояний:

Физика компьютеров 2011 Л.А.Золоторевич

14

Асинхронный D-триггер на логических

элементах И-НЕ

Асинхронный D-триггер (от англ. Delay-задержка) на логических элементах И-НЕ имеет один информационный вход (D-вход) и предназначен для задержки сигнала, поданного .

Физика компьютеров 2011 Л.А.Золоторевич

15

Синхронный RS-триггер (защелка) на

элементах И-НЕ

С(t) |

S(t) |

R(t) |

Q(t-1) |

NQ(t-1) |

Q(t) |

NQ(t) |

|

|

|

||||

|

|

|

|

|||

1 |

1 |

0 |

* |

* |

1 |

0 |

1 |

0 |

1 |

* |

* |

0 |

1 |

1 |

1 |

1 |

* |

* |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

X |

X |

0 |

* |

* |

1 |

0 |

1 |

0 |

0 |

* |

* |

1 |

1 |

X |

X |

0 |

* |

* |

0 |

1 |

0 |

1 |

Таблица

функциониров ания триггера, учитывающая возможность появления критических состязаний входных сигналов.

Физика компьютеров 2011 Л.А.Золоторевич

16

Синхронный RS-триггер (защелка) на

элементах И-НЕ

Таблица

функциониро

вания триггера, не учитывающа

я

возможность

появления

критических

состязаний

входных

сигналов.

Физика компьютеров 2011 Л.А.Золоторевич

17

Синхронный RS-триггер (защелка) на |

||||||||

|

|

|

|

|

|

|

|

|

элементах И-НЕ |

|

|

Q(t) |

NQ(t) |

|

|||

С(t) |

S(t) |

R(t) |

Q(t-1) |

NQ(t-1) |

|

|

Таблица |

|

|

|

|

|

|

функциониров |

|||

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

* |

|

* |

1 |

0 |

ания триггера, |

1 |

0 |

1 |

* |

|

* |

0 |

1 |

учитывающая |

1 |

1 |

1 |

* |

|

* |

1 |

1 |

возможность |

1 |

0 |

0 |

1 |

|

0 |

1 |

0 |

появления |

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

критических |

1 |

0 |

0 |

1 |

|

1 |

X |

X |

состязаний |

0 |

* |

* |

1 |

|

0 |

1 |

0 |

входных |

0 |

* |

* |

1 |

|

1 |

X |

X |

сигналов. |

|

|

|

|

|

|

|

|

Таблица |

0 |

* |

* |

0 |

|

1 |

0 |

1 |

функциониров |

|

|

|

|

|

|

|

|

ания триггера, |

|

|

|

|

|

|

|

|

не |

|

|

|

|

|

|

|

|

учитывающая |

|

|

|

|

|

|

|

|

возможность |

|

|

|

|

|

|

|

|

появления |

|

|

|

|

|

|

|

|

критических |

|

|

|

|

|

|

|

|

состязаний |

|

|

|

Физика компьютеров 2011 |

входных |

||||

|

|

|

сигналов. |

|||||

|

|

|

|

Л.А.Золоторевич |

|

|||

18

Синхронный RS-триггер (защелка) на

элементах И-НЕ

Хочу обратить ваше внимание на то, что любой триггер может быть реконструирован путем добавления комбинационной логики управления на его входах R и S. Пример такой схемы на основе синхронного RS – триггера. Здесь входы R и S триггера являются выходами соответствующих конъюнкторов и

поэтому |

|

дополнительными |

|

||

управляющими |

. |

|

|

|

|

Физика компьютеров 2011 Л.А.Золоторевич

19

Синхронный D-триггер (D-защелка) на элементах И-НЕ

Физика компьютеров 2011

Л.А.Золоторевич

Триггеры с динамическим управлением |

20 |

По способу управления синхронные триггеры |

|

делятся на |

|

Синхронные триггеры со статическим управлением

записью.

Триггеры этого типа принимают информационные сигналы все время пока действует синхросигнал. Вполне возможно многократное переключение триггера за время

действия синхросигнала. У таких триггеров вход С – статический.

Синхронные триггеры с динамическим управлением.

Триггер принимает информационные сигналы, которые

были на входах в момент перепада синхросигнала (на

переднем фронте – подъем -

0 1 или

В другие моменты

сигналы.

Таким образом, быть прямым

Физика компьютеров 2011 Л.А.Золоторевич

Триггеры с динамическим управлением |

21 |

|||

|

|

|||

|

Таким образом, вход динамического управления |

|

|

|

может быть прямым, когда триггер переключается |

|

|

||

во время переднего фронта сигнала синхронизации |

|

|

||

или инверсным: |

|

|

||

─ |

прямой – триггер реагирует на перепад |

|

|

|

|

тактового сигнала с “0” 1”, |

|

|

|

|

инверсный |

– триггер реагирует на перепад |

|

|

|

тактового |

|

|

|

|

|

|

|

|

Пример |

синхросигнал |

а |

Физика компьютеров 2011 |

Л.А.Золоторевич |

Триггеры с динамическим управлением22

По количеству каскадов триггеры

делятся на одноступенчатые и двухступенчатые.

В одноступенчатом триггере информация записывается за один такт. Поступление соответствующего сигнала разрешает переключение

в новое состояние.

Вдвухступенчатом триггере для записи информации требуется два такта работы схемы.

Двухступенчатые триггеры проектируются в виде

последовательного соединения двух триггеров с элементами синхронизации.

Запись в первую ступень производится с появлением синхроимпульса; вторая ступень в это время

закрыта.

Запись во вторую ступень из первой происходит по

следующемуФизикасигналукомпьютеровсинхронизации2011 .

Следовательно двухступенчатыеЛ.А.Золоторевич триггеры

23

Синхронный D-триггер на элементах И-НЕ, переключающийся по прямому входу (положительному фронту)

В данной схеме опрос входа D и изменение выходных сигналов происходит только в моменты времени, задаваемые нарастающим фронтом синхросигнала CLK. Первая защелка называется ведущей (master); при значении CLK, равном 0, она открыта и ее выходной сигнал повторяет входной сигнал D. Когда CLK становится равным 1, ведущая защелка запирается и ее выходной сигнал переписывается во вторую защелку, называемую «ведомой» (slave). Ведомая защелка открыта в течение всего времени, пока CLK равно 1, но изменение

в самом начале этого заперта и сигнал на ее на протяжении всего этого

отрезка времени.

Треугольник на УГО указывает на срабатывание

триггера по фронту |

|

сигнала и называется |

|

«указатель динамического |

|

входа» |

Физика компьютеров 2011 |

Л.А.Золоторевич |

|

Триггеры с динамическим управлением |

24 |

Синхронный D-триггер на элементах И-НЕ, переключающийся по прямому входу (положительному фронту) (прдлж)

Физика компьютеров 2011 Л.А.Золоторевич

25

Синхронный D-триггер на элементах И-НЕ,

переключающийся по положительному фронту (прдлж)

Заметим, что сигнал QM (выходной сигнал ведущей защелки) изменяется только при CLK, равном 0. Когда CLK становится равным 1, текущее значение QM записывается в ведомую

защелку , а изменение сигнала QM невозможно, пока

CLK опять не станет равным 0.

У D - триггера есть интервалы времени- время

установки и время удержания, - в течение

которых информационный сигнал на входе D не должен изменяться. Этот интервал находится в

окрестности переключающего фронта сигнала CLK. Время установки- это интервал времени между приходом

информационного сигнала на вход D триггера и временем поступления разрешающего сигнала синхронизации. Время

удержания – это интервал времени от прихода

Физика компьютеров 2011

разрешающего сигналаЛ.А.Золоторевичсинхрон зации до возможного

26

Синхронный D-триггер на элементах И-НЕ,

переключающийся по отрицательному фронту

Физика компьютеров 2011 Л.А.Золоторевич

Триггер со счетным входом. Т- |

27 |

Характерная особенность T- триггера: |

|

Имеет один информационный вход.

Переключается в противоположное состояние с приходом каждого очередного входного импульса (Т=1). То есть при Т=0 триггер сохраняет свое состояние. При Т=1 изменяет

свое состояние. |

|

|

||

Таблица переходов T- |

|

|||

триггера |

Состояние |

|

||

Входные |

Состояние |

Режим |

||

сигналы T |

Q(t) |

Q(t+1) |

||

|

||||

0 |

0 |

0 |

Хранение |

|

0 |

1 |

1 |

||

|

||||

1 |

1 |

0 |

Инверсия |

|

1 |

0 |

1 |

||

|

||||

Отсюда легко получить характеристическое уравнение

Т-триггера. Физика компьютеров 2011

Q(t+1) = Q(t)Л.А.*Золоторевич^T(t) + ^Q(t) * T(t) = Q(t)

Триггер со счетным входом. Т- |

28 |

||

Одноступенчатый асинхронный Т-триггер |

|

||

Т-триггер на RS - |

Условное |

Т-триггер на |

|

триггере |

обозначение |

D - триггере |

|

Временные диаграммы |

|

|

|

|

|

Второе |

|

|

|

название |

|

|

|

Т- |

|

|

|

триггера – |

|

Физика компьютеров 2011 |

делитель |

|

|

|

Л.А.Золоторевич |

частоты |

|

Триггер со счетным входом. Т- |

29 |

На практике схемы одноступенчатых триггеров не нашли широкого применения.

Основной недостаток – это ненадежность

выходного состояния.

Какой выход?

Вводят вторую ступень.

Уменьшают скважность управляющего сигнала, и вход статический заменяют на вход динамический.

Физика компьютеров 2011 Л.А.Золоторевич

30

Асинхронный Т-триггер на RS-триггерах на

элементах И-НЕ

Т-триггер может быть построен на элементах И-НЕ с |

|

использованием двух RS-триггеров на элементах И-НЕ, |

|

первый T1 из которых служит элементом задержки для |

|

обеспечения надежности |

|

выполняет роль Т-входа, |

. |

перекрестными |

Физика компьютеров 2011 Л.А.Золоторевич

31

Синхронный Т-триггер на элементах И-НЕ

Синхронный Т-триггер отличается от асинхронного Т- триггера наличием С-входа для синхронизирующего сигнала, который подается через элементы И-НЕ1, И-

НЕ2 на первый RS-триггер. Синхронный Т-триггер

имеет следующее условное графическое обозначение, функционально логическую состояний входов-выходов:

Физика компьютеров 2011 Л.А.Золоторевич

32

Асинхронный JK-триггер на элементах И-НЕ

Асинхронный JK-триггер отличается от асинхронного T-триггера наличием двух информационных входов J и K (вместо T-входа), где вход J эквивалентен входу S, а вход K - входу R, и функционирует в соответствии с таблицей состояний RS-триггера. При условии J(t)=K(t)=1 JK-триггер изменяет свое состояние на противоположное, т.к. работает в режиме T-триггера. Таким образом, JK-

триггер отличается запрещенных

.

Физика компьютеров 2011 Л.А.Золоторевич

33

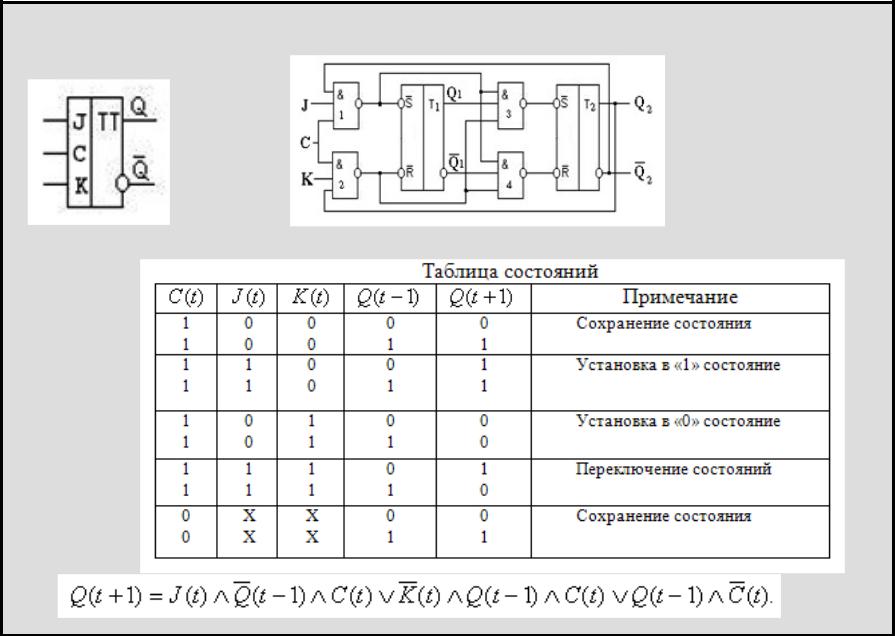

Синхронный JK-триггер на элементах И-НЕ

Физика компьютеров 2011 Л.А.Золоторевич

34

Особенность JK-триггера

JK-триггер является универсальным, т.к. на его основе с помощью внешних соединений выводов схемы можно получить триггеры других видов, RS-, D-, T- триггеры и др.

JK-триггер будет работать как RS

если наложить ограничения на комбинацию входных сигналов J(t)=K(t)=1 (эта комбинация не должна появляться на входах триггера).

JK-триггер будет работать как D-триггер,

если его вход J(t) подключить через инвертор ко входу K(t). В этом случае вход J(t) выполняет функцию входа D(t), а

схема реализует |

состояний D-триггера. |

T-триггер |

условии объединения входов |

|

|

J(t) и K(t): |

|

Физика компьютеров 2011

JK-триггеры находят применениеЛ.А.Золоторевичпри построении счетных