- •Кафедра программного обеспечения информационных технологий

- •ТЕМА 1

- •1.1 Введение в операционные системы

- •1.1.1 Понятие операционной системы

- •1.1.2 Поколения ОС

- •1.1.3 Функции и свойства ОС

- •1.1.4 Характеристики современных ОС

- •1.1.5 Архитектура микроядра

- •1.1.6 Многопоточность

- •1.1.7 Симметричная многопроцессорность

- •1.1.8 Распределенные ОС

- •1.1.9 Объектно-ориентированный дизайн

- •1.1.10 Концепция ОС на основе микроядра

- •1.1.11 Принципы построения ОС

- •ТЕМА 2

- •2.1 Основы операционных систем

- •2.1.1 Понятие процесса

- •2.1.2 Понятие ресурса

- •2.1.3 Концепция виртуализации

- •2.1.5 Дисциплины распределения ресурсов

- •2.1.6 Концепция прерывания

- •ТЕМА 3

- •3.1 Процессы

- •3.1.1 Состояние процессов

- •3.1.2 Описание процессов

- •3.1.2.1 Структуры управления процессами

- •3.1.2.2 Управление процессами

- •3.1.3 Концепция потока как составной части процесса

- •3.1.4 Многопоточность

- •3.1.5 Однопоточная модель процесса

- •3.1.6 Многопоточная модель процесса

- •3.1.7 Функциональность потоков

- •3.1.8 Взаимодействие процессов

- •3.1.8.1 Задача взаимного исключения

- •3.1.8.2 Обобщенная задача взаимного исключения

- •3.1.9 Синхронизирующие примитивы (семафоры). Применение семафоров для решения задачи взаимного исключения

- •3.1.10 Задача “производитель-потребитель”

- •3.1.10.1 Общие семафоры

- •3.1.10.2 Задача “производитель-потребитель”, буфер неограниченного размера

- •3.1.10.3 Задача “производитель-потребитель”, буфер ограниченного размера

- •3.1.11 Взаимодействие через переменные состояния

- •3.1.12 Монитороподобные средства синхронизации

- •3.1.12.1 Введение

- •3.1.12.2 Механизм типа «критическая область»

- •3.1.12.3 Механизм типа «условная критическая область»

- •3.1.12.4 Вторая модификация механизма «критическая область» (модификация второго рода)

- •ТЕМА 4

- •4.1 Ресурсы

- •4.1.1 Распределение ресурсов. Проблема тупиков

- •4.1.2 Алгоритм банкира

- •4.1.3 Применение алгоритма банкира

- •ТЕМА 5

- •5.1 Память. Управление памятью

- •5.1.1 Требования к управлению памятью

- •5.1.2 Схемы распределения памяти

- •5.1.3 Система двойников при распределении памяти

- •ТЕМА 6

- •6.1 Организация виртуальной памяти

- •6.1.1 Структуризация адресного пространства виртуальной памяти

- •6.1.2 Задачи управления виртуальной памятью

- •6.1.2.1 Задача размещения

- •6.1.2.2 Задача перемещения

- •6.1.2.3 Задача преобразования

- •6.1.2.4 Задача замещения

- •ТЕМА 7

- •7.1 Планирование в операционных системах

- •7.1 Типы планирования процессора

- •7.2 Алгоритмы плинирования

- •7.3 Традиционное планирование в Unix

- •ТЕМА 8

- •8.1 Управление вводом-выводом и файлами

- •8.1.2 Развитие функций ввода-вывода

- •8.1.3 Управление ОС и устройствами ввода-вывода

- •8.1.4 Модели организации ввода-вывода

- •ТЕМА 9

- •9.1.1 Сегментация памяти

- •9.1.1.1 Сегментация памяти в процессорах 8086

- •9.1.1.3 Дескриптор сегмента

- •9.1.1.4 Дескрипторные таблицы

- •9.1.1.5 Селекторы сегментов в защищенном режиме

- •9.1.1.6 Локальные дескрипторные таблицы

- •9.1.1.7 Особенности сегментации

- •9.1.2 Страничная организация памяти

- •9.1.2.1 Страничный дескриптор

- •9.1.2.2 Разрешение и запрещение страничного преобразования

- •9.1.3 Организация защиты при работе процессора в защищенном режиме

- •9.1.3.1 Привилегированные команды

- •9.1.3.2 Защита доступа к данным

- •DPL- Descriptor Privilege Level

- •9.1.3.3 Защита сегмента кода

- •9.1.3.4 Определение текущего уровня привилегий

- •9.1.3.5 Передача управления между уровнями привилегий

- •9.1.3.6 Подчиненные сегменты

- •9.1.3.7 Шлюзы вызова

- •9.1.4 Поддержка многозадачности в процессорах архитектуры IA-32

- •9.1.4.1 Сегмент состояния задачи

- •9.1.4.2 Дескриптор сегмента TSS

- •9.1.4.3 Сегмент состояния задач TSS

- •9.1.4.4 События, которые могут вызвать переключение задачи

- •9.1.4.5 Формат шлюза задач

- •9.1.4.7 Особые случаи при переключении задач

- •9.1.4.8 Вложенность задач

- •9.1.4.9 Двоичная карта разрешения ввода-вывода

- •9.1.5 Прерывания и особые случаи

- •9.1.5.1 Прерывания и особые случаи в процессоре 8086

- •9.1.5.2 Прерывания в защищенном режиме

- •9.1.5.3 Дескрипторная таблица прерываний

- •9.1.5.4 Шлюз ловушки

- •9.1.5.5 Шлюз прерывания

- •9.1.5.6 Шлюз задачи

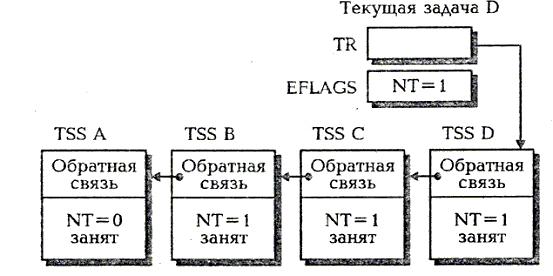

Когда переключение задач инициируется командой far call, аппаратным прерыванием или особым случаем, задача, на которую инициируется переключение, считается вложенной в ту задачу, из которой произошло переключение. Это похоже на вызов подпрограмм.

Когда вложенная задача выполнила команду iret, процессор автоматически переключается на прерванную задачу. Глубина вложенности не ограничивается.

В качестве механизма связи вложенных задач используется поле обратной связи в сегменте TSS, в котором сохраняется старое содержимое регистра задачи. Кроме того, процессор устанавливает в единицу бит вложенной задачи NT в регистре EFLAGS , который свидетельствует о том, поле обратной связи содержит информативное значение.

Рис. 9.18. Цепь из трех вложенных задач

Переключение на задачу А было проведено с помощью команды far jmp, т.к. бит NT=0, а далее эта задача вызвала следующую с помощью команды far call. Биты вложенности устанавливается в 1, а поле обратной связи указывает на предыдущую задачу. Но для всех этих задач остается включенным бит занятости в дескрипторе сегмента TSS.

Фактически вложенность задач учитывает только команда IRET, обычная команда возврата из подпрограммы RET вложенности не учитывает.

9.1.4.9 Двоичная карта разрешения ввода-вывода

Последнее 16-битное слово в базовом TSS содержит смещение начала двоичной карты разрешения ввода-вывода. Она является дополнительным средством механизма защиты по привилегиям. Такая карта создается для каждой задачи и участвует в контроле привилегии команд ввода-вывода.

В двоичной карте каждый бит соответствует одному адресу ввода-вывода, то есть байтному порту ввода-вывода. Младший бит первого байта карты отно-

139