- •Кафедра программного обеспечения информационных технологий

- •ТЕМА 1

- •1.1 Введение в операционные системы

- •1.1.1 Понятие операционной системы

- •1.1.2 Поколения ОС

- •1.1.3 Функции и свойства ОС

- •1.1.4 Характеристики современных ОС

- •1.1.5 Архитектура микроядра

- •1.1.6 Многопоточность

- •1.1.7 Симметричная многопроцессорность

- •1.1.8 Распределенные ОС

- •1.1.9 Объектно-ориентированный дизайн

- •1.1.10 Концепция ОС на основе микроядра

- •1.1.11 Принципы построения ОС

- •ТЕМА 2

- •2.1 Основы операционных систем

- •2.1.1 Понятие процесса

- •2.1.2 Понятие ресурса

- •2.1.3 Концепция виртуализации

- •2.1.5 Дисциплины распределения ресурсов

- •2.1.6 Концепция прерывания

- •ТЕМА 3

- •3.1 Процессы

- •3.1.1 Состояние процессов

- •3.1.2 Описание процессов

- •3.1.2.1 Структуры управления процессами

- •3.1.2.2 Управление процессами

- •3.1.3 Концепция потока как составной части процесса

- •3.1.4 Многопоточность

- •3.1.5 Однопоточная модель процесса

- •3.1.6 Многопоточная модель процесса

- •3.1.7 Функциональность потоков

- •3.1.8 Взаимодействие процессов

- •3.1.8.1 Задача взаимного исключения

- •3.1.8.2 Обобщенная задача взаимного исключения

- •3.1.9 Синхронизирующие примитивы (семафоры). Применение семафоров для решения задачи взаимного исключения

- •3.1.10 Задача “производитель-потребитель”

- •3.1.10.1 Общие семафоры

- •3.1.10.2 Задача “производитель-потребитель”, буфер неограниченного размера

- •3.1.10.3 Задача “производитель-потребитель”, буфер ограниченного размера

- •3.1.11 Взаимодействие через переменные состояния

- •3.1.12 Монитороподобные средства синхронизации

- •3.1.12.1 Введение

- •3.1.12.2 Механизм типа «критическая область»

- •3.1.12.3 Механизм типа «условная критическая область»

- •3.1.12.4 Вторая модификация механизма «критическая область» (модификация второго рода)

- •ТЕМА 4

- •4.1 Ресурсы

- •4.1.1 Распределение ресурсов. Проблема тупиков

- •4.1.2 Алгоритм банкира

- •4.1.3 Применение алгоритма банкира

- •ТЕМА 5

- •5.1 Память. Управление памятью

- •5.1.1 Требования к управлению памятью

- •5.1.2 Схемы распределения памяти

- •5.1.3 Система двойников при распределении памяти

- •ТЕМА 6

- •6.1 Организация виртуальной памяти

- •6.1.1 Структуризация адресного пространства виртуальной памяти

- •6.1.2 Задачи управления виртуальной памятью

- •6.1.2.1 Задача размещения

- •6.1.2.2 Задача перемещения

- •6.1.2.3 Задача преобразования

- •6.1.2.4 Задача замещения

- •ТЕМА 7

- •7.1 Планирование в операционных системах

- •7.1 Типы планирования процессора

- •7.2 Алгоритмы плинирования

- •7.3 Традиционное планирование в Unix

- •ТЕМА 8

- •8.1 Управление вводом-выводом и файлами

- •8.1.2 Развитие функций ввода-вывода

- •8.1.3 Управление ОС и устройствами ввода-вывода

- •8.1.4 Модели организации ввода-вывода

- •ТЕМА 9

- •9.1.1 Сегментация памяти

- •9.1.1.1 Сегментация памяти в процессорах 8086

- •9.1.1.3 Дескриптор сегмента

- •9.1.1.4 Дескрипторные таблицы

- •9.1.1.5 Селекторы сегментов в защищенном режиме

- •9.1.1.6 Локальные дескрипторные таблицы

- •9.1.1.7 Особенности сегментации

- •9.1.2 Страничная организация памяти

- •9.1.2.1 Страничный дескриптор

- •9.1.2.2 Разрешение и запрещение страничного преобразования

- •9.1.3 Организация защиты при работе процессора в защищенном режиме

- •9.1.3.1 Привилегированные команды

- •9.1.3.2 Защита доступа к данным

- •DPL- Descriptor Privilege Level

- •9.1.3.3 Защита сегмента кода

- •9.1.3.4 Определение текущего уровня привилегий

- •9.1.3.5 Передача управления между уровнями привилегий

- •9.1.3.6 Подчиненные сегменты

- •9.1.3.7 Шлюзы вызова

- •9.1.4 Поддержка многозадачности в процессорах архитектуры IA-32

- •9.1.4.1 Сегмент состояния задачи

- •9.1.4.2 Дескриптор сегмента TSS

- •9.1.4.3 Сегмент состояния задач TSS

- •9.1.4.4 События, которые могут вызвать переключение задачи

- •9.1.4.5 Формат шлюза задач

- •9.1.4.7 Особые случаи при переключении задач

- •9.1.4.8 Вложенность задач

- •9.1.4.9 Двоичная карта разрешения ввода-вывода

- •9.1.5 Прерывания и особые случаи

- •9.1.5.1 Прерывания и особые случаи в процессоре 8086

- •9.1.5.2 Прерывания в защищенном режиме

- •9.1.5.3 Дескрипторная таблица прерываний

- •9.1.5.4 Шлюз ловушки

- •9.1.5.5 Шлюз прерывания

- •9.1.5.6 Шлюз задачи

сегменты, где хранятся локальные таблицы, заносятся в GDT, то для локализации или определения используемой в текущий момент времени LDT, необходим только селектор. И для его хранения в процессоре используется 16-битный регистр LDTR. Поле предела занимает 20 бит, поэтому можно создать таблицу более 64 килобайт. Но на практике этого не требуется. В дескрипторе также задействован бит присутствия, и процессор не разрешает загрузить в регистр LDTR селектор, не присутствующий в LDT, генерируется особый случай неприсутствия.

Для начала работы с LDT в регистр LDTR помещается селектор выбираемой таблицы. При попытке загрузить в селектор недопустимое значение процессор формирует общее нарушение защиты. Допускается загрузка в LDTR пустого селектора. Нулевой селектор означает, что таблица LDT не используется.

К LDI обращение на прямую не допускается.

Дескриптор таблицы LDTR подобен общей структуре дескриптора.

63 |

55 |

|

|

|

|

47 |

|

S |

39 |

|

|

|

|

32 |

|

||||||||

Базовый адрес |

0 0 0 0 |

Предел |

|

|

P |

DPL |

0 |

Тип |

|

|

|

Базовый |

|

||||||||||

31-24 |

|

|

|

|

|

19-16 |

|

|

|

|

|

|

0 |

0 |

|

1 |

|

0 |

|

адрес 23-16 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

31 |

23 |

|

|

|

15 |

|

|

|

|

|

|

|

|

|

|

7 |

|

0 |

|||||

Базовый адрес |

|

|

|

|

Предел |

|

|

|

|

|

|||||||||||||

|

15-0 |

|

|

|

|

|

|

|

15-0 |

|

|

|

|

|

|

|

|

|

|

|

|||

Рис. 9.8. Формат дескриптора таблицы LDT

9.1.1.7 Особенности сегментации

Разрешается создание сегментов, в которых допускаются операции только считывания, только исполнения, сегменты считывания - записи, сегменты исполнения - считывания. Не предусмотрено создания сегментов для всех трех функций. Однако путем перекрытия сегментов или введения дескрипторов с альтернативными наименованиями позволяют определять участки памяти, по отношению к которым можно выполнять все эти 3 действия одновременно. CPU обеспечивает мощные средства для сегментации памяти (защита, фиксация недопустимых операций и т.д.)

9.1.2 Страничная организация памяти

118

Внутреннее устройство управления памяти в процессоре, наряду с обязательной сегментацией, реализует еще один уровень косвенности в формировании физического адреса памяти. Это страничная организация памяти.

Основной причиной применения страничного преобразования является возможность реализации виртуальной памяти, которая позволяет программисту использовать объем памяти больше чем размер физической ОП.

Страничное преобразование было реализовано и до процессоров INTEL, но здесь оно реализовано как внутреннее устройство. В связи с этим появился ряд преимуществ:

-сокращается загрузка внешней шины;

-гарантируется правильность взаимодействия процессора и страничного устройства управления памятью;

-стандартизируются средства поддержки ОС виртуальной памяти;

-допускается программное разрешение и запрещение страничного преобразования адреса;

-снижается общая стоимость системы.

Если при сегментации базовым объектом памяти является сегмент практически любого размера, то при страничной организации базовым объектом памяти является блок с фиксированным размером 4 kb, который называется страницей. При линейном адресном пространстве 4 Gb получается 1 MB страниц. Реальная физическая память меньше 4 Gb, следовательно, при выполнении программы в любой момент времени только часть страниц будет присутствовать в ОП. Такой подход в организации памяти называется виртуальной памятью. Страницы, которые не поместились в ОП, располагаются на внешней памяти.

Фиксированный размер всех страниц позволяет загрузить любую виртуальную страницу в любую физическую страницу. Это и объясняет применение страничного преобразования в случае виртуальной памяти.

Понятие виртуальной памяти с заменой страниц по требованию подчёркивает тот факт, что прикладная программа не касается процесса страничного преобразования памяти и может использовать всё доступное адресное пространство.

Процессор автоматически формирует особый случай не присутствия, если обращение идёт к странице, отсутствующей в физической памяти. При возникновении этого особого случая ОС автоматически загружает затребованную страницу из внешней памяти.

Вобщем случае сегменты не являются кратными размеру страницы. Но рекомендуется выравнивать небольшие сегменты так, чтобы они полностью находились внутри одной страницы.

Впроцессе страничного преобразования старшие 20 бит 32-битного линейного адреса замещаются другим 20-битным значением, задающим адрес физической страницы.

Для такого преобразования используются таблицы страниц. В процессорах реализуется двухэтапное преобразование линейного адреса в физический. Можно реализовать и одноэтапное преобразование, но тогда для одной таблицы

119

страниц нужно 4 Мб. Поэтому целесообразнее использование двухэтапного преобразования.

Таблицы

страниц

|

|

|

|

|

|

Физическая |

|

|

|

|

|

|

память |

Каталог |

|

|

|

|

|

|

страниц |

|

|

|

|

|

|

31 |

0 |

|

|

31 … |

0 |

Страничный |

|

|

1023 |

|

|

|

кадр |

|

. . . |

|

|

. . . |

|

Байт |

|

PDE |

|

|

PTE |

|

|

|

. . . |

|

|

. . . |

|

|

|

|

0 |

|

|

0 |

0 |

19 |

0 |

|

|

|

|

|

PDBR |

|

Каталог |

Таблица |

Смещение |

||

CR3 |

|

31 |

22 21 |

12 11 |

0 |

|

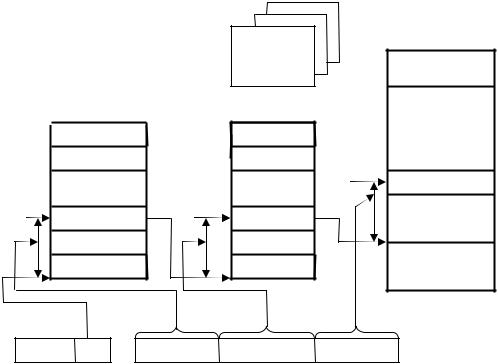

Рис. 9.9. Двухэтапное преобразование линейного адреса в физический

PDE – Page Directory Entry.

PTE – Page Table Entry.

PDBR – Page Directory Base Register.

Основой страничного преобразования является регистр CR3, который содержит 20-битный физический адрес каталога страниц в текущей задаче, и называется регистром базового адреса каталога страниц (PDBR). Это единственный внутренний регистр процессора, который содержит физический адрес памяти. Младшие 12 бит считаются нулевыми, т.е. каталог выровнен на границу страницы.

Предполагается, что каталог страниц всегда находится в памяти и не участвует в свопинге.

Каталог страниц содержит 1024 32-битных дескриптора, называемых элементами каталога страниц. Каждый из этих элементов адресует подчинённую таблицу страниц второго уровня. В свою очередь, каждая из этих страниц содержит 1024 32-битных дескриптора элементов таблицы страниц, а каждый из этих элементов адресует страничный кадр в физической памяти.

120

Преобразование линейного адреса в физический состоит из следующих действий.

1.Старшие 10 бит линейного адреса дополняются двумя младшими нулями и служат индексом каталога страниц, выбирая один из элементов в каталоге. Выбранный элемент каталога страниц определяет 20-ти битный адрес таблицы страниц.

2.Средние 10 бит линейного адреса дополняются двумя младшими нулями

ииндексируют таблицу страниц, выбирая из нее PTE. Этот элемент содержит 20-ти битный базовый адрес страничного кадра в физической памяти.

3.Базовый адрес страничного кадра объединяется с младшими 12-ю битами линейного адреса. В результате получается 32-х битный физический адрес памяти, по которому и производится обращение.

При обращении к элементам каталога и таблицы страниц, производится проверка защиты и присутствия страниц в памяти.

Структура элемента каталога страницы и таблицы страниц одинакова и имеет вид.

|

31 |

12 |

11 |

9 |

0 |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

P |

P |

U |

R |

P |

|

|

Адрес страничного кадра |

|

|

Дост. |

0 0 |

DA |

|

||||||||

|

|

|

C |

W |

/ |

/ |

|

||||||||

|

|

|

|

|

|

|

|

|

|

D T |

S |

W |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 9.10. Формат элемента таблицы страниц

A – Accessed

D – Dirty

PWT – Page Write Through

PCD – Page Cache Disable

В каждом элементе страниц хранится адрес страничного кадра. В этом поле находится физический базовый адрес страницы, младшие 12 бит адреса считаются нулевыми (выравниваются на границу страницы), биты 9, 10, 11 процессор не использует, и они могут использоваться при разработке операционных систем.

Бит присутствия Р показывает, отображается ли адрес страничного кадра на страницу в физической памяти. Если Р = 1, то страница находится в памяти.

Бит пользовательский или системный U/S определяет права доступа, т. е. уровни привилегий.

Бит обращения А и бит D содержат информацию об использовании страницы. Бит D сообщает об обращении к таблице для записи, а бит А сообщает об

121