- •1 КЛЮЧИ

- •1.1 Контактные ключи

- •1.2 Диодные ключи

- •1.3 Транзисторные ключи

- •1.3.1 Ключи на биполярных транзисторах

- •1.3.2 Характеристики биполярных транзисторов в ключевых режимах

- •1.3.3 Ключи на униполярных транзисторах

- •1.3.4 Транзисторы типа MOSFET

- •1.3.5 Транзисторы IGBT

- •1.4 Интеллектуальные ключи

- •1.5 Ключи на тиристорах

- •1.6 Переходные процессы в ключах на биполярных транзисторах

- •1.7 Переходные процессы в ключах на униполярных транзисторах

- •1.8 Потери в ключах в импульсном режиме

- •1.9 Способы повышения быстродействия ключей на биполярных транзисторах

- •1.10 Выходные ключевые каскады

- •1.11 Сквозные токи

- •1.14 Тиристорные схемы управления

- •1.15 Тиристорная схема управления двигателем постоянного тока от сети переменного тока

- •1.16 Тиристорная схема управления двигателем постоянного тока от сети постоянного тока

- •2 ЛОГИЧЕСКИЕ СХЕМЫ

- •2.1 Основные определения

- •2.2 Диодные логические схемы

- •2.3 ТТЛ логические схемы

- •2.4 Особенности 530, 531, 533, 555 серий

- •2.5 Станковая логика. 511 серия

- •2.6 Логика на униполярных транзисторах

- •2.7 Логика с оптическими связями

- •2.8 Эмиттерно–связная логика (ЭСЛ)

- •2.9 Интегральная инжекционная логика

- •2.10 Логика ПТШ (полевые транзисторы Шоттки)

- •2.11 Согласование логических схем

- •2.12 Программируемые логические интегральные схемы (ПЛИС)

- •2.13 Обобщенная модель ПЛИС

- •2.14 Микросхема ПЛМ (К556 РТ 1)

- •3 ТРИГГЕРЫ

- •3.1 Триггеры на биполярных транзисторах

- •3.2 Счетный триггер

- •3.3 Триггеры на униполярных транзисторах

- •3.4 Триггеры на логических элементах

- •3.5 Синхронный RS-триггер

- •3.6 Счетный триггер на логических элементах

- •3.7 D-триггер на логических элементах

- •3.8 JK-триггер на логических элементах

- •3.9 Интегральный шестиэлементный D-триггер ТМ2

- •3.12 Гонки

- •3.13 Триггеры на приборах с отрицательным сопротивлением. Триггеры на туннельных диодах.

- •3.14 Триггеры на тиристорах

- •3.16 Триггеры на операционных усилителях

- •4 Генераторы импульсов

- •4.1 Мультивибраторы на биполярных транзисторах

- •4.1.1 Мультивибраторы в ждущем режиме

- •4.1.2 Мультивибраторы на биполярных транзисторах в автоколебательном режиме

- •4.2 Ждущий мультивибратор на униполярных транзисторах

- •4.3 Генератор импульсов на двух логических элементах с двумя конденсаторами в автоколебательном режиме

- •4.4 Генератор импульсов на четырех логических элементах с одним конденсатором

- •4.5 Генератор импульсов на двух логических элементах с одним конденсатором

- •4.6 Генераторы импульсов на логических элементах в ждущем режиме

- •4.7 Генератор импульсов на туннельном диоде в ждущем режиме

- •4.8 Генератор импульсов на туннельном диоде в автоколебательном режиме.

- •4.9 Генератор импульсов на тиристоре в ждущем режиме

- •4.12 Генератор импульсов в ждущем режиме на таймере

- •4.15 Блокинг-генератор в автоколебательном режиме

- •4.16 Магнитно-транзисторный преобразователь двухплечевой

- •4.17 Схема с дополнительным трансформатором

- •4.18 Мостовая и полумостовая схемы магнитно-транзисторных преобразователей

- •4.19 Генераторы импульсов на ОУ в автоколебательном режиме

- •4.20 Генератор импульсов на ОУ в ждущем режиме

- •4.21 Кварцевая стабилизация импульсных генераторов

- •4.22 Генератор импульсов, стабилизированный кварцем

- •5 Генераторы синусоидальных колебаний

- •5.1 Общие определения

- •5.2 Генератор синусоидальных колебаний с LC контуром и трансформаторной ОС

- •5.3 Схемы с индуктивной, емкостной трехточками

- •5.4 RC цепи для генераторов синусоидальных колебаний

- •5.6 Генераторы синусоидальных колебаний с кварцевой стабилизацией

- •5.7 Генераторы синусоидальных колебаний на ОУ

- •6 Цифроаналоговые и аналого-цифровые преобразователи

- •6.1 Цифроаналоговые преобразователи

- •6.1.1 ЦАП с весовыми резисторами

- •6.1.3 ЦАП с сигма–дельта модуляцией

- •6.1.4 ЦАП с прямым преобразованием

- •6.2.1 Следящие АЦП

- •6.2.2 Развертывающие АЦП

- •6.2.3 АЦП с регистром последовательного приближения

- •6.2.4 АЦП с двойным интегрированием

- •6.2.5 АЦП параллельного преобразования

- •6.2.7 Микросхема КР1108 ПП-1

2.9 Интегральная инжекционная логика

Основные параметры:

–напряжение питания +1,1 … +1,5 В;

–потребление десятки мкВт на схему (сравнимое с КМОП);

–уровень нуля +0,1 В;

–уровень единицы +0,4 В;

–температурный диапазон -10 – +70 °С;

–среднее время задержки 100 ÷ 500 нс (невысокое быстродействие);

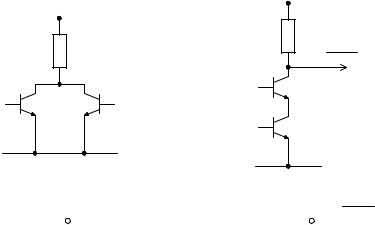

В основе логики лежит НСТЛ (см. рисунок 2.19) (транзисторная логика с непосредственными связями).

Достоинство НСТЛ: возможность несложных соединений на подложке микросхемы.

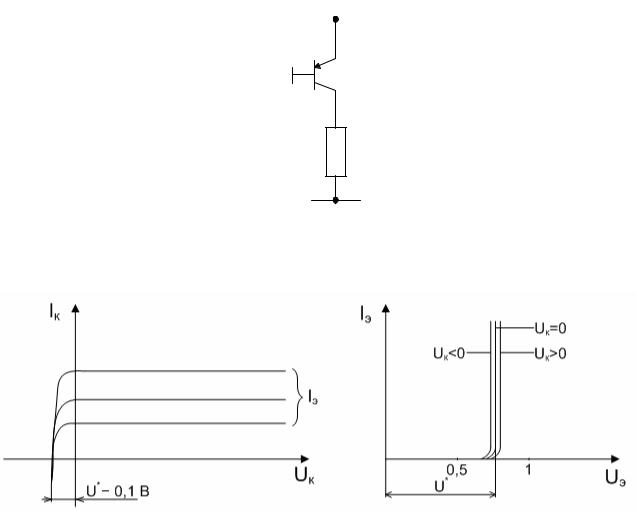

Недостатки НСТЛ: невысокое быстродействие, среднее время задержки 1000 нс. Поэтом не применяется, последующая модернизация (введение ГСТ вместо резисторов, образование микрорежимов по току и снижение напряжения питания) привело к разработке интегральной инжекционной логики, у которой вместо резисторов ГСТ (генератор стабильного тока), вводится транзистор p-n-p (см. рисунок 2.20). Это включение по схеме с ОБ имеет вид редко встречающихся характеристик (см. рисунок 2.21).

+E0

+E0

R

F=X1·X2

X1

X1 |

X2 |

X2

X1 |

|

|

|

|

|

X1 |

|

|

F=X1·X2 |

||

|

1 |

F=X1+X2 |

|

& |

|||||||

|

|

||||||||||

X2 |

|

|

|

|

|

X2 |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

Рисунок 2.19 – НСТЛ

89

Рисунок 2.20 – Генератор стабильного тока

Рисунок 2.21 – Характеристики транзистора в схеме ОБ

Из построения видно, что в окрестности нуля влево и вправо эмиттерные характеристики практически горизонтальны, следовательно, динамическое сопротивление велико. Т. е. в этом режиме транзистор при положительном и отрицательном коллекторном напряжении выполняет роль резистора длинной дорожки, стабилизируя ток. Следовательно, если приложить +Е0 и стабилизировать этот ток, то он протекает по цепи Э···Б···З, образуется режим насыщения, особенность которого в том, что часть неосновных носителей базы попадают в область коллектора, потом инжектируется в нагрузку.

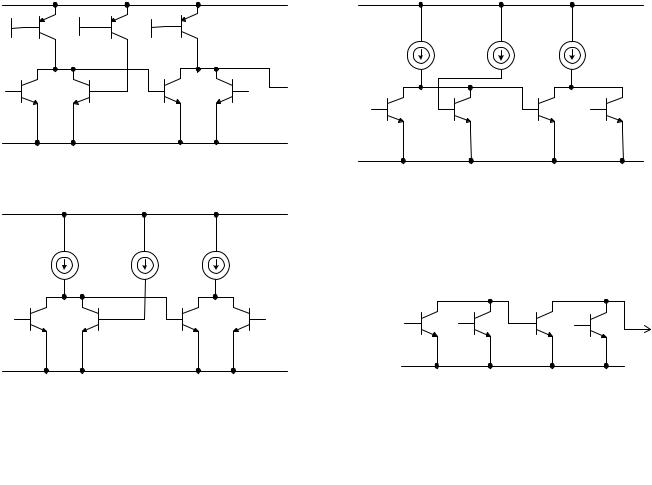

Таким образом, резисторы заменяют транзисторами и получают логику с инжекционным питанием, изображенную на различных вариантах схем рисунка

2.22, а, б, в, г.

90

Рисунок 2.22 – Логика с инжекционным питанием:

а) с ГСТ вместо резисторов; б) с условным изображением ГСТ кружками;

в) в плоскости рисунка базовые электроды второго и четвертого транзисторов повернуты вправо;

г) с целью упрощения ГСТ не приведены, но подразумевается, что они есть.

Широко применяются в калькуляторах, часах, т. е. там, где необходимо малое питание и микромощное потребление. Потому что микрорежимы ГСТ в схеме с ОБ обладают малой чувствительностью к изменению напряжения питания, а тип соединения несложен в конструктивном исполнении. Дают простую связь между каскадами. Применяется в больших СБИС схемах (сверхбольшие интегральные схемы). Как ГСТ, так и транзисторы логики (здесь логика “или”, а для инверсных уровней “и”, по принципу двойственности), выполнены многоколлекторными (см. рисунок 2.23), что и позволяет несложным образом достигать широкого разветвления.

91

Рисунок 2.23 –И2Л

Резистор R включают для того, чтобы сделать характеристику Iэ на рисунке 2.21 более горизонтальной. В этом случае обеспечивается высокая стабильность динамического сопротивления.

2.10 Логика ПТШ (полевые транзисторы Шоттки)

Основные параметры:

–потребляемая мощность 0,5 ÷ 2,5 Вт на корпус;

–напряжение питания +4 В ± 0,2 В Uип1 (Ucc1)

–3,95 В ± 0,12 В Uип2 (Ucc2);

–уровень единицы U1 +0,95…1,5 В (Uон) out high;

–уровень нуля U0 -(0,2…0,1) В (Uol) out low;

–быстродействие 0,16 ÷ 0,3 нс;

–температурный диапазон -10 – +70 °С;

–частотный диапазон свыше 1000 МГЦ;

–входной ток низкого уровня 0,5 мА;

–входной ток высокого уровня 1 мА;

–выходной ток около 30 мА.

GaAs – химическое соединение – арсенид галлия InP – фосфид индия,

Типовая серия :

Схема логики ПТШ приведена на рисунке 2.24.

92