- •58. Шумы в электронных схемах

- •59. Рачет рабочей точки стандартных усилительных каскадов на бт.

- •61. Обратные связи в усилителях.

- •62. Влияние обратной связи на параметры и характеристики усилителей

- •63. Термостабилизация в усилительных каскадах

- •64. Обратная связь в многокаскадных усилителях ( или см. 61)

- •65. Однокаскадный усилитель rc-типа на бт с общим эмиттером (построение эквивалентной схемы)

- •66. Однокаскадный усилитель rc-типа на бт с общим эмиттером (анализ параметров по переменному току)

- •67. Усилители постоянного тока. Назначение, параметры, основные особенности.

- •68. Методы борьбы с дрейфом нуля. Местные отрицательные обратные связи.

- •69. Методы борьбы с дрейфом нуля. Балансные (мостовые схемы).

- •70. Дифференциальный каскад.

- •71. Метод модуляции-демодуляции.

- •72. Комбинированные методы борьбы с дрейфом нуля.

- •73. Операционные усилители

- •74. Инвертирующий усилитель

- •75. Неинвертирующий усилитель

- •76. Применение оу для выполнения нелинейных операций

- •77. Применение оу для выполнения математических операций

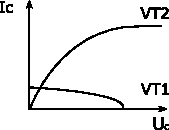

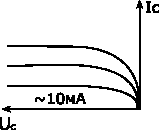

- •78. Электронные ключи. Параметры и характеристики

- •79. Ключ на биполярном транзисторе

- •80. Ключ на переключателе тока

- •81. Ключи на полевых транзисторах.

- •82. Комплементарный ключ (кмдп)

- •83. Логические элементы. Основные параметры и особенности

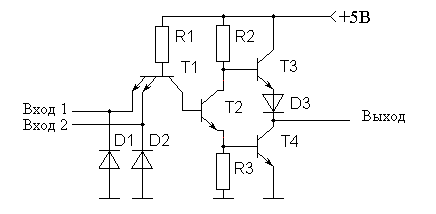

- •84. Элемент ттл со сложным инвертором.

- •85. Дтл-логика

- •86. Этл-логика

- •87. Кмоп-логика

- •88. Триггерная ячейка.

- •89. Триггер с раздельными входами

- •90. Интегральные триггеры

- •91. Rs-триггеры

- •44. D-триггер

- •45. Т-триггер

- •46.Jk-триггер

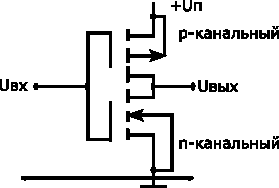

82. Комплементарный ключ (кмдп)

В схеме отсутствуют пассивные сопротивления.

На входах всех микросхем устанавливаются защитные цепочки. Их функции:

Защищают от статического электричества и выбросов входного напряжения обоих полярностей. На схемах не изображаются никогда.

Внутри БИС цепочки не используются. Они включаются только к выводам, ко входам.

Защита от статики — обязательна при работе с МДП элементами!

Уменьшение входных сопротивлений МДП миксросхем и, что существенно, увеличение входной мощности на два порядка.

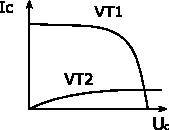

Принцип действия КМДП ключа

На входе высокий уровень. Uвх = Uвх1. VT2 открыт, VT1 закрыт. На выходе низкий уровень. Uвых практически равно нулю I ≈ 10 пА. Uвых ≈ 10мкВ.

Uвх = Uвх0. На входе низкий уровень. VT2 закрыт. Транзистор отсчитывает напряжение на затворе относительно потенциала подложки. На затворе Uзvt - Uп = -5 В. Поэтому VT1 открыт. Его характеристики в этом режиме симметричны. Uвых = +5. U ≈ 10 мкВ (из-за токов утечки).

КМДП ключ обеспечивает близкие к идеальному статические уровни на выходе.

83. Логические элементы. Основные параметры и особенности

Логическим элементом называется электрическая схема, выполняющая какую-либо логическую операцию (операции) над входными данными и возвращающая результат операции в виде выходного уровня напряжения. Логический элемент воспринимает входные данные в виде высокого (напряжение логической 1) и низкого (напряжение логического 0) уровней напряжения на своих входах. Обычно, логические элементы собираются как отдельная интегральная микросхема. Логические операции: конъюнкция (логическое умножение, И), дизъюнкция (логическое сложение, ИЛИ), отрицание (НЕ) и сложение по модулю 2 (исключающее ИЛИ). Рассмотрим основные типы логических элементов.

Параметры:

- коэф-т объединения по входу

- коэф разветвления по выходу

Основные параметры: напряжение источника питания, уровни напряжений логического 0 и логической 1, нагрузочная способность, помехоустойчивость и быстродействие, потребляемая мощность.

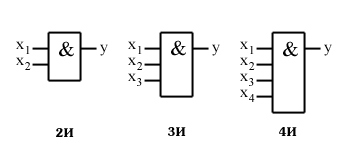

Элемент И

Л огический

элемент И выполняет операцию логического

умножения (конъюнкция) над своими

входными данными и имеет от 2 до 8 входов

и один выход (как правило, выпускаются

элементы с двумя, тремя, четырьмя и

восемью входами). На рис. 1. изображены

условные графические обозначения (УГО)

логических элементов И с двумя, тремя

и четырьмя входами соответственно.

Элементы И обозначаются как NИ, где N -

количество входов логического элемента

(например, 2И, 3И, 8И и т.д.).

огический

элемент И выполняет операцию логического

умножения (конъюнкция) над своими

входными данными и имеет от 2 до 8 входов

и один выход (как правило, выпускаются

элементы с двумя, тремя, четырьмя и

восемью входами). На рис. 1. изображены

условные графические обозначения (УГО)

логических элементов И с двумя, тремя

и четырьмя входами соответственно.

Элементы И обозначаются как NИ, где N -

количество входов логического элемента

(например, 2И, 3И, 8И и т.д.).

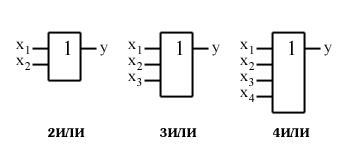

Э лемент

ИЛИ

лемент

ИЛИ

Логический элемент ИЛИ выполняет операцию логического сложения (дизъюнкция) над своими входными данными и, также как и логический элемент И, имеет от 2 до 8 входов и один выход. На рис. 2. изображены УГО логических элементов ИЛИ с двумя, тремя и четырьмя входами соответственно. Элементы ИЛИ обозначаются также, как и элементы И (2ИЛИ, 4ИЛИ и т.д.).

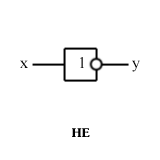

Элемент НЕ (инвертор)

Л огический

элемент НЕ выполняет операцию логического

отрицания над своими входными данными

и имеет один вход и один выход. Иногда

его называют инвертор, так как он

инвертирует входной сигнал. На рис. 3

изображено УГО элемента НЕ.

огический

элемент НЕ выполняет операцию логического

отрицания над своими входными данными

и имеет один вход и один выход. Иногда

его называют инвертор, так как он

инвертирует входной сигнал. На рис. 3

изображено УГО элемента НЕ.

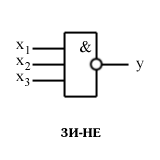

Элемент И-НЕ

Л огический

элемент И-НЕ выполняет операцию

логического умножения над своими

входными данными, а затем инвертирует

(отрицает) полученный результат и выдаёт

его на выход. Таким образом, можно

сказать, что логический элемент И-НЕ -

это элемент И с инвертором на выходе.

УГО элемента 3И-НЕ приведено на рис..

огический

элемент И-НЕ выполняет операцию

логического умножения над своими

входными данными, а затем инвертирует

(отрицает) полученный результат и выдаёт

его на выход. Таким образом, можно

сказать, что логический элемент И-НЕ -

это элемент И с инвертором на выходе.

УГО элемента 3И-НЕ приведено на рис..

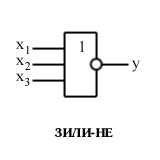

Элемент ИЛИ-НЕ

Л огический

элемент ИЛИ-НЕ выполняет операцию

логического сложения над своими входными

данными, а затем инвертирует (отрицает)

полученный результат и выдаёт его на

выход. Таким образом, можно сказать,

что логический элемент ИЛИ-НЕ - это

элемент ИЛИ с инвертором на выходе. УГО

элемента 3ИЛИ-НЕ приведено на рис.

огический

элемент ИЛИ-НЕ выполняет операцию

логического сложения над своими входными

данными, а затем инвертирует (отрицает)

полученный результат и выдаёт его на

выход. Таким образом, можно сказать,

что логический элемент ИЛИ-НЕ - это

элемент ИЛИ с инвертором на выходе. УГО

элемента 3ИЛИ-НЕ приведено на рис.

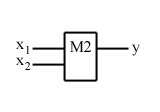

Элемент сложения по модулю 2

Э тот

логический элемент выполняет логическую

операцию сложения по модулю 2 и, как

правило, имеет 2 входа и один выход.

Такой элемент, в основном, используется

в схемах аппаратного контроля. УГО

элемента приведено на рис.

тот

логический элемент выполняет логическую

операцию сложения по модулю 2 и, как

правило, имеет 2 входа и один выход.

Такой элемент, в основном, используется

в схемах аппаратного контроля. УГО

элемента приведено на рис.

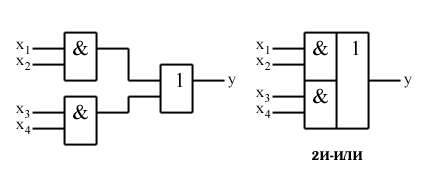

Комбинационные логические элементы

Существуют и более сложные логические элементы, выполняющие несколько логических операций над своими входными данными. Например, элемент 2И-ИЛИ, УГО и схема которого приведено на рис., сначала выполняет операцию логического умножения над парами операндов x1, x2 и x3, x4, а затем выполняет операцию логического сложения над полученными результатами, т.е. y = x1x2 + x3x4.

Простейшие логические элементы на биполярных транзисторах.

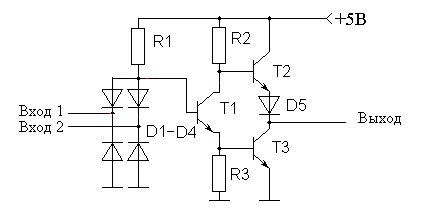

Принципиальная схема типового элемента 2И-НЕ диодно-транзисторной логики(ДТЛ) приведена на рис. 2. Если хотя бы на одном из входов (число которых может быть более двух) появляется уровень 0 (низкое напряжение), то соответствующий входной диод открывается и сигнал низкого напряжения практически закрывает транзистор Т1. При этом Т3 будет закрыт, а Т2 открыт и на выходе установится уровень 1 (высокий уровень). Для получения на выходе уровня 0 нужно, чтобы все входные диоды были закрыты, т.е. на входах должны быть уровни 1.

Рис. 2. Принципиальная схема ДТЛ

Принципиальная схема типового элемента 2И-НЕ транзисторно-транзисторной логики(ТТЛ) приведена на рис. 3. В отличие от схемы ДТЛ роль входных диодов выполняют эмиттерные переходы многоэмиттерного транзистора Т1.

|

|

Рис. 3. Принципиальная схема ТТЛ