МПУЭВС. Лекции. Задания / pdf_ПрилПЦиПУ / Приложение_ М_ ОднокристОМЭВМ

.pdfПриложение М

Однокристальная микроЭВМ (ОМЭВМ)

М.1 Введение

Однокристальная микроЭВМ 1816ВЕ51 (аналог МП i 8051), является развитием МП шинного варианта, в котором технология производства кристаллов микропроцессорных средств позволила на одном кристалле разместить не только микропроцессор, но и память программ, и память данных, и ограниченный набор портов для связи МП с окружением вне общего корпуса. Пространственная близость памяти к процессору, не изменяя функционального назначения каждого из них в общей структуре позволила реализовать идеи Гарвардской архитектуры вычислительных средств в части раздельного доступа устройства управления МП к области хранения команд программ и данных к обработке. Попутно были приняты решения по размещению в общем корпусе устройства портов внешних подключений, тем более, что к этому времени был накоплен опыт применения программируемых параллельных адаптеров, один из вариантов которых обсуждается в разделе 4 пособия. На основе портов внутреннего назначения был открыт доступ в состав такой однокристальной структуры разнообразных технических средств, которые до этого соответствовали электронным аналогам периферийных устройств. Это в первую очередь таймеры и измерители временных параметров сигналов. Позже перечень этих электронных узлов и устройств был дополнен аналоговыми компараторами, с последующим расширением состава устройств до цифроаналоговых и аналого-цифровых преобразователей, широтно-

импульсных преобразователей. Перечень идей по расширению состава новых приборов на кристалле на современных технологиях производства утратил множество ограничений и продолжает расширяться. В пособии для первичного ознакомления предпочтение отдано МП однокристальной МЭВМ МК51, которая стала классическим примером перехода от шинных процессоров к устройствам, которые шины «спрятали в себе», но по

необходимости реализуют шинную структуру внешних связей в доступе к памяти и портам внешнего окружения.

М.2 Структурная организация ОМЭВМ 1816ВЕ51

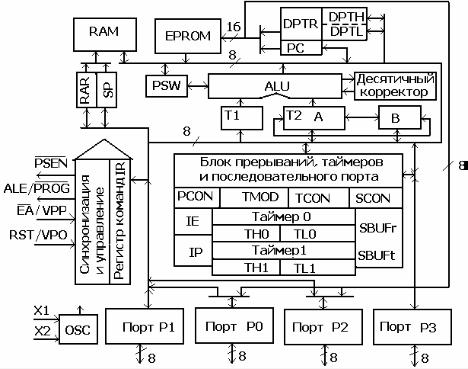

Структурная схема ОМЭВМ 1816ВЕ51 приведена на рисунке М.1.

Рисунок М.1 - Структурная схема ОМЭВМ 1816ВЕ51

В состав ОМЭВМ включены устройство управления, синхронизации,

операционный блок, память регистров общего назначения (РОНы),

совмещеная с регистровой оперативной памятью ОМЭВМ.

Особенностью организации РОНов ОМЭВМ является наличие под общими регистровыми адресами R0-R7 четырёх банков (Банк0 - Банк3)

размером по восемь регистров и слов формата один байт. На кристалле вместе с процессором расположена оперативная память размером 128 слов формата один байт и в этом пространстве начальные восемь ячеек закреплены за активным банком РОНов. С ячейки 07h ОЗУ расположен одноуровневый стек на восемь ячеек. В пространстве адресов с 10h по 7Fh

расположена регистровая память с прямой абсолютной и косвенной через регистры R0, R1 адресацией. В этом адресном пространстве в ячейках 20h-

2Fh предусмотрена прямая битовая адресация каждого бита по специальной кодировочной таблице. С адреса 80h по F0h расположены адреса регистров специальных функций РСФ, (Special Function Register - SFR), к части которых предусмотрен прямой битовый адресный доступ по кодировочной таблице. Назначение регистров SFR определяется их спецификацией в составе ОМЭВМ. Ячейки с адресами 80h-0FFh, которые не заняты регистрами SFR, физически отсутствуют.

У микроконтроллеров семейства i805х память программ и память данных являются самостоятельными и независимыми друг от друга устройствами, адресуемыми различными адресными указателями и разными управляющими сигналами. Объем встроенной памяти программ,

расположенной на кристалле ОМЭВМ в базовой модели был равен 4 Кбайт.

При обращении к внешней памяти программ микроконтроллеры семейства i805х используют 16-разрадный адрес, что обеспечивает им доступ к 64

Кбайт. Операционный блок выполняет подмножество логических и арифметических команд. (операции сложения, вычитания, сравнения,

умножения и деления целых чисел размером один байт, десятичную коррекцию двоичной суммы в двоично-десятичный формат) В АЛУ ОМЭВМ реализован расширенный набор операций над битами с адресным доступом к биту в области памяти данных, портах связи с внешним окружением.

В состав ОМЭВМ включены два таймера, настраиваемые на четыре доступных режима, универсальный приёмопередатчик последовательного кода и четыре порта для внешних подключений P0-P3 . Программными установками порты настраиваются для ввода или для вывода. В ОМВМ предусмотрена возможность счёта импульсов с внешних линий через альтернативно перенастраиваемые входы порта P3. В ОМЭВМ применён блок многоуровневых аппаратных прерываний с программным управлением маскированием. Два уровня прерывания выделены внешним запросам и четыре выделены под внутренние запросы от таймеров и буферных регистров передатчика и приёмника последовательного кода.

М.3 Организация ОЗУ, ПЗУ и регистров ОМЭВМ

М.3.1 Память программ (ПЗУ).

Память программ и память данных ОМЭВМ являются самостоятельными и независимыми друг от друга устройствами,

адресуемыми различными командами и управляющими сигналами.

Объем встроенной памяти программ, расположенной на кристалле ОМЭВМ равен 4 Кбайт. При обращении к внешней памяти программ ОМЭВМ семейства 1816ВЕ51 используют 16-разрадный адрес, что обеспечивает им доступ к 64 Кбайт ЗУ. Микроконтроллер обращается к программной памяти при чтении кода операции и операндов (используя счетчик команд PC), а также при выполнении команд переноса байта из памяти программ в аккумулятор. При выполнении команд переноса данных адресация ячейки памяти программ, из которой будут прочитаны данные,

может осуществляться с использованием, как счетчика PC, так и специального двухбайтового регистра-указателя данных DPTR.

М.3.2 Память данных (ОЗУ)

Объем расположенной на кристалле памяти данных—128 байт. Объем

внешней памяти данных может расширяться по принципам вычислительных средств Принстонской (Неймановской) архитектуры. 64 Кбайт.

Первые 32 байта внутренней памяти данных образуют в четыре банка регистров общего назначения, обозначаемых соответственно банк 0 - банк 3.

Каждый из названных банков состоит из восьми регистров R0-R7. Доступ к банку регистров открывается по номеру, соответствующему третьему и четвертому битам слова состояния программы PSW, назначение битов которого приводится далее.

РPSW.0 Флаг паритета. Устанавливается и сбрасывается на

аппаратно каждом цикле команды. Фиксирует нечетное

/четное число единичных бит в аккумуляторе

-PSW.1 Не используется

OV |

PSW.2 |

Флаг переполнения. Устанавливается и сбрасывается на |

||

|

|

аппаратном уровне при выполнении арифметических |

||

|

|

операций |

|

|

RS0 |

PSW.3 |

Биты выбора используемого банка регистров |

||

RS1 |

PSW.4 |

могут быть изменены программным путем |

||

|

|

RS0-RS1 |

Банк Адрес |

|

|

|

00 |

0 |

00Н - 07h |

|

|

01 |

1 |

08Н - 0Fh |

|

|

10 |

2 |

18H - 1Fh |

|

|

|

|

11 |

3 |

18H - 1Fh |

|

|

F0 |

PSW.5 |

Флаг пользователя. Может быть установлен, сброшен или |

||||

|

|

проверен программой пользователя |

|

|||

АС |

PSW.6 |

Флаг |

вспомогательного переноса. |

Устанавливается и |

||

|

|

сбрасывается |

только |

аппаратными |

средствами при |

|

|

|

выполнении |

команд |

сложения и вычитания. Сигнализи- |

||

|

|

рует о переносе или заёме между ниблами аккумулятора |

||||

СPSW.7 Флаг переноса. Устанавливается и сбрасывается

как аппаратно, так и программным путем

Наиболее "активным" флагом PSW является флаг переноса, который принимает участие и модифицируется в процессе выполнения множества операций, включая сложение, вычитание и сдвиги. Кроме того, флаг переноса (С) выполняет функции "булева аккумулятора" в командах,

манипулирующих с битами. Флаг переполнения (OV) фиксирует арифметическое переполнение при операциях над целыми числами со знаком и делает возможным использование арифметики в дополнительных кодах.

Значение битов выбора банков регистров (RS0, RS1) определяется прикладной программой и используется для выбора одного из четырёх регистровых банков.

Имея в составе регистров аккумулятор, МП 1816ВЕ51 может выполнять множество команд и без его участия. Данные могут быть переданы из любой

ячейки RАM в любой регистр, любой регистр может быть загружен непосредственным операндом и т.д. Многие логические операции могут быть выполнены без участия аккумулятора. Кроме того, переменные могут быть инкрементированы, декрементированы и проверены без использования аккумулятора. Флаги и управляющие биты могут быть проверены и изменены аналогично.

Оставшееся адресное пространство может конфигурироваться по усмотрению разработчика. В нем располагаются стек, системные и пользовательские области данных. Предусмотрена прямая и косвенная адресация ячеек памяти данных. В этом случае адрес ячейки является операндом соответствующей команды.

Таблица М.1 - Организация резидентной памяти данных ОМЭВМ

ОЗУ (30h-7Fh)

ОЗУ (20h-2Fh) Битовая область

ОЗУ (00h-1Fh)

Банк РОН 3 (R0-R7)

Банк РОН 2 (R0-R7)

Банк РОН 1 (R0-R7)

Банк РОН 0 (R0-R7)

Для косвенной адресация используются регистры R0 или R1, в один из которых перед обращением к ячейке памяти должен быть занесен адрес ячейки. Для обращения к внешней памяти данных используется только косвенная адресация с помощью регистров R0 и R1 или с помощью 16-

разрядного регистра-указателя DPTR (из файла регистров специальных функций). Формат регистра-указателя DPTR позволяет адресовать 64 Кбайта

внешней памяти.

Часть памяти данных ОЗУ с адресами (20h-2Fh) обеспечена возможностью доступа к битам ячеек, с прямым указанием в команде адреса бита. Адрес прямо адресуемых битов может быть записан либо в виде (Адрес Байта ).(Разряд), например выражение 21.3 означает третий разряд ячейки памяти с адресом 21h, либо в виде абсолютного битового адреса 0Bh.

Соответствие этих способов адресации можно определить по таблице М2.

К адресному пространству памяти данных примыкает адресное пространство регистров специальных функций SFR (Special Function

Register). Адреса расположения SFR регистров, приведены в таблице М3.

Таблица М2 - |

Таблица адресов области памяти с битовой адресацией |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

Адрес |

|

|

|

Адреса битов |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

D7 |

D6 |

D5 |

D4 |

D3 |

|

D2 |

D1 |

D0 |

|

|

|

|

|

|

|

|

|

|

|

|

2Fh |

7F |

7Е |

7D |

7С |

7В |

|

7А |

79 |

78 |

|

|

|

|

|

|

|

|

|

|

|

|

2Еh |

77 |

76 |

75 |

74 |

73 |

|

72 |

71 |

70 |

|

|

|

|

|

|

|

|

|

|

|

|

2Dh |

6F |

6Е |

6D |

6С |

6В |

|

6А |

69 |

68 |

|

|

|

|

|

|

|

|

|

|

|

|

2Сh |

67 |

66 |

65 |

64 |

63 |

|

62 |

61 |

60 |

|

|

|

|

|

|

|

|

|

|

|

|

2Вh |

5F |

5Е |

5D |

5С |

5В |

|

5А |

59 |

58 |

|

|

|

|

|

|

|

|

|

|

|

|

2Аh |

57 |

56 |

55 |

54 |

53 |

|

52 |

51 |

50 |

|

|

|

|

|

|

|

|

|

|

|

|

29h |

4F |

4Е |

4D |

4С |

4В |

|

4А |

49 |

48 |

|

|

|

|

|

|

|

|

|

|

|

|

28h |

47 |

46 |

45 |

44 |

43 |

|

42 |

41 |

40 |

|

|

|

|

|

|

|

|

|

|

|

|

27h |

3F |

ЗЕ |

3D |

ЗС |

ЗВ |

|

ЗА |

39 |

38 |

|

|

|

|

|

|

|

|

|

|

|

|

26h |

37 |

36 |

35 |

34 |

33 |

|

32 |

31 |

30 |

|

|

|

|

|

|

|

|

|

|

|

|

25h |

2F |

2Е |

2D |

2С |

2В |

|

2А |

29 |

28 |

|

|

|

|

|

|

|

|

|

|

|

|

24h |

27 |

26 |

25 |

24 |

23 |

|

22 |

21 |

20 |

|

|

|

|

|

|

|

|

|

|

|

|

23h |

1F |

1Е |

1D |

1С |

1В |

|

1А |

19 |

18 |

|

|

|

|

|

|

|

|

|

|

|

|

22h |

17 |

16 |

15 |

14 |

13. |

|

12 |

11 |

10 |

|

|

|

|

|

|

|

|

|

|

|

|

21h |

0F |

0Е |

0D |

0С |

0В |

|

0А |

09 |

08 |

|

|

|

|

|

|

|

|

|

|

|

|

20h |

07 |

06 |

05 |

04 |

03 |

|

02 |

01 |

00 |

|

|

|

|

|

|

|

|

|

|

|

Таблица. МЗ - Размещение регистров SFR в адресном пространстве

Адрес |

Имя |

Наименование |

|

|

|

0Е0Н |

*АСС |

Аккумулятор (Accumulator) |

|

|

|

0F0H |

*В |

Регистр расширитель аккумулятора (Multiplication |

|

|

Register) |

|

|

|

0D0H |

*PSW |

Слово состояния программы (Program Status Word) |

|

|

|

080Н |

*Р0 |

Порт 0 (SFR P0) |

|

|

|

090Н |

*Р1 |

Порт 1 (SFR P1) |

|

|

|

0A0H |

*Р2 |

Порт 2 (SFR P2) |

|

|

|

0В0Н |

*РЗ |

Порт 3 (SFR РЗ) |

|

|

|

081Н |

SP |

Регистр указатель стека (Stack Pointer) |

|

|

|

083Н |

DPH |

Старший байт регистра указателя данных DPTR (Data |

|

|

Pointer High) |

|

|

|

082Н |

DPL |

Младший байт регистра указателя данных DPTR (Data |

|

|

Pointer Low) |

|

|

|

08СН |

ТНО |

Старший байт таймера 0 |

|

|

|

08АН |

TLO |

Младший байт таймера 0 |

|

|

|

08DH |

ТН1 |

Старший байт таймера 1 |

|

|

|

08ВН |

TL1 |

Младший байт таймера 1 |

|

|

|

089Н |

TMOD |

Регистр режимов таймеров счетчиков (Timer/Counter |

|

|

Mode Control Register) |

|

|

|

088Н |

*TCON |

Регистр управления статуса таймеров (Timer/Counter |

|

|

Control Register) |

|

|

|

0В8Н |

*IP |

Регистр приоритетов (Interrupt Priority Control Register) |

|

|

|

0А8Н |

*IE |

Регистр маски прерывания (Interrupt Enable Register) |

|

|

|

087Н |

PCON |

Регистр управления мощностью (Power Control Register) |

|

|

|

098Н |

*SCON |

Регистр управления приемопередатчиком (Serial Port |

|

|

Control Register) |

|

|

|

099Н |

SBUF |

Буфер приемопередатчика (Serial Data Buffer) |

|

|

|

Примечание: Регистры, символ которых отмечен знаком «*»,

допускают адресацию отдельных бит в соответствии с таблицей М.4 при использовании команд из группы команд операций над битами.

Таблица М.4- Карта адресуемых битов блока SFR

Адрес |

|

|

Адреса битов по разрядам |

|

|

Имя |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

Adr |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

|

D0 |

Name |

|

|

|

|

|

|

|

|

|

|

|

|

|

F0h |

F7 |

F6 |

F5 |

F4 |

F3 |

F2 |

F1 |

|

F0 |

В |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Е0Н |

Е7 |

Е6 |

Е5 |

Е4 |

ЕЗ |

Е2 |

Е1 |

|

Е0 |

АСС |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D0H |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

|

D0 |

PSW |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

В8Н |

- |

- |

- |

ВС |

ВВ |

ВА |

В9 |

|

В8 |

IP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

В0 |

В7 |

В6 |

В5 |

В4 |

ВЗ |

В2 |

В1 |

|

В0 |

РЗ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

А8Н |

AF |

- |

- |

АС |

АВ |

АА |

А9 |

|

А8 |

IE |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||

А0Н |

А7 |

А6 |

А5 |

А4 |

A3 |

А2 |

А1 |

А0 |

Р2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

98Н |

9F |

9Е |

9D |

9С |

9В |

9А |

99 |

98 |

SCON |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

90Н |

97 |

96 |

95 |

94 |

93 |

92 |

91 |

90 |

Р1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

88Н |

8F |

8Е |

8D |

8С |

8В |

8А |

89 |

88 |

TCON |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

80Н |

87 |

86 |

85 |

84 |

83 |

82 |

81 |

80 |

Р0 |

|

|

|

|

|

|

|

|

|

|||||

Примечание: На языке символьных записей адрес прямо адресуемых |

|||||||||||

битов SFR |

может записываться в программах |

в виде выражения (Имя |

|||||||||

регистра).(Разряд), например выражение SCON.3, либо в виде адреса бита,

который для данного бита равен (см. таблицу) 9В. При этом для некоторых битов управляющих регистров допустима запись бита символьным именем.

Так бит 9Вh имеет имя ТВ8.

Ячейки памяти с адресами 80H-0FFH, которые не заняты регистрами,

физически отсутствуют, на кристаллах ОМЭВМ 1816ВЕ51. При обращении к ним можно прочитать код совпадающий с кодом команды возврата.

Регистры специальных функций управляют работой блоков, входящих в ОМЭВМ. Так регистры SFR параллельных портов P0...P3 - служат для ввода-вывода информации. Две регистровые пары с именами TH0, TL0 и

ТН1, TL1 представляют собой регистры, двух программно-управляемых 16-

битных таймеров-счетчиков. Режимы таймеров-счетчиков задаются с использованием регистра TMOD, а управление ими осуществляется с помощью регистра TCON.

Для управления режимами энергопотребления микро-ЭВМ используется регистр PCON.

Регистры IP и IE управляют работой системы прерываний микро-

ЭВМ. Регистры SBUF и SCON управляют работой приемопередатчика последовательного порта. Регистр-указатель стека SP в микро-ЭВМ рассматриваемого семейства — восьми битный. Он может адресовать любую область внутренней памяти данных. В микро-ЭВМ 1816ВЕ51 стек «растет вверх», т.е. перед выполнением команды PUSH или CALL содержимое SP

инкрементируется, после чего производится запись информации в стек.

Соответственно при извлечении информации из стека регистр SP

декрементируется после извлечения информации. В процессе инициализации микро-ЭВМ после сигнала сброса или при включении питающего напряжения в SP заносится код 07Н. Это означает, что первый элемент стека будет располагаться в ячейке с адресом 08h. Регистр-указатель данных DPTR

используется для фиксации 16-битного адреса в операциях обращения к внешней памяти программ и данных. Он может программироваться как в