МПУЭВС. Лекции. Задания / pdf_ПрилПЦиПУ / Приложение _Н_ ПериферМодулиADSP

.pdf

21

генератора 16.384 МГц. Скорость выполнения программы определяет внешний генератор 37. 5 МГц.

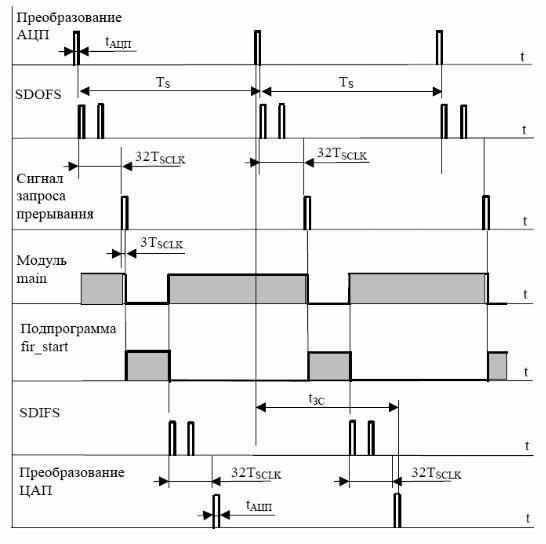

Рисунок Н.10 - Временные диаграммы процесса цифровой обработки аналогового сигнала

Н.4 Подключение устройств к сигнальному процессору

Внешние устройства (клавиатура, индикаторы, кнопки и т.п.) могут подключаться непосредственно к восьми программируемым выводам процессора – флагам общего назначения PF0:7. В регистр PFTYPE

необходимо записать восемь бит, чтобы определить направление сигнала по отдельному флагу (рисунок Н.11). Разряды 15-8 используются портом BDMA

и для задания конфигурации. Конфигурация при MODE D = 1 отличается от

MODE D = 0 другим способом формирования сигнала управления J внешней

22

памяти, разряд 7 соответствует выводу микросхемы PF7, разряд 0 – выводу

PF0. Запись нуля в разряд i настраивает соответствующий сигнал PFi на ввод, запись единицы – на вывод. Шесть младших разрядов PF настроены на вывод, два старших – на ввод. При инициализации программы в регистр

PFTYPE занесено двоичное число 00111111. Следовательно, флаги PF7 и PF6 определены как входы, PF5 - PF0 – выходы. Формирование выходных сигналов и чтение входов флагов выполняется с помощью регистра PFDATA

(рисунок Н.12). Содержимое регистра PFDATA при чтении флагов обновляется синхронно с частотой тактовых импульсов процессора CLKOUT.

Флаги, которые запрограммированы и работают на вывод данных, при выполнении команды чтения регистра возвращают значения выходных сигналов. Номер разряда байта PFDATA соответствует номеру флага PF. Во время сброса программируемые флаги устанавливаются по умолчанию на ввод данных. Необходимо запретить прерывания IRQ2, IRQE, IRQL0 и IRQL1

с помощью регистра IMASK, чтобы разрешить прохождение сигналов PF4PF7.

Рисунок Н.11 - Программирование регистра флагов PFTYPE

Рисунок Н.12 - Запись и чтение регистра флагов PFDATA

Кроме программируемых входов/выходов общего назначения микросхема процессора содержит пять флагов FL0, FL1, FL2, FO и FI,

23

предназначенных для создания многопроцессорных систем и работающих всегда в одном направлении: FL0, FL1, FL2, F0 – выходы, FI – вход. Сигналы

F0 и FI могут использоваться, если в системе не задействован последовательный порт SPORT1. Выбор флагов F0, FI или порта SPORT1

выполняется с помощью бита 10 в регистре управления системой,

расположенном по адресу 0x3FFF.

Cостояние входного сигнала FI анализируется и учитывается в программе во время исполнения ассемблерной команды условного перехода

“ if FLAG_IN” или “ if not FLAG_IN”. В зависимости от уровня сигнала на входе FI условие выполняется или не выполняется, процессор переходит на разные участки программы. Флаг устанавливается (FLi = 1) командой SET,

сбрасывается (FLi = 0) командой RESET. Примеры команд на языке ассемблера, работающих с флагами FLi и программируемыми флагами PFi,

приведены в листинге 1. В одной строке располагается одна команда, которая заканчивается точкой с запятой. Комментарии выделяются с помощью символов /*,*/. Системные переменные регистров PFTYPE и PFDATA

должны быть объявлены в подключаемом файле-заголовке с расширением h.

Листинг 0

Формирование флагов процессора

ax0 = 0xFF3F ;

dm(PFTYPE) = ax0 ; /* 0xFF3F = 1111 1111 0011 1111, PF7, PF6 – входы, PF5 - PF0 – выходы */

/* в регистре PFTYPE задано направление сигналов на выводах PF7-PF0 */ ax0 = 0x0С ;

dm(PFDATA) = ax0 ; /* 0x0С = 0000 1100 */

/* в регистр PFDATA записано число, формирующее сигналы

PF5=PF4=P1=PF0=0, PF3=

PF2=1 */

24

SET FL2; /* установить флаг FL2, т.е. вывести на вывод FL2 напряжение логической единицы */

RESET FL0; /* сбросить флаг FL0, т.е. вывести на вывод FL0 напряжение логического нуля */

IF FLAG_IN JUMP MET1 ; /* если FI = 1, то уйти на метку MET1 */

IF MV SET FLAG_OUT, RESET FL1 ; /* если MV = 1 (переполнение МАС),

то FO = 1,

FL1 = 0 */

MET1: RESET FL2 ; /* FL2 = 0 */

Порты ввода/вывода с 16-разрядной шиной данных и 11-разрядной шиной адреса А10:A0 позволяют подключить к процессору до 2048 (211)

внешних устройств. Каждому порту ввода/вывода соответствует свой адрес.

Множество адресов портов занимает целочисленный диапазон от 0 до 211 – 1, каждый порт используется в программе независимо от других. В отличие от флагов процессора подключение внешнего устройства к порту требует применения дополнительных микросхем для дешифрации адреса,

запоминания выводимых данных и коммутации вводимых данных. Обмен данными через порт происходит с помощью команды ввода/вывода IO,

аналогичной команде обращения к памяти микропроцессорной системы.

Пример схемы подключения двух внешних устройств через однонаправленные порты приведен на рисунке Н.13.

Первый параллельный 16-разрядный порт, состоящий из дешифратора адреса 1 и регистра памяти, работает только на вывод. К нему можно подключить 16-разрядный цифро-аналоговый преобразователь, индикатор и другие устройства вывода с параллельной шиной данных.

Предположим, что первый дешифратор настроен на адрес 0x1FF. Для вывода данных потребуется следующие две команды

ax0 = 0x1234; /* запись числа в регистр процессора,

ax0 = 0001 0010 0011 0100b */IO(0x1FF) = ax0; /* вывод содержимого регистра ax0 в порт 0x1FF */.

25

Во время выполнения команды вывода информации на порт IO (0x1FF)

процессор формирует активные низкие уровни сигналов IOMS, WR на шине управления, двоичный код 001 1111 1111 – на шине адреса А10:A0.

Рисунок Н.13 - Однонаправленные порты ввода/вывода

Одновременная подача перечисленных сигналов меняет выходной сигнал дешифратора и вызывает запись данных во внешний регистр RG с

помощью сигнала синхронизации С. Поступивший с шины данных ADSP- 2189M код 0001 0010 0011 0100 проходит с входов DI на выходы параллельного регистра DO и запоминается на выходе порта до следующего обращения к нему.

Входной порт содержит дешифратор адреса 2 и шинный формирователь BD. Когда процессор не выполняет команду чтения данных входного порта, шинный формирователь находится в высокоомном Z-

состоянии. Выходы формирователя DO отключены от входов двунаправленной шины данных процессора.

Ввести информацию с порта можно одной ассемблерной командой ax0 = IO (0х1FE),

где 0х1FE - пример адреса входного порта, на который настроен второй де-

шифратор.

26

При выполнении команды ввода IO (0х1FE) шинный формирователь выходит из Z-состояния. Выходные сигналы второго внешнего устройства подключаются через формирователь к параллельной шине данных процессора D23:8 и запоминаются во внутреннем 16-разрядном регистре ах0.

Для синхронизации работы ADSP-2189M внутренним или внешним генератором используются выводы микросхемы XTAL, CLKIN, CLKOUT.

Если тактирование выполняется внешним генератором, то его выходной ТТЛ-сигнал с частотой 37.5 МГц подается на вход процессора CLKIN, вывод

XTAL должен быть свободным и не подключенным ни к плюсу источника питания, ни к общей точке схемы. Внутри микросхемы частота удваивается,

образуя тактовую частоту 75 МГц. Большинство команд процессор выполняет за один командный цикл, равный периоду тактовой частоты 13.3

нс. Выходной сигнал CLKOUT меняется с тактовой частотой 75 МГц. Вместо внешнего генератора для синхронизации процессора можно использовать внутренний генератор тактовой частоты (рис. Н.14). Частота встроенного тактового генератора задается кварцевым резонатором BQ, который подключается между выводами CLKIN и XTAL по схеме параллельного резонанса. Емкость внешних конденсаторов С1, С2 зависит от типа резонатора и определяется его изготовителем.

Рисунок Н.14 - Работа процессора от внутреннего генератора тактовой частоты

Напряжение источника питания можно подавать на микросхему ADSP- 2189M двумя способами. Допускается использование одного источника номиналом 2,5 В или двух источников, один из которых обеспечивает

27

напряжением 2,5 В ядро процессора, другой с напряжением 3,3 В

применяется для периферийной части микросхемы (рисунок Н.15).

Рисунок Н.15 - Цепи питания и сброса процессора при включении питания

В таблицё. Н.5 приведены допустимые отклонения напряжений от номинальных значений для двух вариантов температурного исполнения

процессора.

Входное напряжение логической единицы и логического нуля должно

находиться в диапазоне U1 ВХ = 1,5 … 3,3 В, U0 ВХ = 0 … 0,6 |

В. Для сигнала |

синхронизации CLKIN напряжение U1 ВХ = 2,0 … 3,3 |

В. Изготовитель |

микросхемы гарантирует, что минимальное выходное напряжение логической единицы составляет U1ВЫХ MIN = 2,0 В при минимальном напряжении питания UVDDEXT.

Если UVDDEXT = 3,0 В, то минимальное выходное напряжение U1ВЫХ

MIN =2.4 В соответствует уровню ТТЛ-микросхем. Необходимо учитывать,

что выходы процессора выполнены по КМОП-технологии и не допускают подключения нагрузки с постоянным током. Номинальный ток потребления от источника питания составляет 36 мА, в режиме пониженного энергопотребления он уменьшается до 150 мкА. Входной ток одного вывода процессора составляет 10 мкА.

28

Таблица Н.5 - Предельные электрические параметры ADSP-2189M

|

Класс К диапазон Т = 0 |

Класс В диапазон Т = -40 |

|||

Параметр |

… +70° С |

|

… +85° С |

|

|

|

|

|

|

|

|

|

минимум |

максимум |

минимум |

максимум |

|

|

|

|

|

|

|

Напряжение UVDDINT, |

2.37 |

2.63 |

2.25 |

2.75 |

|

В |

|

|

|

|

|

Напряжение UVDDEXT, |

2.37 |

3.6 |

2.25 |

3.6 |

|

В |

|||||

|

|

|

|

||

Входное напряжение, В |

-0.3 |

3.6 |

-0.03 |

3.6 |

|

|

|

|

|

|

|