- •Московский государственный институт

- •Разработка алгоритма выполнения арифметических операций сложения и вычитания многоразрядных чисел в заданном двоично-десятичном коде.

- •Разработка оптимальной схемы одноразрядного двоичного сумматора с учетом заданного базиса логических элементов.

- •Логическая схема одноразрядного двоичного сумматора.

- •Разработка схемы коррекции.

- •Разработка схемы одноразрядного десятичного сумматора.

- •В дальнейшем данную схему будем изображать следующим образом

- •Разработка преобразователя прямого кода в обратный для работы с отрицательными величинами.

- •В дальнейшем данную схему будем изображать следующим образом

- •Функциональная схема фиксирующая переполнение

- •Условное изображение этой функциональной схемы будет следующим.

- •Разработка схемы для определения знака суммы.

- •Разработка функциональной схемы многоразрядного десятичного сумматора

- •Разработка входных и выходных регистров хранения числовой информации, участвующей в операции сложения.

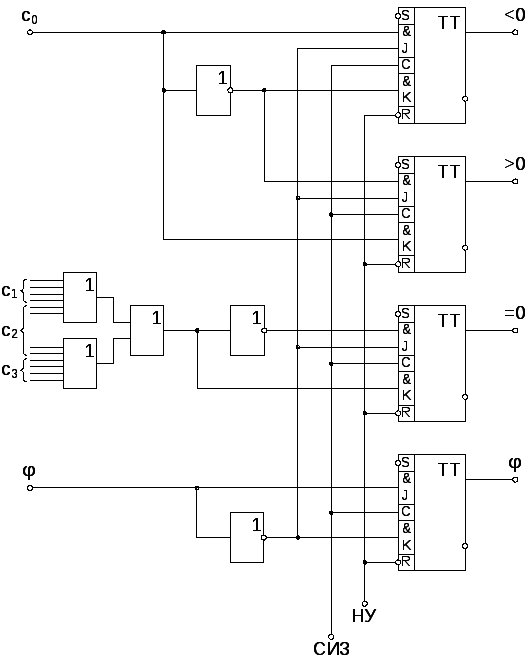

- •Разработка регистра признаков результата.

- •Расчет временных параметров устройства управления.

- •Общая структура схемы многоразрядного десятичного сумматора комбинационного типа с устройством управления.

Разработка регистра признаков результата.

Регистр признаков хранит информацию о результате работы устройства. Регистр состоит из 4 триггеров. Первый дает единицу, если результат отрицательный, второй — если положительный, третий — если равен нулю, четвертый — если произошло переполнение (при этом первые три триггера блокируются). Входными сигналами для первых двух триггеров является знак результата. Для триггера равенства результата нулю необходимый входной сигнал получается на комбинационной схеме, которая вырабатывает сигнал единицы, когда все значащие разряды (двоичные) результата равны нулю. Входным сигналом четвертого триггера является сигнал с выхода схемы переполнения.

Для блокировки первых трех триггеров в случае переполнения на входы Jэтих триггеров следует также подать инверсию сигнала со схемы, фиксирующей переполнение. На все четыре триггера на синхровходыCподается сигнал СИ3 от распределителя сигналов. На инверсные входыRподается сигнал НУ для перевода триггеров в начале выполнения операции в нулевое состояние.

Расчет временных параметров устройства управления.

Устройство, вырабатывающее управляющие сигналы СИ1, СИ1, СИ3 и СИ4, называется распределителем сигналов.

Распределитель сигналов имеет 4 выхода и предназначен для управления процессом работы устройства. Назначение сигналов, на каждом из четырех выходов распределителя:

первая ветка: сигнал подается на синхровход Cрегистров входов, происходит занесение данных в регистры;

вторая ветка: сигнал подается на синхровход Cрегистров выходов, происходит занесение данных в регистры;

третья ветка: сигнал подается на синхровход Cрегистра признаков, происходит занесение флагов окончания процесса в регистр;

четвертая ветка: сигнал подается на асинхронный вход Rтриггера пуска, происходит останов процесса.

Входными сигналами распределителя сигналов являются импульсы с генератора импульсов. Генератор вырабатывает импульсные сигналы длительностью 2 нсек со скважностью 1. Распределитель сигналов должен «выделить» из этой последовательности 4 сигнала с определенной временной задержкой между ними.

При проектировании подобного распределителя сигналов, в первую очередь необходимо определить временные интервалы Т1, Т2иT3.

Т1— характеризуется временем работы трехразрядного десятичного сумматора комбинационного типа. Для определения этой величины надо определить время задержки сигналов по каждой схеме, которая входит составной частью в общую схему.

Начнем с одноразрядного двоичного сумматора. Задержка по цепи вход-выход Р будет определяться тремя ЛЭ и равна 3 нсек. Задержка вход-выход S (по самой длинной цепи) будет определяться пятью ЛЭ и равна 5 нсек.

Расчет задержки сигналов в одноразрядном десятичном сумматоре. При определении этих значений необходимо исходить из общей картины работы сумматора. Будем анализировать самые «длинные цепи». Два слагаемых приходят на входы устройства, и есть перенос по всем 4 разрядам. Сигнал γ’8появится с задержкой 11 нсек (2 нсекx4 разр.). Далее сигнал проходит цепь коррекции и в точке Fкбудет с задержкой 14 нсек (11 нсек + 3 нсек). Следовательно, по выходу Пiзадержка будет 15 нсек. Далее сигнал идет через двоичные сумматоры ввода коррекции, и на выходеγ8появится через 26 нсек (15 нсек + 3 нсек + 3 нсек + 5 нсек).

Задержка в преобразователе будет 3 нсек (1 нсек x3 ЛЭ).

Расчет задержки сигналов в трехразрядном десятичном сумматоре также необходимо проводить, используя знания принципов сложения величин. При поступлении двух слагаемых на входы самой длинной цепью будет: прохождение операндов через преобразователи и поступление на сумматоры: со входов DC3 сигнал по Пiпойдет на вход Пi-1DC2; со входа Пi-1DC2 через выход ПiDC2 на вход Пi-1DC1; со входа Пi-1DC1 через ПiDC1 на вход учитывающего знак суммы сумматораSM; со входа сумматора через выходPна вход Пi-1DC3; со входа Пi-1DC3 на выходы этого сумматора и через выходной преобразователь на выходы устройства. Итого: 77 нсек (3 нсек + 14 нсек + 14 нсек + 14 нсек + 3 нсек + 26 нсек + 3 нсек).

Так как Т1должно быть кратно 4 (длительность импульса 2 нсек и промежуток между импульсами также 2 нсек) и более 77 нсек, то Т1= 80 нсек.

Временной интервал Т2определяется задержкой сигнала во входных цепях регистра признаков. Комбинационная схема на входе триггера, отвечающего за признак равенства нулю результата, имеет задержку 3 нсек, поэтому Т2= 4 нсек.

Величина Т3также равна 4 нсек, так как сигнал останова СИ4 идет непосредственно за сигналом СИ3.

Имея временные интервалы между выходными сигналами в распределителе сигналов, можно приступить к проектированию данного устройства. Распределитель сигналов является генератором следующих четырехразрядных двоичных чисел:

|

0001, |

0000, … , 0000 |

, 0010, 0100, 1000 |

|

|

|

|

|

19 раз |

Распределитель сигналов будет проектироваться на основе счётчика с пересчётом на 23 и комбинационной схемой на выходе. Для проектирования счётчика понадобиться 5 триггеров.

Составим таблицу переходов.

Таблица переходов

|

Такт n |

Такт n+1 |

Функции переходов |

Синхроимпульсы | ||||||||||||||||||||||

|

Q5n |

Q4n |

Q3n |

Q2n |

Q1n |

Q5n+1 |

Q4n+1 |

Q3n+1 |

Q2n+1 |

Q1n+1 |

F5 |

F4 |

F3 |

F2 |

F1 |

СИ4 |

СИ3 |

СИ2 |

СИ1 | |||||||

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

▲ |

0 |

0 |

0 |

1 | |||||||

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

▲ |

▼ |

0 |

0 |

0 |

0 | |||||||

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

▲ |

0 |

0 |

0 |

0 | |||||||

|

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

▲ |

▼ |

▼ |

0 |

0 |

0 |

0 | |||||||

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

▲ |

0 |

0 |

0 |

0 | |||||||

|

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

▲ |

▼ |

0 |

0 |

0 |

0 | |||||||

|

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

▲ |

0 |

0 |

0 |

0 | |||||||

|

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

▲ |

▼ |

▼ |

▼ |

0 |

0 |

0 |

0 | |||||||

|

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

▲ |

0 |

0 |

0 |

0 | |||||||

|

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

▲ |

▼ |

0 |

0 |

0 |

0 | |||||||

|

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

▲ |

0 |

0 |

0 |

0 | |||||||

|

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

▲ |

▼ |

▼ |

0 |

0 |

0 |

0 | |||||||

|

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

▲ |

0 |

0 |

0 |

0 | |||||||

|

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

▲ |

▼ |

0 |

0 |

0 |

0 | |||||||

|

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

▲ |

0 |

0 |

0 |

0 | |||||||

|

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

▲ |

▼ |

▼ |

▼ |

▼ |

0 |

0 |

0 |

0 | |||||||

|

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

▲ |

0 |

0 |

0 |

0 | |||||||

|

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

▲ |

▼ |

0 |

0 |

0 |

0 | |||||||

|

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

▲ |

0 |

0 |

0 |

0 | |||||||

|

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

▲ |

▼ |

▼ |

0 |

0 |

0 |

0 | |||||||

|

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

▲ |

0 |

0 |

1 |

0 | |||||||

|

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

▲ |

▼ |

0 |

1 |

0 |

0 | |||||||

|

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

▼ |

0 |

▼ |

▼ |

0 |

1 |

0 |

0 |

0 | |||||||

|

|

|

|

|

| |||||||||||||||||||||

|

|

|

|

| ||||||||||||||||||||||

|

|

|

|

| ||||||||||||||||||||||

|

|

|

|

| ||||||||||||||||||||||

|

|

|

|

| ||||||||||||||||||||||

|

|

|

|

| ||||||||||||||||||||||

|

|

|

|

| ||||||||||||||||||||||

|

|

|

|

| ||||||||

|

|

|

|

|

|

| ||||||

|

|

X |

X |

|

|

X |

X |

|

|

| ||

|

X |

X |

▲ |

|

X |

X |

|

|

| |||

|

|

1 |

X |

|

|

1 |

▼ |

|

| |||

|

1 |

1 |

|

|

1 |

1 |

|

|

| |||

|

|

|

|

|

|

|

| |||||

|

|

|

|

| ||||||||

|

|

|

|

|

|

| ||||||

|

|

X |

X |

|

|

X |

X |

|

|

| ||

|

X |

X |

1 |

|

X |

X |

|

|

| |||

|

|

X |

X |

|

|

X |

X |

|

| |||

|

X |

X |

|

|

X |

X |

|

|

| |||

|

|

|

|

|

|

|

| |||||

![]()

|

|

|

|

| ||||||||

|

|

|

|

|

|

| ||||||

|

|

X |

X |

|

|

X |

X |

|

|

| ||

|

X |

X |

▲ |

|

X |

X |

|

|

| |||

|

|

1 |

X |

|

|

1 |

▼ |

|

| |||

|

1 |

1 |

|

|

1 |

1 |

|

|

| |||

|

|

|

|

|

|

|

| |||||

![]()

|

|

|

|

| ||||||||

|

|

|

|

|

|

| ||||||

|

|

X |

X |

1 |

1 |

X |

X |

1 |

1 |

| ||

|

X |

X |

▼ |

1 |

X |

X |

1 |

1 |

| |||

|

|

|

X |

▲ |

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

| |||||

|

|

|

|

| ||||||||

|

|

|

|

|

|

| ||||||

|

|

X |

X |

X |

X |

X |

X |

X |

X |

| ||

|

X |

X |

X |

X |

X |

X |

X |

X |

| |||

|

|

|

X |

1 |

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

| |||||

![]()

|

|

|

|

| ||||||||

|

|

|

|

|

|

| ||||||

|

|

X |

X |

|

|

X |

X |

|

|

| ||

|

X |

X |

1 |

|

X |

X |

|

|

| |||

|

|

X |

X |

X |

X |

X |

X |

X |

X | |||

|

X |

X |

X |

X |

X |

X |

X |

X |

| |||

|

|

|

|

|

|

|

| |||||

![]()

|

|

|

|

| ||||||||

|

|

|

|

|

|

| ||||||

|

|

X |

X |

|

|

X |

X |

1 |

|

| ||

|

X |

X |

▼ |

▲ |

X |

X |

1 |

|

| |||

|

|

▲ |

X |

▼ |

▲ |

|

▼ |

1 |

| |||

|

|

1 |

1 |

|

|

1 |

1 |

|

| |||

|

|

|

|

|

|

|

| |||||

|

|

|

|

| ||||||||

|

|

|

|

|

|

| ||||||

|

|

X |

X |

X |

|

X |

X |

X |

|

| ||

|

X |

X |

X |

1 |

X |

X |

X |

|

| |||

|

|

1 |

X |

X |

1 |

|

X |

X |

| |||

|

|

X |

X |

|

|

X |

X |

|

| |||

|

|

|

|

|

|

|

| |||||

![]()

|

|

|

|

| ||||||||

|

|

|

|

|

|

| ||||||

|

|

X |

X |

|

X |

X |

X |

|

X |

| ||

|

X |

X |

1 |

X |

X |

X |

|

X |

| |||

|

|

X |

X |

1 |

X |

X |

1 |

|

X | |||

|

X |

|

|

X |

X |

|

|

X |

| |||

|

|

|

|

|

|

|

| |||||

МКНФ

|

|

|

|

| ||||||||

|

|

|

|

|

|

| ||||||

|

|

X |

X |

1 |

X |

X |

X |

1 |

X |

| ||

|

X |

X |

|

X |

X |

X |

1 |

X |

| |||

|

|

X |

X |

|

X |

X |

|

1 |

X | |||

|

X |

1 |

1 |

X |

X |

1 |

1 |

X |

| |||

|

|

|

|

|

|

|

| |||||

![]()

|

|

|

|

| ||||||||

|

|

|

|

|

|

| ||||||

|

|

X |

X |

▲ |

▲ |

X |

X |

|

|

| ||

|

X |

X |

▼ |

▼ |

X |

X |

1 |

1 |

| |||

|

|

▼ |

X |

▼ |

▼ |

1 |

▼ |

1 |

1 | |||

|

▲ |

▲ |

▲ |

▲ |

|

|

|

|

| |||

|

|

|

|

|

|

|

| |||||

|

|

|

|

| ||||||||

|

|

|

|

|

|

| ||||||

|

|

X |

X |

1 |

1 |

X |

X |

|

|

| ||

|

X |

X |

X |

X |

X |

X |

X |

X |

| |||

|

|

X |

X |

X |

X |

X |

X |

X |

X | |||

|

1 |

1 |

1 |

1 |

|

|

|

|

| |||

|

|

|

|

|

|

|

| |||||

![]()

|

|

|

|

| ||||||||

|

|

|

|

|

|

| ||||||

|

|

X |

X |

X |

X |

X |

X |

X |

X |

| ||

|

X |

X |

1 |

1 |

X |

X |

|

|

| |||

|

|

1 |

X |

1 |

1 |

|

1 |

|

| |||

|

X |

X |

X |

X |

X |

X |

X |

X |

| |||

|

|

|

|

|

|

|

| |||||

МКНФ

|

|

|

|

| ||||||||

|

|

|

|

|

|

| ||||||

|

|

X |

X |

X |

X |

X |

X |

X |

X |

| ||

|

X |

X |

|

|

X |

X |

1 |

1 |

| |||

|

|

|

X |

|

|

1 |

|

1 |

1 | |||

|

X |

X |

X |

X |

X |

X |

X |

X |

| |||

|

|

|

|

|

|

|

| |||||

![]()

|

|

|

|

| ||||||||

|

|

|

|

|

|

| ||||||

|

|

X |

X |

▼ |

▼ |

X |

X |

▲ |

▲ |

| ||

|

X |

X |

▼ |

▼ |

X |

X |

▲ |

▲ |

| |||

|

|

▼ |

X |

▼ |

▼ |

▲ |

|

▲ |

▲ | |||

|

▼ |

▼ |

▼ |

▼ |

▲ |

▲ |

▲ |

▲ |

| |||

|

|

|

|

|

|

|

| |||||

|

|

|

|

| ||||||||

|

|

|

|

|

|

| ||||||

|

|

X |

X |

X |

X |

X |

X |

1 |

1 |

| ||

|

X |

X |

X |

X |

X |

X |

1 |

1 |

| |||

|

|

X |

X |

X |

X |

1 |

|

1 |

1 | |||

|

X |

X |

X |

X |

1 |

1 |

1 |

1 |

| |||

|

|

|

|

|

|

|

| |||||

|

|

|

|

| ||||||||

|

|

|

|

|

|

| ||||||

|

|

X |

X |

X |

X |

X |

X |

|

|

| ||

|

X |

X |

X |

X |

X |

X |

|

|

| |||

|

|

X |

X |

X |

X |

|

1 |

|

| |||

|

X |

X |

X |

X |

|

|

|

|

| |||

|

|

|

|

|

|

|

| |||||

![]()

|

|

|

|

| ||||||||

|

|

|

|

|

|

| ||||||

|

|

X |

X |

1 |

1 |

X |

X |

X |

X |

| ||

|

X |

X |

1 |

1 |

X |

X |

X |

X |

| |||

|

|

1 |

X |

1 |

1 |

X |

X |

X |

X | |||

|

1 |

1 |

1 |

1 |

X |

X |

X |

X |

| |||

|

|

|

|

|

|

|

| |||||

![]()

|

|

|

|

| ||||||||

|

|

|

|

|

|

| ||||||

|

|

X |

X |

|

|

X |

X |

|

|

| ||

|

X |

X |

|

|

X |

X |

|

|

| |||

|

|

|

X |

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

1 |

| |||

|

|

|

|

|

|

|

| |||||

![]()

|

|

|

|

| ||||||||

|

|

|

|

|

|

| ||||||

|

|

X |

X |

|

|

X |

X |

|

|

| ||

|

X |

X |

|

|

X |

X |

|

|

| |||

|

|

|

X |

|

|

|

|

|

| |||

|

|

|

|

|

|

1 |

|

|

| |||

|

|

|

|

|

|

|

| |||||

![]()

|

|

|

|

| ||||||||

|

|

|

|

|

|

| ||||||

|

|

X |

X |

|

|

X |

X |

|

|

| ||

|

X |

X |

|

|

X |

X |

|

|

| |||

|

|

|

X |

|

|

|

|

|

| |||

|

|

1 |

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

| |||||

![]()

|

|

|

|

| ||||||||

|

|

|

|

|

|

| ||||||

|

|

X |

X |

|

|

X |

X |

|

|

| ||

|

X |

X |

|

|

X |

X |

|

|

| |||

|

|

|

X |

|

|

|

1 |

|

| |||

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

| |||||

![]()

По всем полученным логическим уравнения можно построить функциональную схему распределителя сигналов.