- •А. В. Шарапов

- •Содержание

- •1. Введение

- •2. Основные понятия микроэлектроники

- •2.1. Виды сигналов

- •2.2. Классификация микросхем и их условные обозначения

- •3. Математические основы цифровой электроники

- •3.1. Позиционные системы счисления

- •3.3. Совершенная дизъюнктивная нормальная форма

- •3.4. Основные законы булевой алгебры

- •Базовые логические элементы

- •4.1. Классификация логических элементов

- •4.2. Базовый элемент ттл

- •4.3. Логический расширитель

- •4.4. Элемент с открытым коллектором

- •4.5. Элемент с z-состоянием на выходе

- •4.7. Базовый элемент ттлш

- •4.8. Базовая схема эсл

- •4.9. Базовые элементы кмоп

- •4.10. Основные характеристики логических элементов

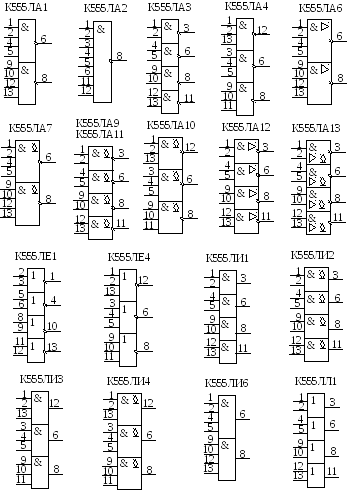

- •4.11. Примеры микросхем логических элементов

- •4.12. Микросхемы на основе арсенида галлия

- •5. Цифровые устройства комбинационного типа

- •5.1. Шифратор

- •5.2. Дешифратор

- •5.3. Преобразователи двоичного кода в двоично-десятичный и наоборот

- •5.4. Дешифратор для управления семисегментным

- •5.5. Преобразователи кода Грея

- •5.6. Мультиплексор

- •5.7. Реализация функций с помощью мультиплексора

- •5.8. Двоичный сумматор

- •5.9. Двоично-десятичный сумматор

- •5.10. Схемы вычитания

- •5.11. Преобразователь прямого кода в дополнительный

- •5.12. Цифровой компаратор

- •5.13. Контроль четности

- •5.14. Примеры построения комбинационных цифровых устройств

- •6. Цифровые устройства последовательностного типа

- •6.7.Классификация счетчиков

- •6.9. Асинхронный двоично-десятичный счетчик

- •Полупроводниковые запоминающие устройства

- •7.7. Примеры микросхем памяти

- •7.8. Организация блока памяти

- •8. Примеры решения задач

- •9. Компьютерный практикум по цифровой схемотехнике

- •Лабораторная работа №1

- •Исследование цифровых устройств

- •Комбинационного типа

- •Программа работы

- •Контрольные вопросы

- •Содержание отчета

- •Исследование цифровых устройств последовательностного типа

- •Пример синтеза счетчика

- •Пример оформления результатов моделирования

- •Программа работы Программа работы

- •Контрольные вопросы

- •Содержание отчета

- •10. Варианты творческих заданий

- •11. Пример выполнения творческого задания

- •Литература

11. Пример выполнения творческого задания

Задание. Спроектировать интегратор сигнала ошибки, формирующий 12-разрядный код управления Nу при подаче на его входы 12-разрядного кода задатчика Nз и 12-разрядного кода сигнала обратной связи Nос (рис. 11.1).

Решение. Структурная схема цифрового интегратора показана на рис. 11.2. Схема вычитания формирует модуль и знак сигнала ошибки. Частота импульсов на выходе преобразователя код-частота пропорциональна модулю сигнала ошибки и зависит от частоты тактового генератора G. Собственно интегратор выполнен на реверсивном двоичном счетчике. Направление интегрирования зависит от знака сигнала ошибки, скорость – от модуля сигнала ошибки. При совпадении кодов задатчика и сигнала обратной связи счет прекращается. На выходе реверсивного счетчика формируется код управления Nу.

Функциональная

схема проектируемого устройства

приведена на рис. 11.3. На входы 12-разрядного

сумматора подаются код задатчика Nз

и инверсный код сигнала обратной связи.

При Nз>Nос

формируется единичный сигнал переноса

Р,

элементы «Исключающее ИЛИ» работают

как повторители и

![]() ,

где

,

где![]() .

Сигнал с частотойf*N/212

поступает на суммирующий вход счетчика

и выходной код Nу

растет. Исполнительный орган системы

автоматического управления вызывает

рост регулируемой величины и растет

сигнал обратной связи, пока не будет

выполнено условие Nз=Nос.

Если счетчик достиг максимального

состояния Nу=4095

(единицы во всех 12 разрядах), а на

суммирующий вход продолжают поступать

счетные импульсы, в счетчике принудительно

фиксируется Nу=4095

(сигнал переноса загружает в него число

FFFH

со входов предустановки).

.

Сигнал с частотойf*N/212

поступает на суммирующий вход счетчика

и выходной код Nу

растет. Исполнительный орган системы

автоматического управления вызывает

рост регулируемой величины и растет

сигнал обратной связи, пока не будет

выполнено условие Nз=Nос.

Если счетчик достиг максимального

состояния Nу=4095

(единицы во всех 12 разрядах), а на

суммирующий вход продолжают поступать

счетные импульсы, в счетчике принудительно

фиксируется Nу=4095

(сигнал переноса загружает в него число

FFFH

со входов предустановки).

При

Nз≤Nос

логические элементы «Исключающее ИЛИ»

работают как инверторы (Р=0)

и

![]() .

Импульсы поступают на вычитающий вход

реверсивного счетчика, вызывая уменьшениеNу

и регулируемой величины. Если счетчик

достигает минимального кода Nу=0,

а на вычитающий вход продолжают поступать

счетные импульсы, сигнал заема (≤0)

принудительно сбрасывает счетчик в

нуль. Изменение частоты f

эквивалентно изменению постоянной

времени интегратора. Уменьшением f

можно добиться устойчивости замкнутой

системы автоматического регулирования.

.

Импульсы поступают на вычитающий вход

реверсивного счетчика, вызывая уменьшениеNу

и регулируемой величины. Если счетчик

достигает минимального кода Nу=0,

а на вычитающий вход продолжают поступать

счетные импульсы, сигнал заема (≤0)

принудительно сбрасывает счетчик в

нуль. Изменение частоты f

эквивалентно изменению постоянной

времени интегратора. Уменьшением f

можно добиться устойчивости замкнутой

системы автоматического регулирования.

ПРИЛОЖЕНИЕ

Условные графические обозначения микросхем