- •А. В. Шарапов

- •Содержание

- •1. Введение

- •2. Основные понятия микроэлектроники

- •2.1. Виды сигналов

- •2.2. Классификация микросхем и их условные обозначения

- •3. Математические основы цифровой электроники

- •3.1. Позиционные системы счисления

- •3.3. Совершенная дизъюнктивная нормальная форма

- •3.4. Основные законы булевой алгебры

- •Базовые логические элементы

- •4.1. Классификация логических элементов

- •4.2. Базовый элемент ттл

- •4.3. Логический расширитель

- •4.4. Элемент с открытым коллектором

- •4.5. Элемент с z-состоянием на выходе

- •4.7. Базовый элемент ттлш

- •4.8. Базовая схема эсл

- •4.9. Базовые элементы кмоп

- •4.10. Основные характеристики логических элементов

- •4.11. Примеры микросхем логических элементов

- •4.12. Микросхемы на основе арсенида галлия

- •5. Цифровые устройства комбинационного типа

- •5.1. Шифратор

- •5.2. Дешифратор

- •5.3. Преобразователи двоичного кода в двоично-десятичный и наоборот

- •5.4. Дешифратор для управления семисегментным

- •5.5. Преобразователи кода Грея

- •5.6. Мультиплексор

- •5.7. Реализация функций с помощью мультиплексора

- •5.8. Двоичный сумматор

- •5.9. Двоично-десятичный сумматор

- •5.10. Схемы вычитания

- •5.11. Преобразователь прямого кода в дополнительный

- •5.12. Цифровой компаратор

- •5.13. Контроль четности

- •5.14. Примеры построения комбинационных цифровых устройств

- •6. Цифровые устройства последовательностного типа

- •6.7.Классификация счетчиков

- •6.9. Асинхронный двоично-десятичный счетчик

- •Полупроводниковые запоминающие устройства

- •7.7. Примеры микросхем памяти

- •7.8. Организация блока памяти

- •8. Примеры решения задач

- •9. Компьютерный практикум по цифровой схемотехнике

- •Лабораторная работа №1

- •Исследование цифровых устройств

- •Комбинационного типа

- •Программа работы

- •Контрольные вопросы

- •Содержание отчета

- •Исследование цифровых устройств последовательностного типа

- •Пример синтеза счетчика

- •Пример оформления результатов моделирования

- •Программа работы Программа работы

- •Контрольные вопросы

- •Содержание отчета

- •10. Варианты творческих заданий

- •11. Пример выполнения творческого задания

- •Литература

5.7. Реализация функций с помощью мультиплексора

Мультиплексоры удобно использовать для реализации логических функций, записанных непосредственно в СДНФ. Любую булеву функцию четырех переменных можно реализовать с помощью восьмиканального мультиплексора. Так, для реализации, например, логической функции

![]() ,

,

г деD – переменная младшего разряда,

на адресные входы мультиплексора

К555КП7 поданы входные сигналыА,В,

С,а входыХ0 – Х7 используются

как настроечные (рис. 5.12,а). Сравнивая

выражение для функцииFc логическим

уравнением мультиплексора

деD – переменная младшего разряда,

на адресные входы мультиплексора

К555КП7 поданы входные сигналыА,В,

С,а входыХ0 – Х7 используются

как настроечные (рис. 5.12,а). Сравнивая

выражение для функцииFc логическим

уравнением мультиплексора

![]()

получаем условия эквивалентности:

X0

= X3 =

![]() ,

X7 = D, X5

=

,

X7 = D, X5

=![]() + D =1, X1

= X2 = X4

= X6 = 0.

+ D =1, X1

= X2 = X4

= X6 = 0.

Эти соотношения позволяют зашифровать входы мультиплексора на выполнение заданного логического уравнения.

В соответствии с этими условиями

построена схема устройства (рис. 5.12, б).

Для подачи логической 1 входы микросхем

ТТЛШ серий К555 и КР1533 можно подключать

к источнику питания +5В непосредственно.

Для получения сигнала

![]() использован инвертор.

использован инвертор.

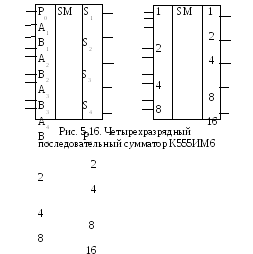

5.8. Двоичный сумматор

Д воичный

сумматор(SM) (рис.

5.13,а) служит для формирования

арифметической суммыn-разрядных

двоичных чиселАиВ(рис. 5.12,б).

Результатом сложения (приn= 4) является четырехразрядная суммаSи выход переносаР, который можно

рассматривать как пятый разряд суммы.

воичный

сумматор(SM) (рис.

5.13,а) служит для формирования

арифметической суммыn-разрядных

двоичных чиселАиВ(рис. 5.12,б).

Результатом сложения (приn= 4) является четырехразрядная суммаSи выход переносаР, который можно

рассматривать как пятый разряд суммы.

П олусумматор(HS) служит для

сложения битов младших разрядов

двух двоичных чисел (его можно реализовать

на ЛЭ по таблице истинности,

представленной на рис. 5.14).

олусумматор(HS) служит для

сложения битов младших разрядов

двух двоичных чисел (его можно реализовать

на ЛЭ по таблице истинности,

представленной на рис. 5.14).

Полный одноразрядный сумматорсуммирует биты соответствующих разрядов двух двоичных чисел и вырабатывает перенос в следующий разряд.

Полный одноразрядный сумматор можно построить из двух полусумматоров HS и логического элемента ИЛИ (рис. 5.15).

В корпусе микросхемы К555ИМ6 четыре полных одноразрядных сумматора объединены в схему четырехразрядного сумматора (рис. 5.16). Сигнал переноса последовательно передается с выхода предыдущего разряда сумматора на вход переноса следующего разряда. В дальнейшем будем использовать более простое и наглядное условное графическое обозначение сумматора, приведенное справа. В дополнительных полях микросхемы показаны весовые коэффициенты разрядов входа и выхода сумматора.

В ремя

выполнения операции в сумматоре на рис.

5.16 намного больше времени сложения в

одноразрядном сумматоре, так как в

каждый следующий разряд единица переноса

попадает, проходя все более длинную

цепочку логических элементов. Чтобы

уменьшить время выполнения операции

сложения многоразрядных чисел, используют

схемы параллельного переноса. При этом

сигналы переноса во всех разрядах

одновременно вычисляются по значениям

входных переменных в данном разряде.

ремя

выполнения операции в сумматоре на рис.

5.16 намного больше времени сложения в

одноразрядном сумматоре, так как в

каждый следующий разряд единица переноса

попадает, проходя все более длинную

цепочку логических элементов. Чтобы

уменьшить время выполнения операции

сложения многоразрядных чисел, используют

схемы параллельного переноса. При этом

сигналы переноса во всех разрядах

одновременно вычисляются по значениям

входных переменных в данном разряде.

Для сигнала переноса из любого k-го разряда справедливо соотношение (см. обозначения на рис. 5.15)

pk = akbk + (ak bk)pk-1, (5.2)

gk сk

где gk - функция генерации переноса;

сk- функция распространения переноса.

Пользуясь рекуррентным выражением (5.2), можно вывести следующие формулы для вычисления сигналов переноса в четырехразрядном сумматоре:

p1 = g1 + p0c1,

p2 = g2 + p1c2 = g2 + c2g1 +p0c1c2,

p3 = g3+ p2c3 = g3 + c3g2 + c2c3g1 + p0c1c2c3 ,

p4 = g4 + p3c4 = (g4 + c4g3 + c3c4g2 + c2c3c4g1) + p0(c1c2c3 c4).

GC

Реализацию этих функций выполняет схема ускоренного переноса (см.блок-схему параллельного сумматора на рис. 5.17). Хотя полученные логические выражения достаточно сложны, время формирования сигнала переноса в любой разряд с помощью вспомогательных функций определяется временем задержки распространения сигнала в двух элементах.

Д ля

построения 16-разрядного сумматора

используется эта же схема ускоренного

переноса, на которую подаются сигналыGиСот каждого

четырехразрядного сумматора.

ля

построения 16-разрядного сумматора

используется эта же схема ускоренного

переноса, на которую подаются сигналыGиСот каждого

четырехразрядного сумматора.