- •ОБразования российской федерации

- •Цель работы

- •Теоретическая часть

- •Типы адресов

- •Механизмы страничной переадресации

- •Базовый механизм страничной переадресации

- •Режимы psEиPse-36

- •РежимPae

- •Буфер ассоциативной трансляции тlb

- •TlBс полностью ассоциативным распределением строк.

- •TlBс наборно-ассоциативным распределением строк

- •Порядок выполнения работы

- •Вопросы для самопроверки (защиты л/р)

- •TlBс полностью ассоциативным распределением строк.

- •TlBс наборно-ассоциативным распределением строк

- •Список литературы

РежимPae

Все процессоры i686 поддерживают расширение физического адреса (PhysicalAddressExtensions) до 64 Гбайт, которое включается установкой бита РАЕ в регистреCR4. Здесь блок страничной переадресации оперирует уже 64-разрядными элементами таблиц трансляции (рис. 11, 12, 13, 14). При этом расширение режимаPSEстановится недоступным (битPSEигнорируется).

Рис. 11.PDPTE– строка таблицы указателей на каталоги

Рис. 12. Строка PDEкаталога страниц для страницы 4 Кбайт

Рис. 13. СтрокаPTEтаблицы для страниц 4 Кбайт

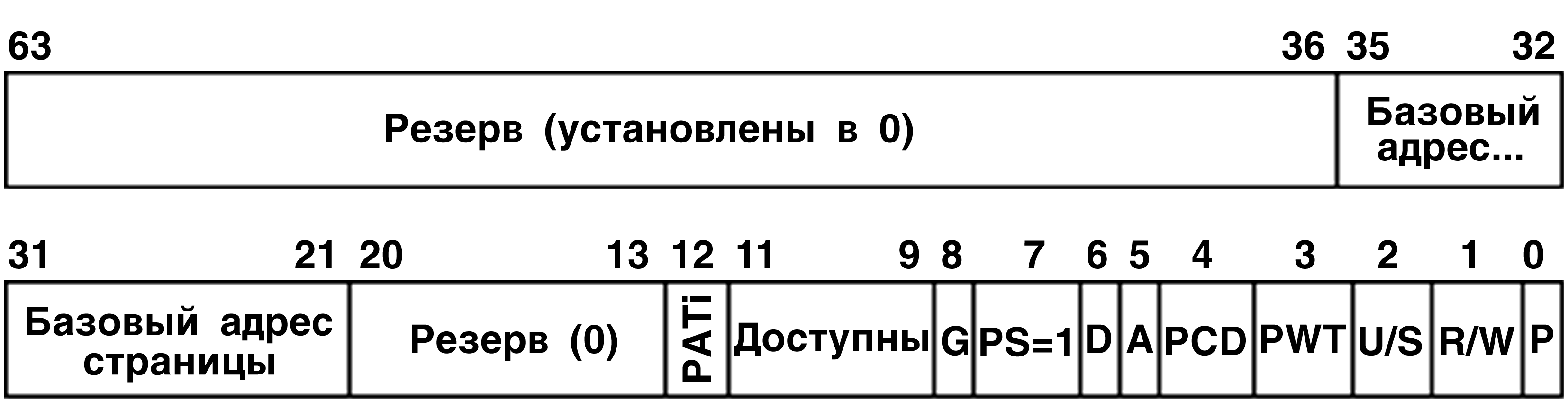

Рис. 14. Строка PDEкаталога страниц для страниц размером 2 Мбайт

Механизм страничной переадресации РАЕ использует трёх- или двух- уровневую табличную трансляцию линейного адреса в физический (рис. 15 и 16).

Рис. 15. Страничная переадресация в режимеPAE для страниц размером 2 Мбайт

Рис. 16. Страничная переадресация в режимеPAE для страниц размером4 Кбайт

32-разрядный регистр CR3 хранит указатель на маленькую (4 строки) таблицу трансляциипервого уровня–таблицу указателей (PDPT–PageDirectoryPointerTable), находящуюся в первых 4Гбайтах памяти. Два старших разряда ЛА[31÷30] линейного адреса выбирают из этой таблицы указатель на одну из 4 таблиц каталогов. Каждая строка этой таблицы (рис. 11) содержит 24 старших разряда (младшие биты этого адреса всегда нулевые) базового адреса таблицы трансляции следующеговторого уровня–каталога страниц(PD) размером 16 Кбайт. Каждый каталогPDсодержит 512 64-разрядных строки (PDE), см. рис. 12 и 14.PDEсодержит 24 старших разряда адреса

либо самой страницы (РАЕ 2Мб). В этом случае в строке РDЕ[35÷21] хранятся старшие разряды базового адреса страницы, а оставшиеся 21 разряд линейного адреса (ЛА[20÷0]) содержат смещение внутри страницы.

либо таблицы трансляции следующего третьего уровня – таблицы страниц и признаки (атрибуты) этой таблицы (РАЕ 4Кб). Индексом поиска в каталоге страниц являются 9 старших бит линейного адреса (ЛА[20÷12]). В этом случае в строке РТЕ[35÷12] хранятся старшие разряды базового адреса страницы, а оставшиеся 12 разрядов линейного адреса (ЛА[11÷0]) содержат смещение внутри страницы.

Режимы переадресации:

При CR4.PAE=1 иPDE.PS=0 разряды [12÷20] линейного адреса выбирают дескриптор страницы, размером 4 Кбайт, из таблицы страниц, а разряды [0÷11] являются смещением в этой странице, (режимРАЕ 4 Кбайт).

При CR4.PAE=1 иPDE.PS=1 биты [20÷0] линейного адреса являются смещением внутри страницы размером 2 Мбайт (режимРАЕ 2 Мбайт).

Схемы страничного преобразования для режима РАЕ приведены на рис. 15 и 16соответственно.

Буфер ассоциативной трансляции тlb

При каждой операции доступа к памяти с использованием механизмов страничной переадресации приходится обращаться к двум или даже более таблицам (PD– каталогу страниц,PT– таблице страниц и т.д.), расположенным в медленной оперативной памяти, что существенно снижает быстродействие. Для предотвращения этого замедления в процессор введенбуфер ассоциативной трансляцииТLB(TranslationLookasideBuffer) для хранения интенсивно используемых строк таблиц1. В процессоре Pentium имеются раздельные TLB для инструкций и данных, а в процессорах i686 буферы разделены еще и по размеру обслуживаемых страниц (4Кбайт и 2Мбайт/4 Мбайт).

Когда страничное управление разрешено (бит CR0.PG=1), блок страничной переадресации получает 32-разрядный линейный адрес от блока сегментации. Этот адрес может рассматриваться как пара: адрес виртуальной страницы и адрес данных внутри страницы. Он должен быть преобразован в абсолютный физический адрес данных, который, в свою очередь можно рассматривать как адресную пару: старшие разряды – адрес физической страницы, младшие разряды – адрес данных внутри страницы (см. рис.17). Вторая часть этих пар неизменна, и каждой виртуальной странице соответствует какая-то физическая страница. ВTLBзапоминаются данные о недавно использованных физических страницах. В качестве поискового признака вTLBлогично было бы использовать виртуальный адрес страницы (старшие разряды линейного адреса – ВВ=32–offset, см. рис.17), что и происходит на практике. Если соответствующая запись найдена вTLB(попадание), то физический адрес данных вычисляется по начальному адресу страницы, полученному из ТBL(ХХ, см. рис.17), а затем выводится на шину адреса. В случае промаха блок страничной переадресации формирует физический адрес по используемому механизму и попутно заносит в ТBLнужную строку таблицы трансляции (PDЕ илиPTЕ).

Рис.17. Механизм формирования физического адреса с использованием TLB или БСП

По сути TLBявляется кэш-элементом и информация запоминается в нём с использованием тех же принципов, что и для любой кэш-памяти. В 32-разрядных процессорахIntelиспользуютсяTLBс полностью ассоциативным отображением строк ОП, частично-ассоциативным (наборно-ассоциативным) отображением. Каждому типуTLB(инструкций, данных, больших страниц) соответствует свой тип отображения. Для простоты будем рассматривать однородные КЭШ.

№ виртуальной страницы – старшие разряды линейного адреса (их число зависит от механизма страничной переадресации и выделено на всех схемах закрашенной областью) сравниваются со значениями памяти тегов из TLB, и, в случае совпадения, физический адрес вычисляется по информации, полученной из ТBL, а затем выводится на шину адреса. ВTLBестьvalidбит, который отвечает за правильность данных, содержащихся в соответствующей строке. Если строки вTLBнет (не найдено совпадение в памяти тегов) или битvalidв ней сброшен, осуществляется цикл работы БСП согласно используемому механизму страничной переадресации. Затем новое соответствие виртуальной и физической страницы (двойное слово из таблицы страницPTEили страничного каталогаPDE) заносится вTLB(см. рис.18, 19).

Рассмотрим два типа распределения информации в КЭШ.