- •5. Задание на дом для самостоятельной работы.

- •Процессоры

- •История развития

- •2. Центральный процессор

- •2.1. Процессор 80086

- •2.2. Процессор 80286

- •2.3. Процессор 80286

- •2.4. Процессор 80386

- •2.5. Процессор 80486

- •2.6. Процессор Pentium I

- •2.7. Процессор Pentium II

- •2.8. Процессор Pentium III

- •2.9. Процессор Pentium IV

- •2.10. Расширение ммх

- •3.Архитектура фон Неймана

- •3.1. Конвейерная архитектура

- •3.2. Суперскалярная архитектура

- •3.3. Cisc-процессоры

- •3.4. Risc-процессоры

- •3.5. Misc-процессоры

- •3.6. Vliw-процессоры

- •3.7. Многоядерные процессоры

- •3.8. Кэширование

- •Гарвардская архитектура

- •4.1. Классическая гарвардская архитектура

- •4.2. Модифицированная гарвардская архитектура

- •4.3. Расширенная гарвардская архитектура

- •5. Параллельная архитектура

- •5.1. Цифровая обработка сигналов

- •6. Энергопотребление процессоров

- •7. Технология изготовления процессоров

- •7.1. История развития процессоров

- •7.2. Современная технология изготовления

- •8. Перспективы процессоров

- •Принцип работы памяти sdram

3.8. Кэширование

Кэширование — это использование дополнительной быстродействующей памяти (кэша) для хранения копий блоков информации из основной (оперативной) памяти, вероятность обращения к которым в ближайшее время велика.

Различают кэши 1-, 2- и 3-го уровней (обозначаются L1, L2 и L3 — от Level 1, Level 2 и Level 3). Кэш 1-го уровня имеет наименьшую латентность (время доступа), но малый размер, кроме того, кэши первого уровня часто делаются многопортовыми. Так, процессоры AMD K8 умели производить одновременно 64-битные запись и чтение, либо два 64-битных чтения за такт, AMD K8L может производить два 128-битных чтения или записи в любой комбинации. Процессоры Intel Core 2 могут производить 128-битные запись и чтение за такт. Кэш 2-го уровня обычно имеет значительно большую латентность доступа, но его можно сделать значительно больше по размеру. Кэш 3-го уровня самый большой по объёму и довольно медленный, но всё же он гораздо быстрее, чем оперативная память.

Гарвардская архитектура

Г арвардская

архитектура —архитектура ЭВМ,

отличительным признаком которой является

раздельное хранение и обработка команд

и данных. Архитектура была разработана

Говардом Эйкеном в конце 1930-х годов в

Гарвардском университете.

арвардская

архитектура —архитектура ЭВМ,

отличительным признаком которой является

раздельное хранение и обработка команд

и данных. Архитектура была разработана

Говардом Эйкеном в конце 1930-х годов в

Гарвардском университете.

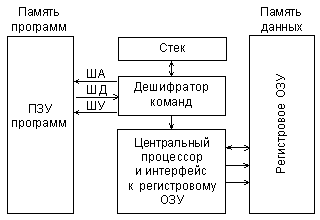

Гарвардская архитектура отличается от архитектуры фон Неймана тем, что программный код и данные хранятся в разной памяти. В такой архитектуре невозможны многие методы программирования (например, программа не может во время выполнения менять свой код; невозможно динамически пе рераспределять память между программным кодом и данными); зато гарвардская архитектура позволяет более эффективно выполнять работу в случае ограниченных ресурсов, поэтому она часто применяется во встраиваемых системах.

4.1. Классическая гарвардская архитектура

Типичные операции (сложение и умножение) требуют от любого вычислительного устройства нескольких действий: выборку двух операндов, выбор инструкции и её выполнение, и, наконец, сохранение результата. Идея, реализованная Эйкеном, заключалась в физическом разделении линий передачи команд и данных. В первом компьютере Эйкена «Марк I» для хранения инструкций использовалась перфорированная лента, а для работы с данными — электромеханические регистры. Это позволяло одновременно пересылать и обрабатывать команды и данные, благодаря чему значительно повышалось общее быстродействие.

4.2. Модифицированная гарвардская архитектура

Соответствующая схема реализации доступа к памяти имеет один очевидный недостаток — высокую стоимость. При разделении каналов передачи команд и данных на кристалле процессора последний должен иметь почти в два раза больше выводов (так как шины адреса и данных составляют основную часть выводов микропроцессора). Способом решения этой проблемы стала идея использовать общую шину данных и шину адреса для всех внешних данных, а внутри процессора использовать шину данных, шину команд и две шины адреса. Такую концепцию стали называть модифицированной Гарвардской архитектурой.

Такой подход применяется в современных сигнальных процессорах. Еще дальше по пути уменьшения стоимости пошли при создании однокристалльных ЭВМ — микроконтроллеров. В них одна шина команд и данных применяется и внутри кристалла.

Разделение шин в модифицированной Гарвардской структуре осуществляется при помощи раздельных управляющих сигналов: чтения, записи или выбора области памяти.