336 ЛЕКЦИИ И ВОПРОСЫ К ЗАЧЕТУ / ЛЕКЦИИ / Лекция №9-10 - Запоминающие устройства, ЗУМП

.doc

ЛЕКЦИЯ №9

ЗАПОМИНАЮЩИЕ УСТРОЙСТВА

Запоминающие устройства (ЗУ) предназначены для хранения информации, выраженной двоичными числами. Такая информация заносится (записывается) в ЗУ и в нужные моменты из него выбирается (считывается).

ЗУ – один из основных функциональных блоков электронных цифровых вычислительных машин; в нем хранятся числа, над которыми должны быть произведены определенные действия, и числа – коды команд, определяющие характер этих действий.

ЗУ состоит из запоминающего массива и электронного обрамления. Запоминающий массив (накопитель) содержит запоминающие элементы (ЗЭ), каждый из которых может принимать состояния логической 1 или логического 0, т.е. хранить один бит информации. В запоминающем элементе хранится один разряд записанного двоичного слова; все п-разрядное слово записывается в запоминающих элементах, составляющих ячейку памяти. Ей соответствует определенный адрес, характеризующий положение этой ячейки в накопителе. Запись и считывание слова (обращение к ЗУ) производятся по адресу, которым выбирается определенная ячейка. Запоминающие элементы должны обладать двумя устойчивыми состояниями. К числу таких элементов относятся ферромагнитные сердечники с прямоугольной петлей гистерезиса (магнитные ЗУ) и триггеры (полупроводниковые ЗУ).

Электронное обрамление содержит, в частности, дешифраторы адреса и усилители записи и считывания. Код адреса, поступающий на входы дешифратора, возбуждает один из его выходов; этим разрешается запись слова в определенные ЗЭ или считывание из них.

Из многих параметров ЗУ отметим информационную емкость и быстродействие.

Информационная емкость определяется количеством запоминающих элементов накопителя и оценивается числом битов хранимой информации. Более крупными единицами емкости являются байт (равный 8 бит), килобит (Кбит=210=1024 бит), килобайт, мегабит (Мбит=220 бит), мегабайт. Быстродействие ЗУ оценивается временем полного цикла обращения – минимально допустимым временем между двумя последовательными обращениями к ЗУ.

По характеру и использованию записанной информации ЗУ делятся на оперативные (ОЗУ) и постоянные (ПЗУ).

Оперативные запоминающие устройства. К оперативным относят ЗУ с относительно кратковременным хранением часто сменяющейся информации.

Существует несколько способов объединения запоминающих элементов в накопителе (несколько видов организации ЗУ).

ЗУ с однокоординатной выборкой. Организация ЗУ, при которой одной линией выбирается группа запоминающих элементов (группа разрядов одного слова), называется словарной или однокоординатной. Упрощенная структура ЗУ с однокоординатной выборкой приведена на рис. 9.1.

Запоминающий массив (ЗМ) представляет собой матрицу, в каждой строке которой располагаются ЗЭ, хранящие разряды одного слова. В каждом столбце матрицы находятся ЗЭ, хранящие одноименные разряды всех слов. В ЗМ (рис. 9.1) могут быть зафиксированы четыре четырехразрядных слова, т.е. его емкость равна 16 бит.

Рис. 9.1. Упрощенная структура ЗУ с однокоординатной выборкой

Для записи слова, к примеру, в ячейку из элементов ЗЭ9-ЗЭ12 нужно подать сигнал выбора адреса на адресную линию ЛА (которая подключена только к элементам ЗЭ9-ЗЭ12); сигналы, соответствующие значениям разрядов (0 или 1) записываемого слова, подать на разрядные линии ЛР1-ЛР4, а на линию Зп/Сч, общую для всех ЗЭ, подать сигнал, разрешающий запись. При этом ЗЭ (в данном случае третьей строки матрицы) переключаются в состояния, соответствующие значениям разрядов.

Считывание слова происходит при отсутствии на шине Зп/Сч сигнала, разрешающего запись, и при подаче сигнала на требуемую адресную шину. При этом потенциалы, соответствующие значениям разрядов слова (0 или 1), появляются на выходах разрядных усилителей считывания.

Выбор той или иной адресной линии (ЛА) производится дешифратором адреса, на вход которого поступает двоичный код номера ЛА – номера ячейки, в которую должно быть записано или из которой должно быть считано слово. Отметим, что ячейка, в которую записывается или из которой считывается слово, имеет одну координату. Ею является номер строки матрицы запоминающих элементов.

Описанное ЗУ называют также двумерным ЗУ (запоминающие элементы расположены в одной плоскости), ЗУ типа 2D.

На рис. 9.2, а приведено условное изображение микросхемы ОЗУ. Она имеет 16 запоминающих ячеек, каждая из которых может выбираться комбинацией двоичных переменных на четырех адресных входах А0-АЗ (24=16). Ячейка имеет четыре разряда (бита). Запись в нее осуществляется по входам D0-D3 при наличии на входе запись/чтение (W/R) логической 1 (W/R=1), а считывание производится с выходов Q0-Q3 при W/R=0. Инициализация (ввод в действие, выбор) микросхемы осуществляется логической 1 по входу СS. При СS=0 микросхема блокируется.

Рис. 9.2. Условное изображение микросхемы ОЗУ

У многих типов микросхем ОЗУ входы W/R и СS – инверсные (рис. 9.2, б), для которых активный уровень сигнала – логический 0. Он производит выбор микросхемы и разрешает запись в нее данных. При этом чтение данных из микросхемы осуществляется по сигналу W/R=1.

ЗУ с двухкоординатной выборкой. Число выходов дешифратора и адресных линий внутри микросхемы равно количеству ячеек в накопителе (см. рис. 9.1) и может быть весьма значительным, что технологически ограничивает емкость памяти в пределах кристалла. Так, при 1000 ячеек это число равно 1024. Его можно значительно уменьшить, если использовать двухкоординатную. адресацию.

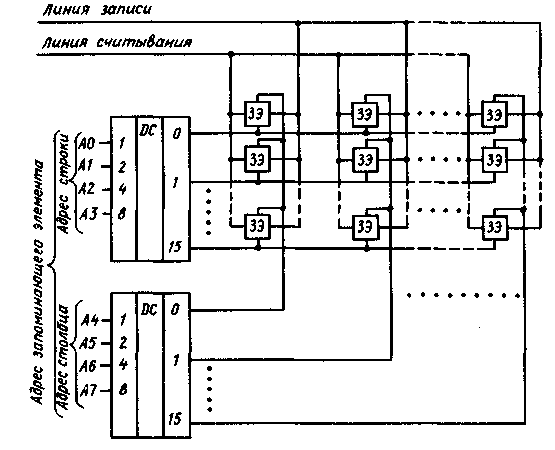

В этом случае каждый запоминающий элемент матрицы выбирается дешифратором строки и дешифратором столбца (рис. 9.3). При этом выбранным оказывается элемент, находящийся на пересечении возбужденных линий, одна из которых принадлежит дешифратору строки, а другая – дешифратору столбца.

Каждая такая двухкоординатная матрица хранит одноименные разряды всех записываемых слов (одна матрица – первые разряды, другая – вторые и т.д.), а все k-разрядное слово хранится в k матрицах. Информационные выводы D и Q на рис. 9.3 не показаны.

Предположим, что в двухкоординатную матрицу надо занести информацию, которая содержалась в одном столбце однокоординатной матрицы с числом ячеек 1000, т.е. в двухкоординатной матрице надо адресовать 1024 находящихся в ней запоминающих элемента (ЗЭ). Это можно обеспечить адресными линиями дешифраторов строк и столбцов, каждый из которых имеет 32 вывода (1024=32х32), что существенно меньше 1024. При этом каждый ЗЭ должен содержать элемент И, регистрирующий одновременно возбужденные линии строки и столбца.

Рис. 9.3. Упрощенная структура ЗУ с двухкоординатной выборкой

Одна часть разрядов адреса, установленного на входах А0-А9 (210=1024), поступает на входы дешифратора строк, другая – на входы дешифратора столбцов. Если матрица накопителя квадратная, то разряды полного адреса распределяются между дешифраторами поровну.

Микросхемами с описанной организацией составляется модуль на требуемое число разрядов. На рис. 9.4 показан модуль ОЗУ, состоящий из восьми микросхем S0-S7 с описанной структурой. Десять адресных входов А0-А9 позволяют выбирать один из 1024 запоминающих элементов, запись в который производится по входу D, а считывание – с выхода Q. Адресные входы всех микросхем запараллелены, поэтому каждая комбинация на них адресует (выбирает) восемь ЗЭ, идентично расположенных в восьми накопительных матрицах, т.е. выбирает восьмиразрядное слово – один байт. Полная емкость модуля составляет 1024 восьмиразрядных слов – 1 Кбайт. Все входы выбора микросхем (СS) соединены, поэтому обращение к ним происходит как к единому блоку. Соединены и все входы W/R записи/чтения, поэтому в каждой из этих операций одновременно участвуют все восемь микросхем.

Рис. 9.4. Модуль ОЗУ

Некоторые типы микросхемы ОЗУ имеют двунаправленные входы данных, через которые можно вводить или выводить информацию. Это дополнительно уменьшает число соединительных линий в кристалле. В структуре таких микросхем имеются выходные буферы с тремя состояниями. Одни из них пропускают данные на запись и блокируются сигналом «Чтение», другие пропускают считываемые данные и блокируются сигналом «Запись».

Большинство типов используемых микросхем ОЗУ энергозависимо: при отключении питания записанная информация теряется. В настоящее время разработаны и выпускаются промышленностью микросхемы ОЗУ на базе МНОП-транзисторов, сохраняющие информацию в течение тысяч часов.

Запоминающий элемент. Запоминающие элементы накопителя ОЗУ могут быть статическими и динамическими.

Статическим ЗЭ является триггер, динамическим – емкость затвор-подложка МОП-транзистора. Заряд этой емкости соответствует одному состоянию ЗЭ, отсутствие заряда – другому состоянию. Так как емкость постоянно разряжается, то динамическая память нуждается в систематической регенерации (восстановлении), осуществляемой с периодом в несколько миллисекунд специальным внешним устройством. В ряде случаев этот недостаток компенсируется большим достижимым объемом памяти в кристалле и значительно меньшим потреблением энергии по сравнению со статическими ОЗУ.

На рис. 9.5 изображена часть ЗУ с однокоординатной выборкой. Она представлена двумя запоминающими элементами для хранения двух разрядов одного слова. Запоминающий элемент является триггером на биполярных транзисторах с непосредственными связями. Будем считать, что в ЗЭ записан 0, если отперт VТ1 и заперт VТ2. От +Ек к -Ек (к «земле») через отпертый транзистор триггера ток может проходить через цепи эмиттеров. Верхние по схеме эмиттеры подключены к разрядным линиям, нижние соединены и выведены на адресную линию. При выборке ячейки, в которую входят рассматриваемые ЗЭ, данная адресная линия возбуждается – ее потенциал возрастает и цепь тока через нижние эмиттеры обрывается.

Рис. 9.5. ЗУ с однокоординатной выборкой

В режиме хранения ЗЭ не выбраны – адресная линия имеет низкий потенциал, а разрядные – более высокий. Поэтому ток отпертого транзистора протекает через нижний эмиттер на адресную линию и по ней на «землю».

В режиме записи происходит выборка запоминающих элементов ячейки – данная адресная линия приобретает высокий потенциал и ток отпертого транзистора ЗЭ может протекать только на разрядную линию.

При появлении на входе двоичной переменной, записываемой в данный ЗЭ, и сигнала разрешения записи одна разрядная линия (например, ЛР1) получает высокий потенциал, а другая (линия ЛР1) благодаря инвертору – низкий. Если перед этим триггер находился в состоянии 0 (VТ1 отперт), то он переключается в состояние 1 (отперт VТ2).

В режиме считывания вновь происходит выборка запоминающих элементов ячейки: адресная линия получает высокий потенциал, и ток открытого транзистора протекает по разрядной линии на один из входов усилителя считывания. На его выходе появляется логическая 1, если отперт VТ2, и логический 0, если отперт VТ1.

Аналогичный запоминающий элемент для ЗУ с двухкоординатной выборкой (рис. 9.6) представляет собой триггер на трехэмиттерных транзисторах. Третьи эмиттеры каждого транзистора соединены и выведены на вторую адресную линию.

Рис. 9.6. ЗУ с двухкоординатной выборкой

Постоянные запоминающие устройства. Постоянные запоминающие устройства (ПЗУ) используют для хранения программ, по которым многократно будет работать ЭВМ, стандартных программ и т.д.

Выпускаются постоянные запоминающие устройства однократно программируемые на заводе-изготовителе (ПЗУ) или пользователем (ППЗУ) и перепрограммируемые, иначе называемые репрограммируемыми (РПЗУ). Процесс перепрограммирования РПЗУ занимает значительное время, т.е. и в РПЗУ смена занесенной информации не происходит оперативно. Таким образом, все постоянные запоминающие устройства работают только на считывание.

Полупроводниковые ПЗУ могут быть диодными и транзисторными.

На рис. 9.7, а изображено ПЗУ, состоящее из диодной матрицы и дешифратора адреса. Горизонтальные линии матрицы – адресные; вертикальные – разрядные, с них снимаются восьмиразрядные двоичные числа, записанные в ПЗУ. Код адреса возбуждает одну из адресных линий матрицы. Диоды в ней расположены так, чтобы обеспечить ее соединение с теми разрядными линиями, на которых нужно получить логические единицы. Если, к примеру, с выхода дешифратора возбуждается адресная линия А1, то логическая 1 проходит с нее через диоды на разрядные линии Р1, Р5, Р6, Р7, сообщая им высокий потенциал – на выходе устанавливается двоичное число 11100010. Аналогично, при возбуждении соответствующих адресных линий на выходах устанавливаются три других двоичных числа.

Рис. 9.7. Схема ПЗУ: а) – диодный мост; б) – многоэмиттерный транзистор

На рис. 9.7, б приведена структура микросхемы ПЗУ на многоэмиттерных транзисторах. При возбуждении одной из адресных линий отпирается транзистор, база которого присоединена к этой линии. Благодаря этому возбуждаются те разрядные линии, к которым присоединены эмиттеры этого транзистора. В ПЗУ (рис. 9.7, б) записаны три четырехразрядных слова (1001, 0011, 1010), каждое устанавливается на разрядных линиях при возбуждении соответствующей адресной линии. При изготовлении таких микросхем все эмиттеры соединяются с разрядными линиями через плавкие перемычки. При программировании изготовителем или пользователем часть их расплавляется импульсами тока, которые пропускают через определенные эмиттеры. В результате нарушаются некоторые связи источника Е с разрядными линиями, что обеспечивает появление логических нулей в определенных разрядах считываемого числа.

Элементы ПЗУ (РПЗУ) выполняются на основе МОП-транзисторов определенных структур. Одни из них допускают запись информации при воздействии импульса напряжения и ее стирание при ультрафиолетовом облучении, а другие – запись и стирание под воздействием только напряжений (разной полярности и величины).

Условное изображение микросхемы ПЗУ приведено на рис. 9.8. Она содержит 2048 восьмиразрядных ячеек, выбираемых 11-разрядным адресом А0—А11 (211=2048). Слово, записанное в ячейку, появляется на восьми выходах Q0-Q7 по сигналу на входе СS – выбор микросхемы. Перепрограммируемые ПЗУ имеют в условном обозначении аббревиатуру RРRОМ.

Рис. 9.8. Условное изображение микросхемы ПЗУ

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ

На рис. 9.9 изображено запоминающее устройство (ЗУ) микропроцессорной системы (МПС), состоящее из оперативного ОЗУ и постоянного ПЗУ запоминающих устройств.

ОЗУ собрано на двух группах микросхем (DD0-DD7 и DD8-DD15). Группа (блок, модуль) содержит восемь микросхем, каждая из которых имеет 1000 одноразрядных ячеек (1024х1), поэтому емкость группы составляет 1000 восьмиразрядных слов (1024х8) – 1 Кбайт. Для обращения к такому количеству слов (ячеек) адресная шина содержит 10 линий А0-А9 (210=1024).

ПЗУ собрано на двух микросхемах DD16, DD17 емкостью 1 Кбайт.

Адресные входы всех микросхем ЗУ соответственно запараллелены: соединены все входы А0, все входы А1 и т.д. Аналогично запараллелены выходы Q разрядов групп ОЗУ и выходы Q разрядов микросхем ПЗУ. Таким же образом попарно соединены входы D микросхем ОЗУ.

Выбор каждого ПЗУ и каждого блока ОЗУ осуществляется по входам СS ("Выбор микросхемы" - ВМ) дешифратором с инверсными выходами, на входы которого подаются старшие разряды А10, А11 адреса. Каждая из четырех комбинаций этих разрядов возбуждает один из выходов дешифратора, а с него – соответствующий блок ЗУ. Это позволяет каждый раз обращаться только к одной ячейке ЗУ, несмотря на то, что младшие разряды А0-А9 адреса являются общими для всех микросхем.

Выходы Q микросхем, не выбранных по входам СS, находятся в высокоимпедансном состоянии, т.е. отключены. Именно это дает возможность объединить их общими линиями шины.

Шина данных ШД МП системы через специальный узел – шинный формирователь ВD – соединяется с шиной входов D микросхем ОЗУ или с шиной выходов Q микросхем ЗУ. По этой шине данные поступают в ОЗУ для записи или считываются из ЗУ. Запись осуществляется по сигналу низкого уровня на линии (Зп/Чт), а считывание – по сигналу высокого уровня.

Шинный формирователь (рис. 9.10, а) позволяет организовать двунаправленную шину, по которой можно попеременно передавать информацию то в одном, то в другом направлениях. Если передача осуществляется в направлении от А к В, то выходы элементов И, присоединенные к линиям С, должны быть установлены в высокоимпедансное состояние. При передаче от В к С в высокоимпедансное состояние должны переводиться выходы элементов И, входы которых присоединены к линиям А.

Рис. 9.9. Схема ЗУ МПС

Рис. 9.10. Схема шинного формирователя (а) и его условное обозначение (б)

Такое управление элементами осуществляется по входу DСЕ. Если DСЕ=0, то логическая 1 устанавливается на линии 1 и информация транслируется от А к В. При DСЕ=1 логическая 1 – на линии 2 и информация передается от В к С.

Шинный формирователь инициируется сигналом СS=0. При СS=1 на линиях 1 и 2 — логические нули и выходы всех элементов находятся в высокоомном состоянии – связь между узлами схемы через шинный формирователь прерывается. Условное обозначение шинного формирователя приведено на рис. 9.17, б.