- •1, Этапы развития спо.

- •3. Назначение и функции ос.

- •4. Классификация ос.

- •5. Понятие вычислительного процесса, состояние процесса, типовые операции над процессами.

- •6. Методы реализации многозадачного режима. Многопотоковость.

- •8. Физические и виртуальные ресурсы. Задачи распределения ресурсов.

- •9. Дисциплины распределения ресурсов. Примеры функционирования систем планирования и диспетчеризации.

- •10. Взаимодействие процессов. Синхронизация процессов на уровне примитивов семафора и сигнала. Тупики.

- •11. Сравнение реализации взаимодействующих процессов и многопотокового приложения.

- •12. Средства взаимод-вия процессов в Unix.

- •13.Организация памяти вычислительной системы. Задачи управления оперативной

- •14.Методы статического распределения памяти, динамическое управление памятью.

- •15.Принципы организации виртуальной памяти.

- •16.Страничная и сегментная организация виртуальной памяти. Схемы преобразования адресов.

- •17.Сегментный уровень виртуальной памяти в процессорах Intel x86.

- •18.Сpедства защиты памяти в процессорах Intel x86.

- •19.Механизм шлюзов. Передача управления через Call Gate и Task Gate.

- •20.Прерывания в защищенном режиме работы процессора. Interrupt Gate и Trap Gate.

- •21.Модели сегментации памяти в 32-pазpядных пpоцессоpах. Страничный уровень виртуальной памяти.

- •33.Процесс форматирования. Доступ к диску на физическом уровне.

- •34.Логическая структура диска в ms-dos.

- •35.Файловая система ms-dos. Командные и программные средства управления файлами.

- •36.Сравнительная характеристика файловой системы dos fat и высокопроизводительных файловых систем ntfs, hpfs.

- •37.Система прерываний в реальном режиме процессора. Управление прерываниями в ms-dos.

- •38.Управление программами в ms-dos. Схема создания резидентных программ.

- •39.Системный программный интерфейс bios. Системная область данных bios.

- •40.Системный программный интерфейс dos.

21.Модели сегментации памяти в 32-pазpядных пpоцессоpах. Страничный уровень виртуальной памяти.

Виртуальная память – совокупность программно-аппаратных средств, позволяющих разрабатывать программы в независимом модельном адресном пространстве, не ограниченном ресурсами (размерами) физической памяти.

Модели сегментации памяти в 32-pазpядных процессорах:

На сегментном уровне ВП м.б. реализована 3 моделями:

1.Плоская модель памяти (FLAT)

Суть: все сегменты отображаются в единое физическое адресное пространство, а смещение может относиться как к области кода, так и к области данных.

В таком дескрипторе баз.адрес=0, а макс. размер=4Гб.

Все регистры указывают на один базовый адрес. В такой модели нет ситуаций исключения выхода за границу сегмента (4Гб>макс. реально существующей ОП)

2.Защищенная плоская модель.

Похожа на обычную плоскую модель, но границы сегментов устанавливаются в соответствии с фактически существующей ОП.

Исключение защиты генерируется при попытке доступа к несуществующей памяти. Такая модель используется в системе, где запрещен механизм подкачки страниц.

3.Многосегментная модель.

Каждой программе выделяются собственные сегменты и своя дескрипторная таблица.

Сегменты м.б. с исключительным доступом (чаще всего или могут разделяться несколькими программами (системные библиотеки).

CS-

CS-

SS-

SS-

DS-

DS-

ES-

ES-

FS-

GS-

Страничный уровень виртуальной памяти.

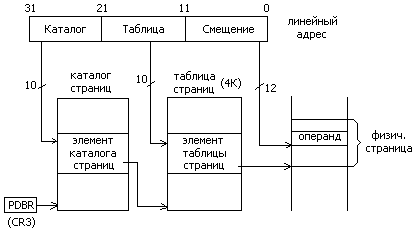

Сегментный уровень ВП формирует линейный адрес (32х разр: адрес в несегментированном однородном адресном пространстве)(32разр.->4Гб).

Если страничная память отключена, линейный адрес является физическим. Если включена (включена подкачка страниц) линейный адрес либо транслируется в физический адрес элемента памяти, либо генерируется исключение по отсутствию страниц.

Страницы имеют фиксированный размер 4кбайта. Если использовать одну таблицу страниц, пришлось бы потратить на нее 4Мб. Поэтому реализованы 2 уровня преобразования:

1.каталог страниц адресует до 1К страничных таблиц 2го уровня. Таблицы страниц сами являются страницами.

PDBR хранит базовый адрес ???????.

При управлении памятью м. реализовать:

а)один каталог для всех задач;

б)по одному каталогу для каждой задачи.

Элемент таблицы страниц:

![]()

P – бит присутствия (Present) страницы в физической памяти.

Р=1-страница в памяти, Р=0-на внешнем носителе (в этом случае элементы таблицы содержат информацию о размещении страницы во внешней памяти.

R/W – разрешение доступа по чтению/записи.

U/S – режимы пользователя/супервизора.

Оба используются для защитных проверок.

PWT – запись страницы прозрачна.

PCD – кэширование на уровне страниц запрещено.

Оба используются для управления страничным КЭШом.

А(Access) – указывает, что доступ к странице произошел (данный элемент – страница занят).

D(Dirty) – указывает, что произошел доступ по записи. Это означает, что при обращении к странице в физической памяти.

AVAIL(Available) – страница доступна для использования ОС-ой (программистом).

Последние использованные элементы таблиц страниц кэшируются во внутреннем ассоциативном буфере процессора (TLB). При управлении этот буфер очищается изменением в CR3.