ЦОС_Заочники2013 / Курсовая МПиЦОС 2011 / Справочная информация / ADC&DAC / cs4226-f2

.pdf

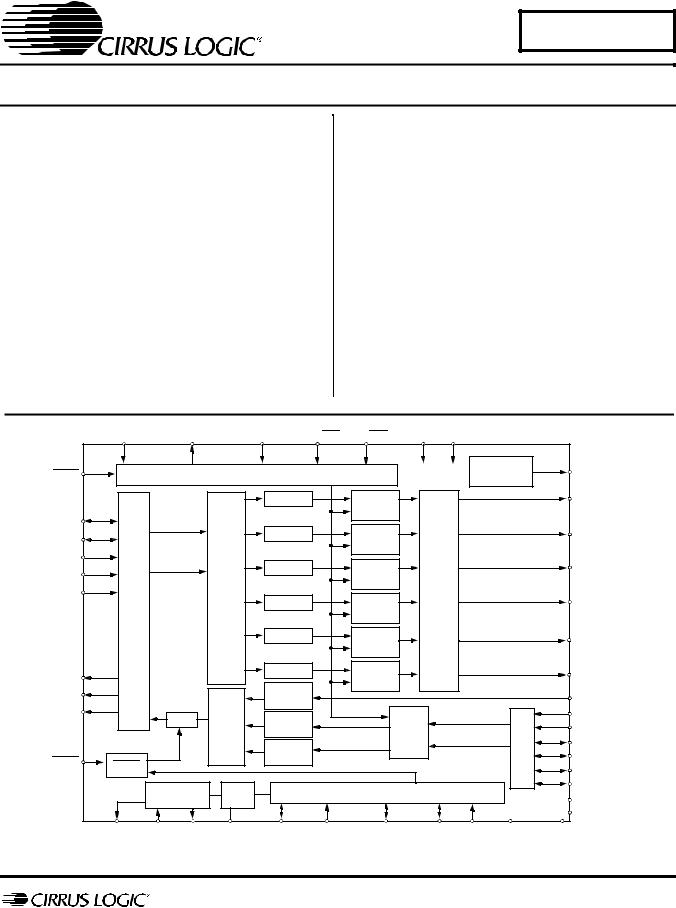

CS4226

Surround Sound Codec

Features

!Stereo 20-bit A/D converters

!Six 20-bit D/A converters

!S/PDIF receiver

– AC-3 & MPEG auto-detect capability

!108 dB DAC signal-to-noise ratio (EIAJ)

!Mono 20-bit A/D converter

!Programmable Input gain & output attenuation

!On-chip anti-aliasing and output smoothing filters

!De-emphasis for 32 kHz, 44.1 kHz, 48 kHz

Description

The CS4226 is a single-chip codec providing stereo an- alog-to-digital and six digital-to-analog converters using Delta-Sigma conversion techniques. This +5V device also contains volume control independently selectable for each of the six D/A channels. An S/PDIF receiver is included as a digital input channel. Applications include Dolby Pro-logic , Dolby Digital AC-3, THX and DTS home theater systems, DSP based car audio systems, and other multi-channel applications.

The CS4226 is packaged in a 44-pin plastic TQFP.

ORDERING INFORMATION |

|

|

CS4226-KQ |

-10° to +70° C |

44-pin TQFP |

CS4226-BQ |

-40° to +85° C |

44-pin TQFP |

CS4226-DQ |

-40° to +85° C |

44-pin TQFP |

CDB4226 |

|

Evaluation Board |

I |

|

|

|

|

|

|

|

|

|

|

SCL/CCLK SDA/CDOUT AD1/CDIN AD0/CS |

I2C/SPI |

VD+ |

VA+ |

|

||||

PDN |

|

|

Control Port |

|

|

|

Voltage |

CMOUT |

|

|

|

|

|

|

Reference |

||||

|

|

|

|

|

DAC#1 |

Volume |

|

|

AOUT1 |

LRCK |

|

|

|

|

|

Control |

|

|

|

|

|

|

|

DAC#2 |

Volume |

|

|

|

|

SCLK |

|

|

|

|

|

|

AOUT2 |

||

|

|

|

|

|

Control |

Analog Low Pass and |

|

|

|

SDIN1 |

|

|

|

|

|

|

|

||

Audio Data Interface |

|

|

Digital Filters |

DAC#3 |

Volume |

Output Stage |

AOUT3 |

||

SDIN2 |

|

|

|||||||

|

|

|

Control |

|

|||||

SDIN3 |

|

|

|

|

|||||

|

|

DAC#4 |

Volume |

AOUT4 |

|||||

|

|

|

|||||||

|

|

|

|

Control |

|

||||

|

|

|

DAC#5 |

Volume |

AOUT5 |

||||

|

|

|

|

Control |

|||||

|

|

|

|

|

|||||

SDOUT1 |

Serial |

|

|

|

DAC#6 |

Volume |

|

|

AOUT6 |

SDOUT2 |

|

|

|

|

Mono |

Control |

|

|

|

|

|

|

Digital Filters |

|

|

|

AINAUX |

||

|

|

|

ADC |

|

|

|

|||

OVL/ERR |

|

|

|

|

|

|

|||

|

MUX |

Left |

|

Input Gain |

|

AIN1L |

|||

|

|

|

Input MUX |

AIN1R |

|||||

|

|

|

|

ADC |

|

||||

|

|

|

|

Right |

|

AIN2L/FREQ0 |

|||

DEM |

DEM |

|

|

ADC |

|

AIN2R/FREQ1 |

|||

|

|

|

|

AIN3L/AUTODATA |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

Clock Osc/ |

PLL |

S/PDIF RX/Auxiliary Input |

AIN3R/AUDIO |

||||

|

|

AGND1 |

|||||||

|

|

Divider |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

AGND2 |

|

CLKOUT |

XTI |

XTO |

FILT HOLD/RUBIT |

LRCKAUX/RX3 |

RX1 DGND1 DGND2 |

|||

|

|

|

|

|

DATAUX/RX4 |

SCLKAUX/RX2 |

|

||

|

|

Copyright Cirrus Logic, Inc. 2003 |

MAR ‘03 |

|

www.cirrus.com |

||||

(All Rights Reserved) |

DS188F2 |

|||

|

|

|

||

|

|

|

1 |

|

|

CS4226 |

TABLE OF CONTENTS |

|

1 CHARACTERISTICS/SPECIFICATIONS .................................................................................. |

4 |

SPECIFIED OPERATING CONDITIONS ................................................................................. |

4 |

ABSOLUTE MAXIMUM RATINGS ........................................................................................... |

4 |

ANALOG CHARACTERISTICS ................................................................................................ |

5 |

SWITCHING CHARACTERISTICS .......................................................................................... |

7 |

SWITCHING CHARACTERISTICS - CONTROL PORT........................................................... |

8 |

S/PDIF RECEIVER CHARACTERISTICS ................................................................................ |

9 |

DIGITAL CHARACTERISTICS ................................................................................................. |

9 |

2 FUNCTIONAL DESCRIPTION ................................................................................................ |

11 |

2.1 Overview .......................................................................................................................... |

11 |

2.2 Analog Inputs ................................................................................................................... |

11 |

2.2.1 Line Level Inputs ................................................................................................. |

11 |

2.2.2 Adjustable Input Gain .......................................................................................... |

12 |

2.2.3 High Pass Filter ................................................................................................... |

12 |

2.3 Analog Outputs ................................................................................................................ |

12 |

2.3.1 Line Level Outputs .............................................................................................. |

12 |

2.3.2 Output Level Attenuator ...................................................................................... |

12 |

2.4 Clock Generation ............................................................................................................. |

13 |

2.4.1 Clock Source ....................................................................................................... |

13 |

2.4.2 Master Clock Output ........................................................................................... |

14 |

2.4.3 Synchronization ................................................................................................... |

14 |

2.5 Digital Interfaces .............................................................................................................. |

14 |

2.5.1 Audio DSP Serial Interface Signals ..................................................................... |

14 |

2.5.2 Audio DSP Serial Interface Formats ................................................................... |

15 |

2.5.3 Auxiliary Audio Port Signals ................................................................................ |

17 |

Contacting Cirrus Logic Support |

|

For all product questions and inquiries contact a Cirrus Logic Sales Representative. |

|

To find one nearest you go to www.cirrus.com |

|

IMPORTANT NOTICE

Cirrus Logic, Inc. and its subsidiaries ("Cirrus") believe that the information contained in this document is accurate and reliable. However, the information is subject to change without notice and is provided "AS IS" without warranty of any kind (express or implied). Customers are advised to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability. No responsibility is assumed by Cirrus for the use of this information, including use of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights of third parties. This document is the property of Cirrus and by furnishing this information, Cirrus grants no license, express or implied under any patents, mask work rights, copyrights, trademarks, trade secrets or other intellectual property rights. Cirrus owns the copyrights associated with the information contained herein and gives consent for copies to be made of the information only for use within your organization with respect to Cirrus integrated circuits or other parts of Cirrus. This consent does not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating any work for resale.

An export permit needs to be obtained from the competent authorities of the Japanese Government if any of the products or technologies described in this material and controlled under the "Foreign Exchange and Foreign Trade Law" is to be exported or taken out of Japan. An export license and/or quota needs to be obtained from the competent authorities of the Chinese Government if any of the products or technologies described in this material is subject to the PRC Foreign Trade Law and is to be exported or taken out of the PRC.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). CIRRUS PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED FOR USE IN AIRCRAFT SYSTEMS, MILITARY APPLICATIONS, PRODUCTS SURGICALLY IMPLANTED INTO THE BODY, LIFE SUPPORT PRODUCTS OR OTHER CRITICAL APPLICATIONS (INCLUDING MEDICAL DEVICES, AIRCRAFT SYSTEMS OR COMPONENTS AND PERSONAL OR AUTOMOTIVE SAFETY OR SECURITY DEVICES). INCLUSION OF CIRRUS PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK AND CIRRUS DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS PRODUCT THAT IS USED IN SUCH A MANNER. IF THE CUSTOMER OR CUSTOMER'S CUSTOMER USES OR PERMITS THE USE OF CIRRUS PRODUCTS IN CRITICAL APPLICATIONS, CUSTOMER AGREES, BY SUCH USE, TO FULLY INDEMNIFY CIRRUS, ITS OFFICERS, DIRECTORS, EMPLOYEES, DISTRIBUTORS AND OTHER AGENTS FROM ANY AND ALL LIABILITY, INCLUDING ATTORNEYS' FEES AND COSTS, THAT MAY RESULT FROM OR ARISE IN CONNECTION WITH THESE USES.

Cirrus Logic, Cirrus, and the Cirrus Logic logo designs are trademarks of Cirrus Logic, Inc. All other brand and product names in this document may be trademarks or service marks of their respective owners.

I2C is a registered trademark of Philips Semiconductor. Purchase of I2C Components of Cirrus Logic, Inc., or one of its sublicensed Associated Companies conveys a license under the Philips I2C Patent Rights to use those components in a standard I2C system.

DTS is a registered trademark of the Digital Theater Systems, Inc.

Dolby, Dolby Digital, AC-3, AAC, and Pro Logic are registered trademarks of Dolby Laboratories, Inc.

THX is a registered trademark of Lucasfilms Ltd.

2 |

DS188F2 |

CS4226

2.5.4 Auxiliary Audio Port Formats .............................................................................. |

17 |

2.5.5 S/PDIF Receiver ................................................................................................. |

17 |

2.5.6 AC-3/MPEG Auto Detection ................................................................................ |

18 |

2.6 Control Port Signals ......................................................................................................... |

18 |

2.6.1 SPI Mode ............................................................................................................ |

18 |

2.6.2 I2C Mode ............................................................................................................. |

19 |

2.6.3 Control Port Bit Definitions .................................................................................. |

19 |

2.7 Power-up/Reset/Power Down Mode ............................................................................... |

20 |

2.8 DAC Calibration ............................................................................................................... |

20 |

2.9 De-Emphasis ................................................................................................................... |

20 |

2.10 HOLD Function .............................................................................................................. |

21 |

2.11 Power Supply, Layout, and Grounding .......................................................................... |

21 |

2.12 ADC and DAC Filter Response Plots ............................................................................ |

22 |

3 REGISTER DESCRIPTION ..................................................................................................... |

24 |

4 PIN DESCRIPTION .................................................................................................................. |

32 |

5 PARAMETER DEFINITIONS ................................................................................................... |

36 |

6 PACKAGE DIMENSIONS ....................................................................................................... |

37 |

LIST OF FIGURES |

|

Figure 1. Recommended Connection Diagram............................................................................. |

10 |

Figure 2. Optional Line Input Buffer .............................................................................................. |

11 |

Figure 3. Butterworth Filter Examples........................................................................................... |

13 |

Figure 4. Audio DSP and Auxiliary Port Data Input Formats ........................................................ |

15 |

Figure 5. Audio DSP Port Data Output Formats ........................................................................... |

15 |

Figure 6. One data line modes...................................................................................................... |

16 |

Figure 7. Control Port Timing, SPI mode ...................................................................................... |

18 |

Figure 8. Control Port Timing, I2C Mode....................................................................................... |

19 |

Figure 9. De-emphasis Curve ....................................................................................................... |

20 |

Figure 10. 20-bit ADC Filter Response ......................................................................................... |

22 |

Figure 11. 20-bit ADC Passband Ripple ....................................................................................... |

22 |

Figure 12. 20-bit ADC Transition Band ......................................................................................... |

22 |

Figure 13. DAC Frequency Response .......................................................................................... |

22 |

Figure 14. DAC Passband Ripple ................................................................................................. |

22 |

Figure 15. DAC Transition Band ................................................................................................... |

22 |

LIST OF TABLES |

|

Table 1. Single-ended vs Differential Input Pin Assignments ....................................................... |

11 |

Table 2. High Pass Filter Characteristics ..................................................................................... |

12 |

Table 3. DSP Serial Interface Ports ............................................................................................. |

15 |

Table 4. S/PDIF Receiver Status Outputs .................................................................................... |

17 |

DS188F2 |

3 |

CS4226

1 CHARACTERISTICS/SPECIFICATIONS

(All Min/Max characteristics and specifications are guaranteed over the Specified Operating Conditions. Typical performance characteristics and specifications are derived from measurements taken at nominal supply voltages and TA = 25°C.)

SPECIFIED OPERATING CONDITIONS

(AGND, DGND = 0V, all voltages with respect to 0V.)

Parameter |

|

Symbol |

Min |

Nom |

|

Max |

Units |

|||

|

|

|

|

|

|

|

|

|

|

|

Power Supplies |

Digital |

VD+ |

4.75 |

|

5.0 |

|

|

5.25 |

V |

|

|(VA+)-(VD+)|<0.4V |

Analog |

VA+ |

4.75 |

|

5.0 |

|

|

5.25 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

Operating Ambient Temperature |

CS4226-KQ |

TA |

-10 |

|

- |

|

|

70 |

°C |

|

|

CS4226-BQ |

|

|

-40 |

|

- |

|

|

85 |

°C |

|

CS4226-DQ |

|

|

-40 |

|

- |

|

|

85 |

°C |

|

|

|

|

|

|

|

|

|

||

ABSOLUTE MAXIMUM RATINGS (AGND, DGND = 0V, all voltages with respect to 0V.) |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

Parameter |

|

Symbol |

|

Min |

|

Typ |

|

|

Max |

Units |

|

|

|

|

|

|

|

|

|

|

|

Power Supplies |

Digital |

VD+ |

|

-0.3 |

|

- |

|

6.0 |

V |

|

|

Analog |

VA+ |

|

-0.3 |

|

- |

|

6.0 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

Input Current |

(Note 1) |

|

|

- |

|

- |

|

±10 |

mA |

|

|

|

|

|

|

|

|

|

|

|

|

Analog Input Voltage |

(Note 2) |

|

|

-0.7 |

|

- |

|

(VA+)+0.7 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

Digital Input Voltage |

(Note 2) |

|

|

-0.7 |

|

- |

|

(VD+)+0.7 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

Ambient Temperature |

(Power Applied) |

|

|

-55 |

|

- |

|

+125 |

°C |

|

|

|

|

|

|

|

|

|

|

|

|

Storage Temperature |

|

|

|

-65 |

|

- |

|

+150 |

°C |

|

|

|

|

|

|

|

|

|

|

|

|

WARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

Notes: 1. Any pin except supplies. Transient currents of up to ±100 mA on the analog input pins will not cause SCR latch-up.

2. The maximum over or under voltage is limited by the input current.

4 |

DS188F2 |

CS4226

ANALOG CHARACTERISTICS (Full Scale Input Sine wave, 990.52 Hz; Fs = 44.1 kHz (PLL in use); Measurement Bandwidth is 20 Hz to 20 kHz, unless specified otherwise.)

|

|

|

|

CS4226-KQ |

CS4226-BQ/-DQ |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

Parameter |

|

Symbol |

Min |

Typ |

Max |

Min |

Typ |

Max |

Units |

|

|

|

|

|

|

|

|

|

||

Analog Input Characteristics - Minimum gain |

setting (0 |

dB) Differential Input; unless otherwise specified. |

||||||||

|

|

|

|

|

|

|

|

|

|

|

ADC Resolution |

Stereo Audio channels |

|

16 |

- |

20 |

16 |

- |

20 |

Bits |

|

|

Mono channel |

|

16 |

- |

20 |

16 |

- |

20 |

Bits |

|

|

|

|

|

|

|

|

|

|

|

|

Total Harmonic Distortion |

|

THD |

|

0.003 |

- |

|

0.003 |

- |

% |

|

|

|

|

|

|

|

|

|

|

|

|

Dynamic Range |

(A weighted, Stereo) |

|

92 |

95 |

- |

90 |

93 |

- |

dB |

|

|

(unweighted, Stereo) |

|

- |

92 |

- |

- |

90 |

- |

dB |

|

|

(A weighted, Mono) |

|

89 |

- |

- |

87 |

- |

- |

dB |

|

|

|

|

|

|

|

|

|

|

|

|

Total Harmonic |

-1 dB, Stereo |

(Note 3) |

THD+N |

- |

-88 |

-82 |

- |

-86 |

-80 |

dB |

Distortion + Noise |

-1 dB, Mono |

(Note 1) |

|

- |

- |

-72 |

- |

- |

-70 |

dB |

|

|

|

|

|

|

|

|

|

|

|

Interchannel Isolation |

|

|

- |

90 |

- |

- |

90 |

- |

dB |

|

|

|

|

|

|

|

|

|

|

|

|

Interchannel Gain Mismatch |

|

|

- |

0.1 |

- |

- |

0.1 |

- |

dB |

|

|

|

|

|

|

|

|

|

|

|

|

Programmable Input Gain Span |

|

|

8 |

9 |

10 |

8 |

9 |

10 |

dB |

|

|

|

|

|

|

|

|

|

|

|

|

Gain Step Size |

|

|

|

2.7 |

3 |

3.3 |

2.7 |

3 |

3.3 |

dB |

|

|

|

|

|

|

|

|

|

|

|

Offset Error (with high pass filter) |

|

|

- |

- |

0 |

- |

- |

0 |

LSB |

|

|

|

|

|

|

|

|

|

|

||

Full Scale Input Voltage (Single Ended): |

|

0.90 |

1.0 |

1.10 |

0.90 |

1.0 |

1.10 |

Vrms |

||

|

|

|

|

|

|

|

|

|

|

|

Gain Drift |

|

|

|

- |

100 |

- |

- |

100 |

- |

ppm/°C |

|

|

|

|

|

|

|

|

|

|

|

Input Resistance |

|

(Note 4) |

|

10 |

- |

- |

10 |

- |

- |

kΩ |

|

|

|

|

|

|

|

|

|

|

|

Input Capacitance |

|

|

|

- |

- |

15 |

- |

- |

15 |

pF |

|

|

|

|

|

|

|

|

|

|

|

CMOUT Output Voltage |

|

|

- |

2.3 |

- |

- |

2.3 |

- |

V |

|

|

|

|

|

|

|

|

|

|

||

A/D Decimation Filter Characteristics |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

Passband |

|

(Note 5) |

|

0.02 |

- |

20.0 |

0.02 |

- |

20.0 |

kHz |

|

|

|

|

|

|

|

|

|

|

|

Passband Ripple |

|

|

|

- |

- |

0.01 |

- |

- |

0.01 |

dB |

|

|

|

|

|

|

|

|

|

|

|

Stopband |

|

(Note 5) |

|

27.56 |

- |

5617.2 |

27.56 |

- |

5617.2 |

kHz |

|

|

|

|

|

|

|

|

|

|

|

Stopband Attenuation |

(Note 6) |

|

80 |

- |

- |

80 |

- |

- |

dB |

|

|

|

|

|

|

|

|

|

|

|

|

Group Delay (Fs = Output Sample Rate) |

(Note 7) |

tgd |

- |

15/Fs |

- |

- |

15/Fs |

- |

s |

|

Group Delay Variation vs. Frequency |

|

∆ tgd |

- |

- |

0 |

- |

- |

0 |

µs |

|

Notes: 3. Referenced to typical full-scale differential input voltage (2Vrms).

4.Input resistance is for the input selected. Non-selected inputs have a very high (>1MΩ) input resistance. The input resistance will vary with gain value selected, but will always be greater than the min. value specified

5.Filter characteristics scale with output sample rate.

6.The analog modulator samples the input at 5.6448 MHz for an output sample rate of 44.1 kHz. There is no rejection of input signals which are multiples of the sampling frequency (n × 5.6448 MHz ±20.0 kHz where n = 0,1,2,3...).

7.Group delay for Fs = 44.1 kHz, tgd = 15/44.1 kHz = 340 µs

DS188F2 |

5 |

CS4226

ANALOG CHARACTERISTICS (Continued)

|

|

|

|

|

CS4226-KQ |

CS4226-BQ |

|

||||

Parameter |

|

Symbol |

|

|

|

|

|

|

Units |

||

|

Min |

Typ |

Max |

Min |

Typ |

Max |

|||||

|

|

|

|

|

|

|

|

|

|

||

High Pass Filter Characteristics |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

Frequency Response: |

-3 dB |

(Note 5) |

|

- |

3.4 |

- |

- |

3.4 |

- |

Hz |

|

|

|

-0.13 dB |

|

|

- |

20 |

- |

- |

20 |

- |

Hz |

|

|

|

|

|

|

|

|

|

|

|

|

Phase Deviation |

|

@ 20 Hz |

(Note 5) |

|

- |

10 |

- |

- |

10 |

- |

Deg. |

|

|

|

|

|

|

|

|

|

|

|

|

Passband Ripple |

|

|

|

|

- |

- |

0 |

- |

- |

0 |

dB |

|

|

|

|

|

|

|

|

|

|||

Analog Output Characteristics - Minimum Attenuation, 10 kΩ, 100 pF load; unless otherwise specified. |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

DAC Resolution |

|

|

|

|

16 |

- |

20 |

16 |

- |

20 |

Bits |

|

|

|

|

|

|

|

|

|

|

|

|

Signal-to-Noise/Idle |

|

(DAC muted, A weighted) |

|

101 |

108 |

- |

99 |

106 |

- |

dB |

|

Channel Noise |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Dynamic Range |

(DAC not muted, A weighted) |

|

93 |

98 |

- |

91 |

96 |

- |

dB |

||

(DAC not muted, unweighted) |

|

- |

95 |

- |

- |

93 |

- |

dB |

|||

|

|

|

|

|

|

|

|

|

|

|

|

Total Harmonic Distortion |

|

|

THD |

- |

0.003 |

- |

- |

0.003 |

- |

% |

|

|

|

|

|

|

|

|

|

|

|

||

Total Harmonic Distortion + Noise |

(Stereo) |

THD+N |

- |

-88 |

-83 |

- |

-86 |

-81 |

dB |

||

|

|

|

|

|

|

|

|

|

|

|

|

Interchannel Isolation |

|

|

|

|

- |

90 |

- |

- |

90 |

- |

dB |

|

|

|

|

|

|

|

|

|

|

||

Interchannel Gain Mismatch |

|

|

- |

0.1 |

- |

- |

0.1 |

- |

dB |

||

|

|

|

|

|

|

|

|

|

|

|

|

Attenuation Step Size |

|

(All Outputs) |

|

0.7 |

1 |

1.3 |

0.7 |

1 |

1.3 |

dB |

|

|

|

|

|

|

|

|

|

|

|||

Programmable Output Attenuation Span |

|

-84 |

-86 |

- |

-84 |

-86 |

- |

dB |

|||

|

|

|

|

|

|

|

|

|

|

|

|

Offset Voltage |

|

(relative to CMOUT) |

|

- |

±15 |

- |

- |

±15 |

- |

mV |

|

|

|

|

|

|

|

|

|

|

|

|

|

Full Scale Output Voltage |

|

|

|

0.92 |

1.0 |

1.08 |

0.92 |

1.0 |

1.08 |

Vrms |

|

|

|

|

|

|

|

|

|

|

|

|

|

Gain Drift |

|

|

|

|

- |

100 |

- |

- |

100 |

- |

ppm/°C |

|

|

|

|

|

|

|

|

|

|

|

|

Out-of-Band Energy |

|

(Fs/2 to 2Fs) |

|

- |

-60 |

- |

- |

-60 |

- |

dBFs |

|

|

|

|

|

|

|

|

|

|

|

|

|

Analog Output Load |

|

|

Resistance: |

|

10 |

- |

- |

10 |

- |

- |

kΩ |

|

|

|

Capacitance: |

|

- |

- |

100 |

- |

- |

100 |

pF |

|

|

|

|

|

|

|

|

|

|||

Combined Digital and Analog Filter Characteristics |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

Frequency Response |

|

10 Hz to 20 kHz |

|

- |

±0.1 |

- |

- |

±0.1 |

- |

dB |

|

|

|

|

|

|

|

|

|

|

|

||

Deviation from Linear Phase |

|

|

- |

±0.5 |

- |

- |

±0.5 |

- |

Deg. |

||

|

|

|

|

|

|

|

|

|

|

||

Passband: to 0.01 dB corner |

(Notes 8, 9) |

|

0 |

- |

20.0 |

0 |

- |

20.0 |

kHz |

||

|

|

|

|

|

|

|

|

|

|

|

|

Passband Ripple |

|

|

(Note 9) |

|

- |

- |

±0.01 |

- |

- |

±0.01 |

dB |

|

|

|

|

|

|

|

|

|

|

|

|

Stopband |

|

|

(Notes 8, 9) |

|

24.1 |

- |

- |

24.1 |

- |

- |

kHz |

|

|

|

|

|

|

|

|

|

|

|

|

Stopband Attenuation |

|

|

(Note 10) |

|

70 |

- |

- |

70 |

- |

- |

dB |

|

|

|

|

|

|

|

|

|

|

||

Group Delay (Fs = Input Word Rate) |

(Note 5) |

tgd |

- |

16/Fs |

- |

- |

16/Fs |

- |

s |

||

|

|

|

|

|

|

|

|

|

|

||

Analog Loopback Performance |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

||||

Signal-to-noise Ratio (CCIR-2K weighted, -20 dB input) |

CCIR-2K |

- |

71 |

- |

- |

71 |

- |

dB |

|||

|

|

|

|

|

|

|

|

|

|

|

|

Power Supply |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Power Supply Current |

|

Operating |

|

- |

90 |

113 |

- |

90 |

115 |

mA |

|

|

|

|

Power Down |

|

- |

1 |

3 |

- |

1 |

3 |

mA |

|

|

|

|

|

|

|

|

|

|

||

Power Supply Rejection |

(1 kHz, 10 mVrms) |

|

- |

45 |

- |

- |

45 |

- |

dB |

||

Notes: 8. The passband and stopband edges scale with frequency. For input word rates, Fs, other than 44.1 kHz, the 0.01 dB passband edge is 0.4535×Fs and the stopband edge is 0.5465×Fs.

9.Digital filter characteristics.

10.Measurement bandwidth is 10 Hz to 3 Fs.

6 |

DS188F2 |

CS4226

SWITCHING CHARACTERISTICS (Outputs loaded with 30 pF)

|

|

|

|

Parameter |

|

|

Symbol |

|

|

Min |

|

Typ |

|

|

Max |

|

Units |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

Audio ADC's & DAC's Sample Rate |

|

|

Fs |

|

|

4 |

|

|

|

- |

|

50 |

|

|

kHz |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

XTI Frequency |

|

(XTI = 256, 384, or 512 Fs) |

|

|

|

1.024 |

|

|

|

- |

|

26 |

|

|

MHz |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

XTI Pulse Width High |

XTI = 512 Fs |

|

|

|

|

|

|

10 |

|

|

|

- |

|

- |

|

|

|

ns |

|||||||||||||

|

|

|

|

|

|

XTI = 384 Fs |

|

|

|

|

|

|

21 |

|

|

|

- |

|

- |

|

|

|

ns |

|||||||||

|

|

|

|

|

|

XTI = 256 Fs |

|

|

|

|

|

|

31 |

|

|

|

- |

|

- |

|

|

|

ns |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

XTI Pulse Width Low |

XTI = 512 Fs |

|

|

|

|

|

|

10 |

|

|

|

- |

|

- |

|

|

|

ns |

|||||||||||||

|

|

|

|

|

|

XTI = 384 Fs |

|

|

|

|

|

|

21 |

|

|

|

- |

|

- |

|

|

|

ns |

|||||||||

|

|

|

|

|

|

XTI = 256 Fs |

|

|

|

|

|

|

31 |

|

|

|

- |

|

- |

|

|

|

ns |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

PLL Clock Recovery Frequency RX, XTI, LRCK, LRCKAUX |

|

|

|

|

30 |

|

|

|

- |

|

50 |

|

|

kHz |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

XTI Jitter Tolerance |

|

|

|

|

|

|

|

|

|

|

|

|

- |

|

|

|

500 |

|

- |

|

|

|

ps |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PDN |

Low Time |

|

|

|

|

|

|

|

(Note 11) |

|

|

|

|

500 |

|

|

|

- |

|

- |

|

|

|

ns |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SCLK Falling Edge to SDOUT Output Valid |

|

(DSCK = 0) |

tdpd |

|

|

- |

|

|

|

- |

|

1 |

|

|

|

|

ns |

||||||||||||||

|

|

|

|

|

|

|

|

------------------- + 20 |

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(384)Fs |

|

|

||||

|

LRCK edge to MSB valid |

|

|

|

|

|

|

|

|

tlrpd |

|

|

- |

|

|

|

- |

|

40 |

|

|

ns |

||||||||||

|

SDIN Setup Time Before SCLK Rising Edge |

|

(DSCK=0) |

tds |

|

|

- |

|

|

|

- |

|

25 |

|

|

ns |

||||||||||||||||

|

SDIN Hold Time After SCLK Rising Edge |

|

(DSCK=0) |

tdh |

|

|

- |

|

|

|

- |

|

25 |

|

|

ns |

||||||||||||||||

|

Master Mode |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SCLK Period |

|

|

|

|

|

|

|

|

tsck |

|

|

1 |

|

|

|

- |

|

- |

|

|

|

ns |

|||||||||

|

|

|

|

|

|

|

|

|

|

------------------- |

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(256)Fs |

|

|

|

|

|

|

|

|

|

|

|

||||

|

SCLK Falling to LRCK Edge |

|

(DSCK=0) |

tmslr |

|

|

- |

|

|

|

±10 |

|

- |

|

|

|

ns |

|||||||||||||||

|

SCLK Duty Cycle |

|

|

|

|

|

|

|

|

|

|

|

|

- |

|

|

|

50 |

|

- |

|

|

|

% |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Slave Mode |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SCLK Period |

|

|

|

|

|

|

|

|

tsckw |

|

|

1 |

|

|

|

- |

|

- |

|

|

|

ns |

|||||||||

|

|

|

|

|

|

|

|

|

|

------------------- |

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(128)Fs |

|

|

|

|

|

|

|

|

|

|

|

||||

|

SCLK High Time |

|

|

|

|

|

|

|

|

tsckh |

|

|

40 |

|

|

|

- |

|

- |

|

|

|

ns |

|||||||||

|

SCLK Low Time |

|

|

|

|

|

|

|

|

tsckl |

|

|

40 |

|

|

|

- |

|

- |

|

|

|

ns |

|||||||||

|

SCLK Rising to LRCK Edge |

|

|

|

|

|

|

|

(DSCK=0) |

tlrckd |

|

|

20 |

|

|

|

- |

|

- |

|

|

|

ns |

|||||||||

|

LRCK Edge to SCLK Rising |

|

|

|

|

|

|

|

(DSCK=0) |

tlrcks |

|

|

40 |

|

|

|

- |

|

- |

|

|

|

ns |

|||||||||

Notes: 11. After powering up the CS4226, |

|

|

should be held low until the power supply is settled. |

|

||||||||||||||||||||||||||||

PDN |

|

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LRCK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LR C K A UX |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

t sck |

(input) |

t lrckd |

|

t lrcks |

|

t sckh |

|

tsckl |

|

|||||||||||

|

|

SCLK* |

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

SCLKAUX* |

|

|

|

|

|

|

|

S C LK * |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

(output) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

S C L KA U X * |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

t mslr |

|

(input) |

|

|

|

|

|

|

|

|

|

|

|

t sckw |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

LRCK |

|

|

|

|

SDIN1 |

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

LRCKAUX |

|

|

|

|

|

|

|

|

SDIN2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

(output) |

|

|

|

|

|

|

|

|

SDIN3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D AT AU X |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t lrpd |

t ds |

|

t dh |

|

|

|

t dp d |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

SDOUT1 |

|

|

|

|

|

|

|

|

S D O U T 1 |

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

M S B |

|

|

|

MSB-1 |

|

|||||||||

|

|

SDOUT2 |

|

|

|

|

|

|

|

|

S D O U T 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

*S C LK , SC LK AU X sh ow n for D SC K = 0 and ASC K = 0. |

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

S C LK & S CL KA U X inverted for D SC K = 1 a nd A SC K = 1 , respectively. |

|||||||||||||||||||

|

|

Audio Ports Master Mode Timing |

|

|

Audio Ports Slave Mode and Data I/O timing |

|||||||||||||||||||||||||||

DS188F2 |

7 |

CS4226

SWITCHING CHARACTERISTICS - CONTROL PORT (Inputs: logic 0 = DGND, logic 1 =

VD+, CL = 30 pF)

|

|

Parameter |

|

Symbol |

Min |

Max |

Units |

|

|

|

|

|

|

|

|

|

SPI Mode (SPI/I2C = 0) |

|

|

|

|

|

|

|

CCLK Clock Frequency |

|

fsck |

- |

6 |

MHz |

|

|

CS |

High Time Between Transmissions |

|

tcsh |

1.0 |

|

s |

|

CS |

Falling to CCLK Edge |

|

tcss |

20 |

|

ns |

CCLK Low Time |

|

tscl |

66 |

|

ns |

||

CCLK High Time |

|

tsch |

66 |

|

ns |

||

CDIN to CCLK Rising Setup Time |

|

tdsu |

40 |

|

ns |

||

CCLK Rising to DATA Hold Time |

(Note 12) |

tdh |

15 |

|

ns |

||

CCLK Falling to CDOUT stable |

|

tpd |

|

45 |

ns |

||

Rise Time of CDOUT |

|

tr1 |

|

25 |

ns |

||

Fall Time of CDOUT |

|

tf1 |

|

25 |

ns |

||

Rise Time of CCLK and CDIN |

(Note 13) |

tr2 |

|

100 |

ns |

||

Fall Time of CCLK and CDIN |

(Note 13) |

tf2 |

|

100 |

ns |

||

Notes: 12. Data must be held for sufficient time to bridge the transition time of CCLK.

13. For FSCK < 1 MHz

C S |

|

|

t css |

t scl |

t s ch |

C C L K |

|

|

t r2 |

t f2 |

|

C D IN |

|

|

|

t d s u |

t dh |

t csh

t pd

C D O U T

8 |

DS188F2 |

CS4226

SWITCHING CHARACTERISTICS - CONTROL PORT (Inputs: logic 0 = DGND, logic 1 =

VD+, CL = 30 pF)

Parameter |

|

Symbol |

Min |

Max |

Units |

|

|

|

|

|

|

I2C® Mode (SPI/I2C = 1) |

|

|

|

|

|

SCL Clock Frequency |

|

fscl |

- |

100 |

kHz |

Bus Free Time Between Transmissions |

|

tbuf |

4.7 |

|

µs |

Start Condition Hold Time (prior to first clock pulse) |

|

thdst |

4.0 |

|

µs |

Clock Low Time |

|

tlow |

4.7 |

|

µs |

Clock High Time |

|

thigh |

4.0 |

|

µs |

Setup Time for Repeated Start Condition |

|

tsust |

4.7 |

|

µs |

SDA Hold Time from SCL Falling |

(Note 14) |

thdd |

0 |

|

µs |

SDA Setup Time to SCL Rising |

|

tsud |

250 |

|

ns |

Rise Time of Both SDA and SCL Lines |

|

tr |

|

1 |

µs |

Fall Time of Both SDA and SCL Lines |

|

tf |

|

300 |

ns |

Setup Time for Stop Condition |

|

tsusp |

4.7 |

|

µs |

Notes: 14. Data must be held for sufficient time to bridge the 300 ns transition time of SCL

S/PDIF RECEIVER CHARACTERISTICS (RX1, RX2, RX3, RX4 pins only)

Parameter |

|

Symbol |

Min |

Typ |

Max |

Units |

|

|

|

|

|

|

|

Input Resistance |

|

ZN |

- |

10 |

- |

kΩ |

Input Voltage |

|

VTH |

200 |

- |

- |

mVpp |

Input Hysteresis |

|

VHYST |

- |

50 |

- |

mV |

Input Sample Frequency |

|

FS |

30 |

- |

50 |

kHz |

CLKOUT Jitter |

(Note 15) |

|

- |

200 |

- |

ps RMS |

|

|

|

|

|

|

|

CLKOUT Duty Cycle (high time/cycle time) |

(Note 16) |

|

40 |

50 |

60 |

% |

|

|

|

|

|

|

|

Notes: 15. CLKOUT Jitter is for 256×FS selected as output frequency measured from falling edge to falling edge. Jitter is greater for 384×Fs and 512×Fs as selected output frequency.

16. For CLKOUT frequency equal to 1×Fs, 384×Fs, and 512×Fs. See Master Clock Output section.

DIGITAL CHARACTERISTICS

|

Parameter |

Symbol |

Min |

Typ |

Max |

Units |

|

|

|

|

|

|

|

High-level Input Voltage |

(except RX1) |

VIH |

2.8 |

- |

(VD+)+0.3 |

V |

Low-level Input Voltage |

(except RX1) |

VIL |

-0.3 |

- |

0.8 |

V |

High-level Output Voltage at I0 = -2.0 mA |

VOH |

(VD+)-1.0 |

- |

- |

V |

|

Low-level Output Voltage at I0 = 2.0 mA |

VOL |

- |

- |

0.4 |

V |

|

Input Leakage Current |

(Digital Inputs) |

|

- |

- |

10 |

µA |

|

|

|

|

|

|

|

Output Leakage Current |

(High-Impedance Digital Outputs) |

|

- |

- |

10 |

µA |

|

|

|

|

|

|

|

DS188F2 |

9 |

|

|

|

|

|

|

|

|

|

|

|

|

CS4226 |

|

F e rrite Bea d |

|

|

|

2.0 Ω |

|

|

|

|

|

|

|

+ 5 V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S u p p ly |

|

|

+ 1 µ F |

0 .1 µF |

+ 1 µF |

0 .1 µF |

|

|

|

|

||

|

|

|

|

|

|

19 |

|

40 |

|

|

|

|

|

|

|

|

|

V A + |

|

V D + |

|

|

|

|

|

To O ptional |

|

|

16 |

C M O U T |

|

|

|

2 1 |

A N A L O G |

|

||

1 µ F |

+ |

|

|

|

|

A O U T 1 |

F ILT E R |

|

|

|||

Input and |

|

|

|

|

|

|

|

|

||||

O utput B uffers |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 2 |

A N A L O G |

|

|

|

|

1 0 µF |

* |

14 |

|

|

|

|

A O U T 2 |

F ILT E R |

|

|

|

|

A IN 1 L |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

r |

|

1 0 µF |

* |

13 |

A IN 1 R |

CS 4226 |

|

|

|

|

||

|

|

|

|

|

|

|

|

|||||

u ffe |

|

|

|

|

|

2 3 |

A N A L O G |

|

||||

|

|

|

|

|

|

|

|

|

||||

B |

|

1 0 µF |

* |

11 |

|

|

|

|

A O U T 3 |

F ILT E R |

|

|

u t |

|

A IN 2L/F R E Q 0 |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|||

l In p |

|

1 0 µF |

* |

12 |

|

|

|

|

|

|

|

|

na |

|

A IN 2R /F R E Q 1 |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|||

ptio |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

2 4 |

A N A L O G |

|

||

O |

|

1 0 µF |

* |

10 |

A IN 3 L/AU T O D A TA |

|

|

A O U T 4 |

F ILT E R |

|

|

|

m |

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|||

F ro |

|

10 µ F |

* |

9 |

|

|

|

|

|

|

|

|

|

|

A IN 3 R /A U D IO |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

2 5 |

A N A L O G |

|

|

|

|

1 0 µF |

* |

15 |

|

|

|

|

A O U T 5 |

F ILT E R |

|

|

|

|

A IN A U X |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R S |

|

27 |

D E M |

|

|

|

|

|

|

|

|

|

R S |

|

2 |

|

|

|

|

|

|

|

|

|

|

|

H O LD /R U B IT |

|

|

2 6 |

A N A L O G |

|

||||

|

|

|

|

|

|

|

|

|||||

|

|

R S |

|

42 |

|

|

|

|

|

|||

|

|

|

R X 1 |

|

|

|

A O U T 6 |

F ILT E R |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

1 0 0 pF |

† |

|

|

|

|

|

|

|

|

|

D igital |

|

|

|

|

|

|

|

|

|

|||

R S |

|

|

|

|

|

|

3 |

|

|

|

||

A ud io |

|

1 |

D A T A U X /R X 4 |

|

S C L/C C LK |

|

|

|

||||

S ou rce |

|

|

|

|

|

4 |

|

|

|

|||

1 0 0 pF |

† |

|

|

|

S D A /C D O U T |

M icroco ntro ller |

||||||

|

|

|

|

|

|

6 |

||||||

|

|

|

|

|

|

|

|

|

A D 0/C S |

|

|

|

|

|

R S |

|

44 |

|

|

|

|

5 |

|

|

|

|

|

|

LR C K A U X /R X 3 |

|

A D 1/C D IN |

|

|

|

||||

|

|

|

|

† |

|

|

|

|

|

|

||

|

|

10 0 pF |

|

|

|

|

|

3 4 |

R D |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

S D IN 1 |

|

|

|

|

|

RS |

|

43 |

S C LK A U X /R X 2 |

|

|

3 3 |

R D |

|

|

|

|

|

|

|

† |

|

|

|

|

S D IN 2 |

|

|

|

|

|

1 0 0 pF |

|

|

|

|

3 2 |

R D |

|

|

||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

S D IN 3 |

|

|

|

|

M ode |

|

|

8 |

P D N |

|

|

|

3 6 |

R S |

|

|

|

|

|

|

|

|

|

|

|

||||

|

S etting |

|

|

7 |

I 2 C /S P I |

|

|

|

S D O U T 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

3 5 |

R S |

|

|

||

R S |

= 5 0 Ω |

|

|

|

|

|

|

|

S D O U T 2 |

|

A udio |

|

|

|

|

|

|

|

|

3 7 |

R S |

|

|||

R D |

= 4 7 5 Ω |

|

|

|

|

|

|

D S P |

|

|||

|

|

|

|

|

|

LR C K |

R |

|

|

|||

|

|

|

|

|

|

|

|

|

3 8 |

|

|

|

A ll unus ed digital inp u ts |

|

|

|

|

|

S C L K |

S |

|

|

|||

|

|

|

|

|

|

|

|

|||||

sh ou ld b e tie d to D G N D . |

|

|

|

|

3 1 |

|

|

|

||||

A ll un us e d ana lo g inp u ts |

|

|

|

|

|

C L K O U T |

|

|

|

|||

|

|

|

|

|

3 0 |

|

|

|

||||

sh ou ld b e le ft flo atin g . |

|

|

|

|

|

|

|

|

||||

|

|

|

|

O V L/E R R |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

||

* O ptional if an alo g inp uts |

A G N D 1 , 2 D G N D 1, 2 |

F IL T |

X T O |

X T I |

|

|

|

|||||

b ia se d to w ith in 1 % |

of |

|

|

|

|

|||||||

|

|

|

|

2 9 R X2 ** 2 8 |

|

|

|

|||||

C M O U T |

|

|

|

18 2 0 |

41 3 9 |

1 7 |

|

|

|

|||

† O nly needed w he n inpu ts |

|

R F IL T |

R X1 ** |

|

** |

|

256, |

|||||

a re used for S /P D IF. |

|

|

|

|

1xF s |

384, |

||||||

|

|

|

|

|

Loop Current |

|

|

|

|

512xF s |

||

|

|

|

|

|

|

|

|

|

|

|||

|

|

N orm al |

High |

|

|

|

|

|

|

|

C 1** |

C 2** |

C 1 |

4 0 |

pF |

40 |

p F |

|

|

||||

|

C FILT |

15 nF |

180 n F |

C F IL T |

|

|

|

|

|

C R IP |

|

|

|

|

|

|

C 2 |

1 0 |

pF |

40 |

p F |

|

|

|

R FILT |

4 3 kΩ |

3.3 k Ω |

|

|

|

|

|

|

|

|

|

|

|

|

R X1 |

3 0 0 k Ω |

sho rt |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

C RIP |

1.5 nF |

1 8 nF |

|

|

|

|

|

|

|

|

|

|

|

|

R X2 |

1 0 M Ω |

open |

|

||||

Figure 1. Recommended Connection Diagram |

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DS188F2 |