ЦОС_Заочники2013 / Курсовая МПиЦОС 2011 / Справочная информация / ADC&DAC / tlc320ac01

.pdf

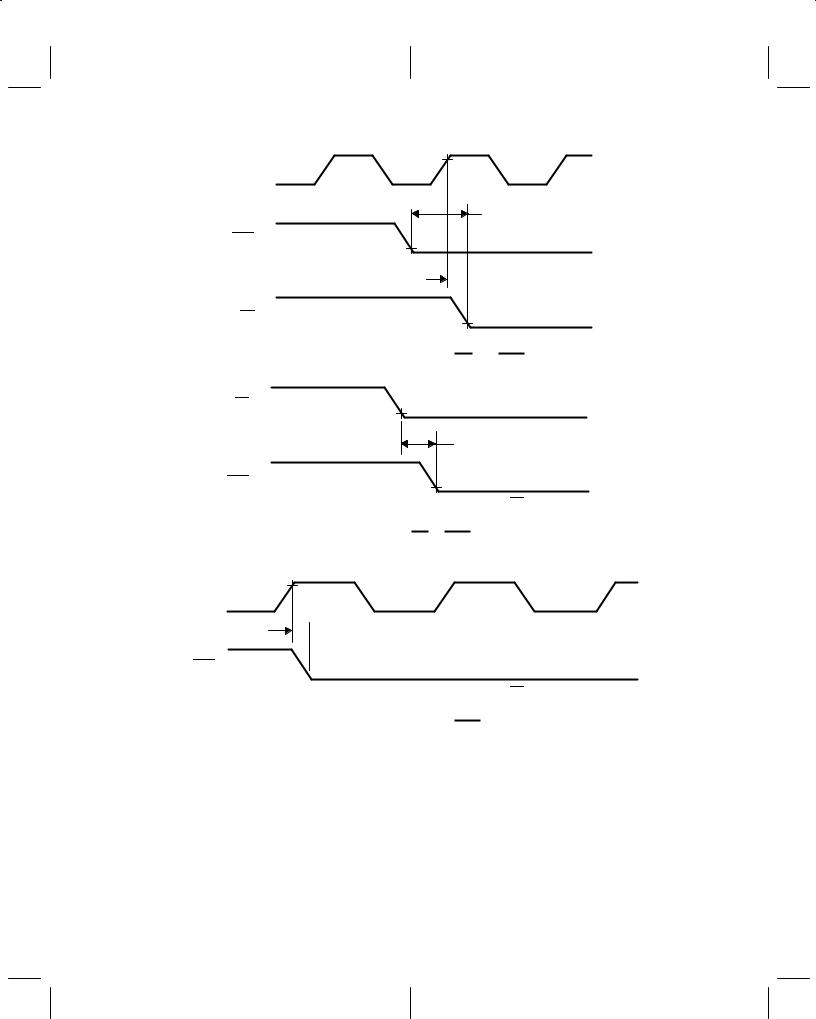

2.4 V

SCLK

SCLK Period/2

FSD

0.8 V

td(CH-FL)

td(CH-FL)

FS

0.8 V

NOTE A: Timing shown is for the TLC320AC01 operating as the master or as a stand-alone device.

Figure 4 – 4. Master or Stand-Alone FS and FSD Timing

FS

0.8 V

td(FL-FDL)

FSD

0.8 V

NOTE A: Timing shown is for the TLC320AC01 operating in the slave mode (FS and SCLK signals are generated externally). The programmed data value in the FSD register is 0.

Figure 4 – 5. Slave FS to FSD Timing

2.4 V

SCLK

0.8 V

td(CH-FDL)

td(CH-FDL)

FSD

0.8 V

NOTE A: Timing shown is for the TLC320AC01 operating in the slave mode (FS and SCLK signals are generated externally). There is a data value in the FSD register greater than 18 (decimal).

Figure 4 – 6. Slave SCLK to FSD Timing

4–3

2 V |

|

|

SCLK |

|

|

|

0.8 V |

|

|

td(CH-DOUT) |

|

Hi-Z |

2.4 V |

2.4 V |

DOUT |

0.4 V |

0.4 V |

|

||

Figure 4 – 7. DOUT Enable Timing From Hi-Z |

||

2 V |

|

|

SCLK |

|

|

|

0.8 V |

|

|

td(CH-DOUTZ) |

|

|

Hi-Z |

|

DOUT |

0.8 V |

|

|

|

|

Figure 4 – 8. DOUT Delay Timing to Hi-Z |

|

|

|

td(ML-EH) |

|

2 V |

|

2 V |

MCLK |

|

0.8 V |

0.8 V |

|

|

|

tr(EH) |

td(ML-EL) |

EOC |

2.4 V |

2.4 V |

0.4 V |

|

0.4 V |

|

|

tf(EL) |

|

Internal ADC |

|

|

Conversion Time |

|

Figure 4 – 9. EOC Frame Timing

4–4

|

Delay Is m Shift Clocks† |

Master |

|

FS |

|

|

Delay Is m Shift Clocks† |

Master FSD, |

Delay Is m Shift Clocks† |

Slave Device 1 FS |

|

Slave Device 1 FSD, |

|

Slave Device 2 FS |

|

Slave Device 2 FSD,

Slave Device 3 FS

Slave Device

(n – 1) FSD,

Slave Device n FS

†The delay time from any FS signals to the corresponding FSD signals is m shift clocks with the value of m being the numerical value of the data programmed into the FSD register. In the master mode with slaves, the same data word programs the master and all slave devices; therefore, master to slave 1, slave 1 to slave 2, slave 2 to slave 3, etc., have the same delay time.

Figure 4 – 10. Master-Slave Frame-Sync Timing After a Delay Has Been

Programmed Into the FSD Registers

|

|

t = 0 |

|

|

t = 1 |

|

|

t = 2 |

|

|

|

|

|

Sampling |

|

|

|

|

|

|

|

|

|

Period |

|

|

|

|

|

Master AIC |

FS |

|

|

|

|

|

|

|

|

Only Primary |

|

MP |

|

|

MP |

|

|

MP |

|

Frame Sync |

|

|

|

|

|

|

|||

|

|

|

1/2 Period |

|

|

|

|

||

|

|

|

|

|

|

|

|

||

Master AIC |

FS |

|

|

|

|

|

|

|

|

Only Primary |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

and Secondary |

FSD |

MP |

|

MS |

MP |

MS |

|

MP |

|

Frame Sync |

|

|

|

|

|

|

|

|

|

|

Value |

|

|

|

|

|

|

|

|

Master and Slave |

FS |

|

|

|

|

|

|

|

|

AIC Primary |

|

MP |

SP |

MP |

SP |

|

MP |

SP |

|

Frame Sync |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

Master and Slave |

FS |

|

|

|

|

|

|

|

|

AIC Primary and |

|

|

|

|

|

|

|

|

|

|

MP |

SP |

MS SS |

MP |

SP MS |

SS |

MP |

SP MS SS |

|

Secondary |

|

||||||||

|

|

|

|

|

|

|

|

|

|

Frame Sync |

|

|

|

|

|

|

|

|

|

MP = Master Primary |

SP = Slave Primary |

|

|

|

|

|

|||

MS = Master Secondary |

SS = Slave Secondary |

|

|

|

|

|

|||

Figure 4 – 11. Master and Slave Frame-Sync Sequence with One Slave

4–5

4–6

5 Typical Characteristics

Attenuation – dB

ADC LOW-PASS RESPONSE

0

TA = 25° C

TA = 25° C

FCLK = 144 kHz

–10

–20

–30

–40

–50

–60

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

fi – Input Frequency – kHz

NOTE A : Absolute Frequency (kHz) + Normalized Frequency FCLK (kHz)

144

Figure 5 – 1

5–1

Attenuation – dB

|

ADC LOW-PASS RESPONSE |

|||||

0.5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

0.4 |

|

|

TA = 25° C |

|

|

|

|

|

FCLK = 144 kHz |

|

|||

|

|

|||||

0.3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

0.1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

–0.1

–0.2

–0.3

–0.4

–0.5

0 |

0.5 |

1 |

1.5 |

2 |

2.5 |

3 |

3.5 |

4 |

fi – Input Frequency – kHz

NOTE A : Absolute Frequency (kHz) + Normalized Frequency FCLK (kHz)

144

Figure 5 – 2

5–2

Time – ms

|

|

|

|

|

|

ADC GROUP DELAY |

|

|

|

|

|

|

|||||||||

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TA = 25° C |

|

|

|

|

|||

0.9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

FCLK = 144 kHz |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

0.8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

|||||||||||

fi – Input Frequency – kHz

Normalized Frequency |

FCLK (kHz) |

NOTE A : Absolute Frequency (kHz) +

144

Figure 5 – 3

5–3

ADC BAND-PASS RESPONSE

Attenuation – dB

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TA = 25° C |

|

||||

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

fs = 8 kHz |

|

|||

– 10 |

|

|

|

|

|

FCLK = 144 kHz |

|

|||

|

|

|

|

|

|

|

|

|

|

|

– 20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

– 30 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

– 40 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

– 50 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

– 60 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

|

|

fi – Input Frequency – kHz |

|

|

||||

NOTE A : Absolute Frequency (kHz) + Normalized Frequency FCLK (kHz)

144

Figure 5 – 4

5–4

ADC BAND-PASS RESPONSE

Attenuation – dB

0.5

TA = 25° C

0.4fs = 8 kHz FCLK = 144 kHz

0.3

0.2

0.1

0

–0.1

–0.2

–0.3

–0.4

–0.5

0 |

0.5 |

1 |

1.5 |

2 |

2.5 |

3 |

3.5 |

4 |

fi – Input Frequency – kHz

NOTE A : Absolute Frequency (kHz) + Normalized Frequency FCLK (kHz)

144

Figure 5 – 5

5–5

Attenuation – dB

ADC HIGH-PASS RESPONSE

– 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

– 5 |

|

|

|

|

|

|

|

|

– 10 |

|

|

|

|

|

|

|

|

– 15 |

|

|

|

|

|

|

|

|

– 20 |

|

|

|

|

|

|

|

|

– 25 |

|

|

|

|

TA = 25° C |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

fs = 8 kHz |

|

|

|

– 30 |

|

|

|

|

FCLK = 144 kHz |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

50 |

100 |

150 |

200 |

250 |

|||

fi – Input Frequency – kHz

Normalized Frequency |

FCLK (kHz) |

NOTE A : Absolute Frequency (kHz) +

144

Figure 5 – 6

5–6