- •Радиостанция «Баклан-рн» Назначение

- •4.5.1.2 Технические характеристики

- •Конструкция радиостанции

- •Функциональная схема

- •Синтезатор

- •Радиоприемник

- •Усилитель «Селкол»

- •Усилитель мощности

- •Модулятор

- •Указания по эксплуатации

- •Лабораторная работа № 1

- •1.2.2. Функциональная схема радиостанции "Баклан".

- •1.3. Порядок проведения работы

- •1.3.1. Проверка работоспособности радиостанции.

- •1.3.2. Измерение чувствительности приемника.

- •1.3.3. Проверка работы подавителя шума.

- •1.3.4. Проверка работы автоматической регулировки усиления.

- •1.3.5. Измерение мощности передатчика.

- •1.3.6. Измерение стабильности частоты передатчика.

- •1.3.7. Анализ неисправности радиостанции.

- •1.4. Содержание отчета

Синтезатор

Синтезатор (Рис. 2) является составной частью трансиверной схемы радиостанции. В режиме «передача» он используется как возбудитель, в режиме «прием» как гетеродин и вырабатывает управляющее напряжение для перестройки входных цепей приемника. Кроме того, синтезатор обеспечивает задержку включения передатчика при переходе из режима «прием» в режим «передача» и наборе каналов до окончания переходных процессов, а также блокирует работу передатчика в случае отказа возбудителя.

Рис. 2. Функциональная схема синтезатора

В состав синтезатора входят следующие основные элементы: возбудитель-гетеродин (блок 2—3), состоящий из ГУН, ШУ и БУ; ОГ, ВЧ и ДОЧ (блок 2—2), ДПКД (блок 2—1).

Генератор, управляемый напряжением, состоит из автогенератора на полевом транзисторе типа 2П307Г и буферного каскада на транзисторе типа 2Т368А. Автогенератор выполнен по схеме индуктивной трехточки. Индуктивная ветвь контура выполнена катушкой индуктивности, емкостная ветвь — конденсаторами С1, С2 и варикапами. Встречно-последовательное включение варикапов уменьшает нелинейность контура, улучшая условия возбуждения и уменьшая перенос амплитудных флуктаций на частотные. Конденсатор С2 подбирается при регулировке для коррекции разброса емкости варикапов, а конденсатор С1 обеспечивает коррекцию коэффициента перекрытия по частоте. Резистор R3, конденсатор СЗ и диод ДЗ являются элементами автоматического смещения на затворе транзистора. Стабилизация режима работы транзистора обеспечивается резисторами R4, R24.

Напряжение питания подводится от источника +15 В через фильтры С22, Др7, С18, С15, Др5, СП, R5, С4. Управляющее напряжение на варикапы подается с выхода ЧФД через фильтр нижних частот и развязывающие резисторы Rl, R2. Высокочастотное напряжение через конденсатор С5 подается на базу транзистора Т2 буферного каскада, выполненного по схеме с общим эмиттером. В цепь коллектора включена согласующая индуктивность L2 и фильтр С6, Др1. Режим транзистора по постоянному току определяется резисторами R6, R7, R10. Резисторы R8, R9 обеспечивают стабилизацию рабочей точки и коэффициента усиления.

Широкополосный усилитель выполнен на двух транзисторах, которые включены по постоянному току последовательно. ШУ предназначен для усиления амплитуды напряжения ГУН и для ослабления реакции модулируемых каскадов передатчика на частоту ГУН. Индуктивность L3 и конденсатор С9 составляют фильтр верхних частот. Резисторы R12, R13, R14, R15, R11 обеспечивают требуемый режим транзисторов по постоянному току. Дроссель Др2 устраняет шунтирующее действие резистора R14 участка база-эмиттер Т4 по высокой частоте. С коллектора Т4 высокочастотное напряжение через разделительный конденсатор С10 и согласующую индуктивность L4 подается на базу ТЗ. Усиленный сигнал с коллектора ТЗ через разделительный конденсатор С12 и согласующую индуктивность L5 снимается на разъем Ш2 «Возбудитель- гетеродин» и через R17, С16 на базу транзистора Т6 буферного усилителя.

Буферный усилитель выполнен по каскадной схеме «общий змиттер – общая база» на транзисторах Т5, Т6 (2Т368А). Режим транзисторов по постоянному току обеспечивается резисторами R18, R19, R20, R21, R22. Конденсаторы С22, С18 и дроссели Др7, Др6 — элементы фильтра в цепи питания Цепь частотно-зависимой обратной связи образована резисторами R21, R22 и конденсатором С21. Конденсатор С17 блокировочный, а конденсатор С19 антипаразитный. С коллектора Т5 сигнал через фильтр нижних частот С20, L6, С23 поступает на вход ВЧД.

Опорный генератор выполнен на транзисторе Т1 (2Т306Б) по двухконтурной схеме. В качестве внешнего контура используется резистор R17. Внутренний контур состоит из емкостного делителя обратной связи С7, С9 индуктивной ветви, представляющей собой кварцевый резонатор ПЭ, и последовательно включенного с ним контура С5, С4, L, Д1, Д2, эквивалентного некоторому значению подстроечной индуктивности для температурной компенсации. Внутренний контур определяет частоту генерации, равную 6400 кГц. Высокая стабильность частоты обеспечивается применением метода температурной компенсации нестабильности частоты при помощи термозависимого потенциометра, составленного резисторами R1–R10 и емкости рп-перехода варикапов Д1, Д2.

Термозависимый потенциометр рассчитан так, что при изменении температуры окружающей среды закон изменения напряжения на варикапах зеркально повторяет температурно-частотную характеристику кварцевого резонатора. Таким образом обеспечивается эффект температурной компенсации нестабильности частоты ОГ. На транзисторе Т2 (2Т306Б) выполнен эмиттерный повторитель. Потенциометром R12, R14 производится начальная установка частоты и коррекции ее при старении радиодеталей. Конденсаторы C1 C2, СЗ, С10 – блокировочные. Резисторы R19–R21 обеспечивают номинальный режим транзисторов по постоянному току. Конденсаторы С8, С11 – разделительные. Относительная нестабильность ОГ не ниже ±10·10-6. С выхода эмиттерного повторителя напряжение снимается на вход ДОЧ.

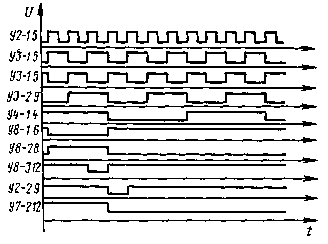

Делитель опорной частоты путем деления понижает частоту ОГ 6400 кГц до частоты сравнения ЧФД, 6,25 кГц. ДОЧ содержит формирователь входных логических уровней, десятиразрядный счетчик и формирователь выходных логических уровней импульсов. Синусоидальные колебания частоты 6400 кГц с выхода эмиттерного повторителя ОГ (У1) подаются на базу транзистора Т2 — формирователя уровней, представляющего собой ненасыщенный ключ. С коллектора транзистора снимаются прямоугольные импульсы с уровнями ЛОГ «1» — 2,4 В, ЛОГ «0» — 0,35. Десятиразрядный счетчик содержит три Д-триггера У2-1 У3-1, У3-2 (133ТМ2), работающих в режиме счета и JК-триггеры У4-1, У4-2, У5-1, У6-1, У6-2, У7-1, (134ТВ14). Формирователь выходного импульса ДОЧ состоит из триггеров У2-2, У7-2 и схемы совпадения У8-1, УШ2-2, У8-3. Фронт выходного импульса привязан с точностью до задержки в высокочастотных триггерах счетчика к фронту входного импульса триггера У2-1. Эпюры напряжений ДОЧ показаны на рис. 3.

Рис 3. Эпюры напряжений ДОЧ

Триггер формирователя выходного импульса переключается фронтом импульса, поступающего с триггера У2-1, но только в то время, когда на его вход Д поступает ЛОГ «0» со схемы совпадения У8-3. Одновременно этим же фронтом переключаются триггеры УЗ-1, УЗ-2, У4-1, которые обеспечивают срабатывание схемы совпадения и на выходе У8-3 формируется ЛОГ «1», благодаря чему триггер У2-2 с приходом следующего импульса возвращается в первоначальное положение. Таким образом, на выходе У2-2 формируется импульс нулевой полярности с длительностью 312,5 нс, равной периоду выходного сигнала У2-1. Этот импульс поступает на вход R триггера У7-2, устанавливает на его выходе ЛОГ «0». Разрешение на срабатывание триггера У2-2, т. е. подача на его вход Д ЛОГ «0» появляется после прихода на счетчик 1024-го импульса, когда переключаются триггеры У7-2, УЗ-1, УЗ-2, У4-1. Таким образом, триггеры У2-1, УЗ-1 – У7-1 десятиразрядного счетчика обеспечивают коэффициент деления частоты ОГ, равный 1024, что необходимо для получения частоты сравнения ЧФД:

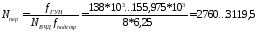

где

– частота колебаний ОГ,

– частота колебаний ОГ, – опорная частота сравнения ЧФД.

– опорная частота сравнения ЧФД.

Высокочастотный делитель предназначен для предварительного деления на 8 частоты ГУН и формирования прямоугольных импульсов для работы ДПКД. ВЧД состоит из трех динамических двоичных делителей частоты, выполненных на транзисторах Т1–ТЗ, Т5–Т6, Т8–Т9, межкаскадных буферных усилителей на транзисторах Т4, Т7, Т10 и формирователя логических уровней на транзисторах Т11, Т12.

Ячейка динамического делителя частоты выполнена по схеме мультивибратора, работающего в режиме синхронизации входным сигналом. Эпюры токов и напряжений для первой ячейки показаны на рис. 4. В интервале t1 – t2 отрицательный входной сигнал открывает диоды Д1, Д2 и транзисторы Т1, ТЗ поддерживаются в закрытом состоянии. t2 положительный входной сигнал стремится перевести оба транзистора в открытое состояние. Однако конденсатор С8 разрядится до более низкого потенциала, чем С4. Это обеспечивает быстрое смещение перехода эмиттер – база транзистора 75 в прямом направлении, и он открывается. Отрицательный импульс с коллектора ТЗ через конденсатор С7 и резистор R7 поступает на базу Т1, и он надежно закрывается. Конденсатор С8 будет заряжаться в течение времени t2–t3 током транзистора ТЗ. В интервале t3—t4, оба транзистора закрыты, а в интервале t3—t4 транзистор ТЗ закрыт, но Т1 открыт.

Выходное напряжение имеет форму пилообразного импульса с длительностью, равной двум периодам синхронизирующего напряжения. Буферные каскады первой и второй ячеек делителя трансформаторные, что обеспечивает согласование выгодных сопротивлений усилителей с входными сопротивлениями делителей.

Дроссели Др2, Др3, включенные в эмиттерные цепи транзисторов Т4, Т7, Т10, обеспечивают подавление высших гармонических составляющих спектра частот, приближая форму сигнала к синусоидальному. Транзисторы Т11, Т12 формирователя уровней импульсного выходного напряжения работают в нелинейном режиме, ограничивая синусоидальные колебания сверху и снизу, благодаря чему сигнал fподстр приобретает прямоугольную форму.

Делитель с переменным дробным коэффициентом деления предназначен для деления частоты ГУН, предварительно поделенной в ВЧД. ДПКД состоит из предварительного делителя, вентиля единиц, схемы управления вентилем единиц, управляемого делителя, схемы обеспечения дроби. ДПКД может работать в двух режимах «прием» и «передача». В режиме «передача» коэффициент деления ДПКД:

где

—

коэффициент предварительного делителя

ВЧД;

—

коэффициент предварительного делителя

ВЧД; - частота деления ЧФД.

- частота деления ЧФД.

Рис. 4. Эпюры токов и напряжений ячейки динамического делителя

В режиме «прием» синтезатор выполняет роль гетеродина и ГУН работает со сдвигом частоты на +20 МГц, поэтому коэффициент деления ДПКД

Переход из режима «прием» в режим «передача» осуществляется без изменения кода управления путем подачи +16,5 В на делитель R85, ,R86 схемы досчета. Управление коэффициентом деления осуществляется одиннадцатиразрядным кодом с передней панели радиостанции, т. е. переключателями набора частоты. При изменении выходной частоты синтезатора на 25, 50, 100, 1000 кГц коэффициент деления ДПКД изменяется соответственно на 0,5; 1,0; 2,0; 20,0.

Коэффициент деления изменяется тремя способами: изменением начального состояния счетчика (начальной установки), от которого начинается отсчет; изменением конечного состояния счетчика (опознаваемой комбинации), нахождение в котором говорит о том, что процесс счета окончен; пропуском при счете необходимого числа входных импульсов. Так, для изменения выходной частоты синтезатора через 1 МГц используется способ изменения начальной установки управляемого восьмиразрядного счетчика.

Диапазон изменения частоты синтезатора равен 17,975 МГц, поэтому достаточно производить установку пяти первых разрядов счетчика. Коэффициент деления предварительного делителя равен 20, поэтому изменение коэффициента деления управляемого делителя на единицу приводит к изменению результирующего коэффициента ДПКД на 20. В режиме «передача» коэффициент деления управляемого делителя изменяется от 118 до 135, а в режиме «прием» от 138 до 155.

В качестве опознаваемой комбинации выбрано поразрядное состояние счетчика 10100001, что эквивалентно приходу на счетчик 133 импульсов при начальной установке 00000000. 134-й импульс переключает триггер установки. Вырабатывается установочный импульс, который, воздействуя на схему установки, производит запись в счетчик начальной комбинации. 135-й импульс возвращает триггер установки в исходное состояние и импульс установки кончается. На этом цикл счета заканчивается, а следующий входной импульс будет первым для нового цикла счета.

Коэффициент деления управляемого делителя определяется разницей между числом импульсов, необходимым для заполнения счетчика до опознаваемой комбинации, и числом, соответствующим начальной установке. Например, коэффициент деления 118 получается как разность числа 135 опознаваемой комбинации и числа 17, записанного в счетчик.

Для увеличения коэффициента деления используется способ изменения опознаваемой комбинации управляемого делителя. В режиме «прием» счетчик устанавливается в опознаваемое состояние 10100001 после прихода 153-го импульса, а не 133-го, как в режиме «передача». Досчет 20 импульсов без изменения состояния счетчика на момент установки осуществляется специальной схемой досчета. 154-й импульс переключает триггер установки, а 155-й возвращает триггер установки в исходное состояние.

Получение шага сетки выходной частоты через 50 и 100 кГц достигается путем пропуска при счете необходимого числа импульсов. Для получения шага сетки через 50 кГц необходимо пропускать при счете один импульс, что увеличит коэффициент деления ДПКД на единицу, а для шага через 100 кГц — два импульса, обеспечивающих изменение коэффициента на две единицы.

Блокировка предварительного делителя ДПКД на время прохождения одного входного импульса производится вентилем единиц, который управляется специальной схемой управления, представляющей собой пятиразрядный счетчик.

Срабатывание вентиля единиц и счетчика происходит от выходных импульсов предварительного делителя. Блокировка вентиля единиц происходит в момент появления в счетчике схемы управления опознаваемой комбинации. Число срабатываний вентиля единиц определяется разницей между числом, соответствующим опознаваемой комбинации (11001, что соответствует 19 импульсам), и числом, соответствующим начальной установке счетчика схемы управления.

Для получения шага сетки частот 25 кГц необходимо получить дробный коэффициент деления ДПКД, изменяющийся на 0,5. Получение дробного коэффициента достигается пропуском одного входного импульса за два цикла счета ДПКД. Вентиль единиц в этом случае управляется схемой обеспечения дроби, которая в свою очередь управляется с передней панели радиостанции по одному проводу.

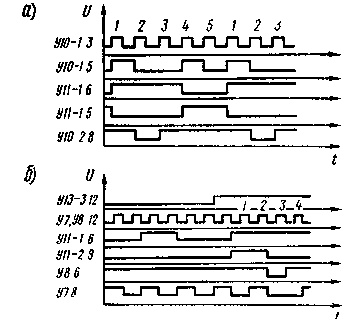

Предварительный делитель ДПКД состоит из двух делителей на 2—У7 (130ТВ1), У9 (133ТВ1) и делителя на 5—У10-1, У11-1, У10-2 133ТМ2). Общий коэффициент деления равен 20. Блокировка первого триггера У7 в нулевом состоянии осуществляется подачей на вход R ЛОГ «0» с выхода 06 триггера У8 вентиля единиц. Эпюры напряжений делителя на 5 показаны на рис. 5.

Вентиль единиц выполнен на триггерах У8 (130ТВ1), У11-2 (133ТМ2) и микросхеме У15-3 (136ЛА4). Командой для работы вентиля единиц является наличие на выходе 12 схемы «ИЛИ» У15-3 ЛОГ «1», а это может быть при подаче ЛОГ «0» на ее входы 01 или 13. При отсутствии команды со схемы управления или обеспечения дроби триггер У11-2 наличием на входе Д нуля удерживается в таком состоянии, что на его выходе Q9 — нуль. Этот ЛОГ «0», поступая на вход 04 триггера У8, удерживает его в состоянии, при котором на выходе 06 — ЛОГ «1», что в свою очередь обеспечивает нормальную работу триггеров У7 и У11-2. Эпюры работы вентиля единиц показаны на рис. 5.

При подаче ЛОГ «0» на вход 13 или 01 схемы «ИЛИ» У15-3 на выходе 12, а значит, на входе Д (12) триггера У11-2 появляется ЛОГ «1» и триггер переключается сигналом, приходящим с выхода 06 триггера У11-1 предварительного делителя. Этот же сигнал, но с выхода 05 У11-1 одновременно воздействует на счетчик схемы управления и переключает его. Триггер У11-2, переключившись, обеспечит подачу на вход I (04) триггера У8 ЛОГ «1». Но для переключения триггера У8 необходимо наличие ЛОГ «1» на всех входах I. Импульс I переключит триггер У7 в в единицу на выходе 08 и на вход 03 триггера У8 будет подана ЛОГ «1», т. е. на всех входах I триггера У8 будет уровень ЛОГ «1».

Рис. 5. Эпюры напряжений:

1 — делителя на 5, б — вентиля единиц

Следующий импульс 2 переключит триггеры У7 и У8 в нулевое состояние. Уровень ЛОГ «0» с выхода 06 триггера У8 поступает на входе R триггера У7 и заблокирует его в нулевом состоянии на время действия импульса 3. Одновременно этим же ЛОГ «0» триггер У11-2 возвращается в исходное состояние (на выходе 09 — нуль). Наличие нулей на I входах триггера У8 не запрещает ему переключаться из состояния ЛОГ «0» в ЛОГ «1» от импульса 3, но не разрешает переключаться от импульса 4 из состояния ЛОГ «1» в ЛОГ «0». Импульс 3 возвращает триггер У8 в исходное состояние, снимает блокировку с триггера У7 и импульс 4 переключает этот триггер, возвращая схему в исходное состояние. Таким образом, срабатывание вентиля единиц привело к пропуску при счете одного импульса (импульс 3) и, следовательно, к увеличению коэффициента деления ДПКД на единицу.

Число срабатываний вентиля единиц определяется длительностью уровня ЛОГ «0», поступающего с выхода схемы управления и зависит от кода установки, поступающего с переключателей выбора частоты.

Схема управления вентилем единиц состоит из счетчика импульсов У13-1, У13-2, У14-1, У14-2, У17-2 (134ТВ14), схемы установки У12-1, У12-2, У13-3, У12-4, У18-1 (136ЛАЗ), схемы формирования команды У15-1, У15-2 (136ЛА4), У17-1 (134ТВ14). Число срабатываний вентиля единиц определяется разницей чисел, соответствующих опознаваемой комбинации и начальной установке.

Импульс установки, поступая на схему установки, производит запись в счетчик начальной комбинации. На рис. 26 показаны эпюры работы схемы управления при установке в счетчик комбинации НПО. Для этой комбинации число пропущенных импульсов равно 4, а число, записываемое в счетчик — 15.

Импульс установки ЛОГ «1» поступает одновременно и на вход триггера У17-1 и подготавливает его к срабатыванию. Выходной импульс / (выход 06 триггера У11-1) предварительного делителя переключает триггер У17-1. Уровнем ЛОГ «1», снимаемым с выхода 09 триггера У17-1 разблокируется счетчик (У 13-1) и импульс поступает на схему У15-2. Если в счетчике было записано число, не соответствующее опознаваемой комбинации, то на выходе 06 схемы У15-1 в момент установки появляется ЛОГ «1», которая не препятствует переключению триггера У17-1 от импульса I и, поступая на вход 09 схемы У15-2, после переключения У17-1 дает на входе 08 схемы У15-2 ЛОГ «0», что является командой для работы вентиля единиц. Импульс 2, поступая на вентиль единиц, вызывает его срабатывание, пропускается в счетчике один импульс. Срабатывание вентиля единиц будет происходить до тех пор, пока счетчик не установится в опознаваемую комбинацию.

С появлением опознаваемой комбинации, т. е. срабатывания для рассматриваемого случая счетчика от импульса 5, на выходе 06 схемы У15-1 появляется ЛОГ «0», который вызывает на выходе 08 схемы У15-2 ЛОГ «1». Одновременно ЛОГ «0» поступает на вход R триггера У17-1, устанавливая на его выходе 09 ЛОГ «0». Так как на входах 09, 10 схемы У15-2 действует ЛОГ «0», на ее выходе 08 будет ЛОГ «1», т. е. оканчивается команда на работ} вентиля единиц. Уровень ЛОГ «0» с выхода 09 триггера У17-1, поступая на вход К триггера У13-1, не запрещает переключение триггера под действием импульса 6 из единичного состояния в нулевое, по запрещает обратное переключение под действием импульса 7. Таким образом, в счетчике устанавливается состояние 00001, которое сохраняется неизменным до момента установки.

Переключение триггера У14-1 от импульса 6 блокируется подачей на вход К ЛОГ «0», поступающего с выхода 13 триггера У17-2.

Управляемый делитель состоит из восьмиразрядного счетчика У21-2, У23-2, У24-2, У26-2, У28-2, У28-1, У29-2, У29-1 (134ТВ14); схемы установки У18-2, У18-3, У25-1, У25-2 (136ЛАЗ); схемы досчета У23-1, У26-1 (134ТВ14), У27-1, У27-2, У27-3, У27-4 (136ЛАЗ); триггера установки У21-1 со схемой сборки У22-1, У22-2; схемы формирования выходного импульса У22-3, У4-2 (130ЛА1). Коэффициент деления управляемого делителя в режиме «передача» 118—135, и в режиме «прием» 138—155. В режиме «передача» напряжение +16,5 В подается на делитель R85, R86, который формирует уровень ЛОГ «1» = 2,4 В, поступающий на элементы досчета У27-3, У27-4. Уровень ЛОГ «1» дважды инвертируется элементами У27-3, У27-2 и поступает на вход I триггера У23-1 независимо от остальных элементов управляемого делителя.

Рис. 6. Эпюры напряжении:

а - схемы управления; б – триггера установки

Установочный импульс, воздействуя на триггер У29-1, вызывает появление на его выходе 09 ЛОГ «0», который подается на входы R триггеров У26-1, У23-1 и на их выходах 09 также появляется ЛОГ «0». С выхода У23-1 ЛОГ «0» поступает на схему сборки У22-1, У22-2, с выхода которой ЛОГ «0» подается на вход I триггера установки У21-1, блокируя его от повторного срабатывания. После окончания импульса установки начинается процесс заполнения счетчика.

Срабатывание триггера У29-1 обеспечивает подачу на вход 13 У27-4 ЛОГ «1», а на входе 12 действует ЛОГ «1» с делителя R85, R.86. На выходе 11 У27-4 появляется ЛОГ «0», который подается на вход К триггера У24-2 и блокирует его от срабатывания. Когда же на выходе 09 триггера У29-1 появляется ЛОГ «1», триггер У23-1 разблокируется по входу R. При дальнейшем счете триггер У24-2 заменяется триггером У23-1, переключение которого вызывает блокировку триггера У23-2 (нуль на входе 08 триггера У23-1), единица с выхода 09 триггера У23-1 поступает на схему сборки.

В момент переключения триггера У21-2 в состояние ЛОГ «1» на входах сборки появляется комплект единиц, что приводит к появлению разрешения (ЛОГ «1» на входе I триггера У21-1) на срабатывание триггера установки. Эпюры работы триггера установки и схемы формирования выходного импульса показаны.

Импульс 7 переключает триггер У21-2 в состояние ЛОГ «1», в результате чего на выходе 06 У22-2 появляется ЛОГ «1». Импульс 2 переключает триггер установки У21-1. Вырабатывается установочный импульс, который блокирует триггер У21-2 на время действия импульса 3, возвращает триггер У29-1 в исходное состояние, который в свою очередь, воздействуя на триггер У23-1 возвращает его в исходное состояние, проходя через умощнительный каскад У25-4, поступает на схему установки и производит запись в счетчик начальной комбинации. Импульс установки поступает также на схему формирования выходного импульса У4-2.

Выходной импульс вырабатывается в момент совпадения установочного импульса и импульса 3, причем одинаковой длительности Установочный импульс, кроме того, поступая на вход I триггера У17-1, разрешает ему срабатывать от импульса 1. Снятие разрешения с входа I триггера У21-1 не препятствует его переключению от импульса 3, который возвращает триггер в исходное состояние. Импульс 4 будет первым для нового цикла счета.

В режиме «прием» на делитель R85, R86 напряжение + 16,5 В не поступает, а следовательно, на входах 10 У27-3 и 12 У27-4 действует ЛОГ «О». На выходе 11 У27-4 будет ЛОГ «1», которая подается на вход К триггера У24-2 независимо от состояния остальных элементов делителя. Наличие ЛОГ «О» на входе 10 У27-3 приводит к тому, что состояние входа I триггера У23-1 определяется состоянием триггеров У24-2, У26-1. Разрешение на срабатывание триггера У23-1 появится после переключения триггеров У24-2, У26-1 в состояние ЛОГ «1».

В процессе заполнения счетчика переключается триггер У29-1, блокируя триггер У28-2 и разблокируя триггеры У23-1, У26-1. Блокировка триггера У28-2 исключает его срабатывание при дальнейшем счете. Затем срабатывает У26-1, блокируя У26-2 и выдавая ЛОГ «1» на схему У27-1. После переключения У24-2 в состояние ЛОГ «1» на входах У27-1 появляется комплект единиц, что разблокирует У23-1 по I входу. Эпюры работы схемы досчета в режиме «прием» показаны на рис. 7.

Рис. 7. Эпюры напряжений: z —схемы досчета в режиме «прием»; 5 — временные положения команд, приходящих на вентиль единиц

Одновременно с переключением триггера У23-1 триггер У24-2 возвращается в состояние ЛОГ «О». Блокировка У26-2 от срабатывания осуществляется заблаговременно подачей на его вход К нуля с У26-1. Дальнейший процесс счета происходит так же, как и в режиме «передача». Таким образом, к моменту переключения У21-1 было просчитано дополнительно 20 импульсов с сохранением неизменной опознаваемой комбинации. Код установки счетчика в режимах «прием» и «передача» не меняется.

Схема обеспечения дроби выдает команды на вентиль единиц один раз за два цикла, обеспечивая дробный коэффициент делителя ДПКД. Схема состоит из триггера У24-1, фиксирующего счет циклов, и схемы У25-3, обеспечивающей формирование команды. Схема обеспечения дроби управляется с передней панели радиостанции по одному проводу 1р (7).

При выборе частот XXX, ХОО МГц, и XXX, Х50 МГц код управления схемой обеспечения дроби будет «О», а на частотах XXX, Х25 МГц и XXX, Х75 МГц равен «1». Команды кода управления подаются через входные цепи, защищающие срабатывание ДПКД от помех, наводимых в проводах управления. Входные цепи всех проводов выполнены по одинаковым схемам. Входная цепь провода 1р выполнена на транзисторе У1-5 (198НТ1Б), выполняющем роль ключа. Проводом 18 на делитель напряжения R1, Д12, R12, .R13 подается напряжение +18 В. С резистора R13 напряжение снимается на базу транзистора У1-5.

При подключении провода управления 1р к корпусу открывается диод Д1, напряжение с резистора R13 и базы У1-5 отключается, транзистор У1-5 закрывается, и с его коллектора напряжение +5 В подается на вход R триггера У24-1, удерживая его в нулевом состоянии, а на выходе У25-3 поддерживается ЛОГ «1» на протяжении всего цикла счета. Вентиль единиц не срабатывает.

При отключении провода управления от корпуса на резисторе R13 и базе У1-5 появляется напряжение, транзистор открывается, на вход R триггера У24-1 подается ЛОГ «О» и триггер У24-1 срабатывает при переключении триггера У29-2, которое происходит раз за цикл счета.

В момент установки происходит совпадение единиц на входах схемы У25-3. Это приводит к появлению ЛОГ «О» на выходе данной схемы, что является командой для срабатывания вентиля единиц. Так как совпадение единиц происходит через цикл, пропуск импульса ДПКД происходит один раз за два цикла счета, тем самым обеспечивается дробный коэффициент деления. Временное положение команд, приходящих на вентиле единиц со схем управления и обеспечения дроби.

Как было сказано выше, входные цепи всех проводов выполнены по одинаковым схемам, но с различными кодами управления, что достигается коммутацией проводов переключателями выбора частоты.

Частотно-фазовый детектор предназначен для сравнения частоты и фазы сигнала с выхода ДПКД fподстр с сигналом выхода ДОЧ fonop и формирования управляющего напряжения ГУН. В состав ЧФД входят: триггерный частотно-фазовый детектор, выполненный на микросхемах У16 (133ЛАЗ), У19, У20 (134ТВ14); ключ ТЗ и ограничитель Д23.

Напряжение частоты сравнения fопор с ДОЧ проводом 22 подается на вход 01 схемы У16-1 и на счетный вход У19-2. Напряжение частоты сравнения fподстр с выхода формиропателя ДПКД У4-2 подается на вход 05 схемы У16-2, на счетный вход триггера У19-1 и на R вход У19-2.

В работе ЧФД можно рассмотреть несколько случаев в зависимости от соотношения частот и фаз fподстр и fопор.

Если fподстр = fопор. и разница фаз постоянна, на выходе ЧФД 06 У16-3 формируются импульсы уровня ЛОГ «1» с постоянной длительностью, которые управляют ключом ТЗ, с коллектора которого проводом 21 снимается импульсное напряжение на ФНЧ, где оно интегрируется, и затем подается на варикапы ГУН Указанный случай является штатным в работе всего кольца АПЧ, а уровень управляющего напряжения калиброванным, относительно которого он будет изменяться в зависимости от знака и величины расстройки ГУН.

В случае fподстр > fопор происходит частотная автоподстройка ГУН. На выходе ЧФД формируется уровень ЛОГ «1», который открывает ключ ТЗ и с его коллектора через ФНЧ на ГУН подается управляющее напряжение около 2 В, что значительно ниже калиброванного уровня. Под действием этого напряжения емкость варикапов увеличивается и частота ГУН понижается.

Если fподстр < fопор, на выходе триггерного ЧФД У16-3 формируется уровень ЛОГ «О», транзистор ТЗ закрывается. Уровень управляющего напряжения высокий, но не более 12 В, что обеспечивает ограничитель Д23, емкость варикапов уменьшается и частота ГУН повышается. В этом случае на вход 13 У16-4 подается ЛОГ «О», а на вход 09 У16-3 ЛОГ «1». На выходе У16-3 поддерживается нуль до тех пор, пока за один период fопор придут два импульса fподстр. Это говорит о том, что произошло перерегулирование. На вход 13 У16-4 подается ЛОГ «1», и сигнал с выхода вентиля У16-3 поступает на Т-3. Начинается подстройка по фазе.

Схема запрета передачи предназначена для задержки включения передатчика до окончания переходных процессов в синтезаторе при переходе из режима «прием» в режим «передача» и отключения передатчика в случае отказа синтезатора в режиме «передача» Схема запрета передачи выполнена на микросхемах У3-3, У3-4, У3-5 и транзисторе Т4. При переходе в режим «передача» проводом 4 подается +16,5 В через R79 на эмиттер Т4 и через R70 на транзисторные ключи У3-4, УЗ-3. Проводом 19 подается +5 В на базы Т4, УЗ-3, У3-4.

Если в кольце АПЧ синтезатора отсутствует равенство частот, то на одном из триггеров (У20-1 выход 12 или У20-2 выход 0) в зависимости от знака расстройки формируется ЛОГ «1», воздействующая на базу ключа УЗ-4 или УЗ-3. Один из транзисторов открывается и конденсатор С22 разряжается через R70. Транзистор Т4, а значит, и 75 закрываются, и общая точка резисторов 3-2R27, 3-2R32 в модуляторе отключается от корпуса, передатчик выключается.

Если синтезатор исправен, т. е. fподст » fопор и схема АПЧ работает нормально, то при переходе на «передачу» проводом 4 подается +16,5 В через R79 на конденсатор С22. Постоянная времени заряда С22 выбрана такой, что когда напряжение на С22 достигает 6 В и транзистор Т4 открывается, переходные процессы в кольце АПЧ заканчиваются. Транзистор УЗ-5 открывается и замыкает общую точку резисторов 3-2R27, 3-2R32 на корпус, на выходные каскады передатчика подается напряжение + 13,5 В, и передатчик включается.