Лекции АВС / Лекция3

.doc

Лекция 3. Логическая структура микропроцессора

Для понимания основ современной ВТ имеет смысл рассмотреть базовую структуру микропроцессора. Главное в этой структуре - логика работы МП, поэтому можно рассматривать работу процессора без лишней детализации.

Рис. 1 Модель процессора Intel

Как видно из этой схемы в состав микропроцессора входят регистры (устройства хранения информации) АЛУ и устройства управления. Все действия по обработке информации выполняются с участием регистров. Регистры используются: 1. Для адресации ячеек памяти 2. Для выполнения арифметических операций. 3. Для хранения адреса стека. 4 Для хранения результатов выполнения операций (флаговый регистр).

Регистры имеют название и используются в соответствии со своим назначением.

Программная модель процессора Intel Pentium

Для понимания работы команд ассемблера необходимо четко представлять, как выполняется адресация данных, какие регистры процессора и как могут использоваться при выполнении инструкций. Рассмотрим базовую программную модель процессоров Intel Pentium, в которую входят:

– 8 регистров общего назначения, служащих для хранения данных и указателей;

– регистры сегментов – они хранят 6 селекторов сегментов;

– регистр управления и контроля EFLAGS, который позволяет управлять состоянием выполнения программы и состоянием (на уровне приложения) процессора;

– регистр-указатель EIP выполняемой следующей инструкции процессора;

– система команд (инструкций) процессора;

– режимы адресации данных в командах процессора.

Начнем с описания базовых регистров процессора Intel Pentium.

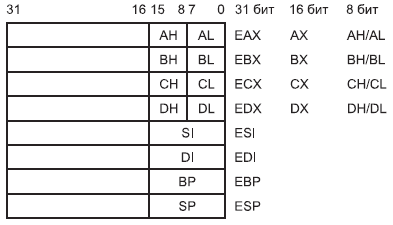

Базовые регистры процессора Intel Pentium являются основой для разработки программ и позволяют решать основные задачи по обработке данных. Все они показаны на рис. 2.

Рис. 2. Базовые регистры процессора Intel Pentium

Среди базового набора регистров выделим отдельные группы и рассмотрим их назначение. Начнем с 32-разрядных регистров общего назначения (ЕАХ, ЕВХ, ЕСХ, EDX, ESI, EDI, EBP, ESP), которые могут использоваться в качестве:

– операндов в арифметических и логических операциях;

– операндов при вычислении адресов операндов;

– указателей на переменные в памяти.

Несмотря на то, что любой из этих регистров можно использовать для вышеперечисленных операций, необходимо учитывать специфику применения регистра ESP – он служит для хранения указателя стека, поэтому задействовать его для других целей не рекомендуется.

Во многих случаях регистры общего назначения используются для предопределенных целей:

– ЕАХ выполняет функцию аккумулятора при работе с операндами и хранит результат операции;

– ЕВХ – указатель на данные, находящиеся в сегменте данных, адресуемом регистром DS;

– ЕСХ – счетчик циклов и элементов при строковых операциях;

– EDX – указатель на порты устройств ввода-вывода;

– ESI – указатель на данные, находящиеся в сегменте, адресуемом регистром DS (при выполнении строковых операций содержит смещение строки-источника);

– EDI – указатель на данные, находящиеся в сегменте, адресуемом регистром ES (при выполнении строковых операций содержит смещение строки-приемника);

– ESP содержит указатель стека в сегменте стека, адресуемом регистром SS;

– ЕВР содержит указатель на данные, находящиеся в стеке, адресуемом регистром SS.

Младшие 16 бит 32-разрядных регистров общего назначения могут адресоваться так же, как и 16-разрядные регистры в процессорах 8086 с именами АХ, ВХ, СХ, DX, ВР, s1 , DI, SP. В свою очередь, 16-разрядные регистры АХ, ВХ, СХ и DX позволяют обращаться отдельно как к старшим 8-разрядным регистрам (АН, ВН, СН, DH), так и к младшим (AL, BL, CL, DL). Это проиллюстрировано рис. 3.

Сегментные регистры (CS, DS, SS, ES, FS и GS) содержат 16-разрядные селекторы сегментов. Селектор представляет собой специальный указатель, который идентифицирует данный сегмент в памяти.

Рис. 3. Использование регистров общего назначения

Помимо регистров общего назначения и сегментных регистров, как мы знаем, в базовой архитектуре имеется еще два регистра: регистр управления/состояния EFLAGS и регистр-указатель адреса следующей инструкции El Р. Рассмотрим их более подробно.

Регистр EFLAFS, часто именуемый регистром флагов, имеет 32 разряда и содержит группу битов или, как их чаще называют, флагов состояния, управляющий флаг и группу системных флагов. На рис. 3.8 показана структура регистра флагов и приводится расшифровка наиболее часто используемых флагов.

Указанные на рис. флаги наиболее часто используются в прикладных программах и сигнализируют о следующих событиях:

– OF (флаг переполнения) фиксирует ситуацию переполнения, то есть выход результата арифметической операции за пределы допустимого диапазона значений;

– DF (флаг направления) используется командами обработки строк. Если DF = 0, строка обрабатывается в прямом направлении, от меньших адресов к большим. Если DF = 1, обработка строк ведется в обратном направлении;

– SF (флаг знака) показывает знак результата операции, при отрицательном результате SF = 1;

– ZF (флаг нуля) устанавливается в 1, если результат операции равен 0;

– AF (флаг вспомогательного переноса) используется в операциях над упакованными двоично-десятичными числами. Этот флаг служит индикатором переноса или заема из старшей тетрады (бит 3);

– PF (флаг четности) устанавливается в 1, если результат операции содержит четное число двоичных единиц;

– CF (флаг переноса) показывает, был ли перенос или заем при выполнении арифметических операций.

Из всех этих флагов только флаг переноса CF может устанавливаться или сбрасываться непосредственно при помощи команд ассемблера

Рис. 4. Регистр управления/состояния процессора

Управление памятью

Память в значительной мере определяет возможности ПК. Основными требованиями к памяти являются объем, быстродействие, стоимость, энергонезависимость. Эти параметры противоречивы, не существует устройства памяти, выполняющего все эти требования. В настоящее время память реализуется в виде иерархической многоуровневой системы, состоящей из нескольких устройств. Управление памятью осуществляют контроллеры и процессор.

Информационный объем ОП в современных ПК составляет 256 Мбайт - 3Гбайт

ОП имеет линейно-адресную организацию. В процессе работы процессор постоянно взаимодействует с ОП, обмениваясь с ней данными и выбирая команды. Физически ОП реализуется на СБИС динамической памяти (DRAM), быстродействие которых в силу специфики работы ограничено значениями 20-40 нс. Для достижения максимальной производительности ВМ и обеспечения нормального функционирования в многозадачном режиме разработчикам ВМ приходится решать ряд проблем, связанных с обеспечением взаимодействия процессора с ОП.

Одной из проблем взаимодействия является согласование скоростных характеристик процессора и ОП. При современном уровне развития микроэлектроники процессор имеет значительно более высокое быстродействие по сравнению с быстродействием ОП. При этом с ростом тактовой частоты процессоров все большую долю в задержке обмена процессора данными с ОП составляет задержка в связях по СШ (вне кристалла процессора). Основным архитектурным способом согласования скоростных характеристик процессора и ОП является кэширование ОП. Под кэшированием понимается использование быстродействующей буферной памяти относительно малого размера, выполненной на элементах памяти статического типа (триггерах), которые имеют более высокое быстродействие по сравнению с динамическими элементами ОП. В эту буферную память из ОП помещаются копии команд и данных, относящихся к обрабатываемому в данный момент фрагменту программы. Работа буферной памяти прозрачна для программ, т. е. скрыта от пользователя. По этой причине ее называют кэш-памятью (cache - тайник).

Кэш-память размещается в непосредственной близости от процeccopного ядра, при этом ее работа наиболее эффективна, если она встроена внутрь кристалла процессора (кэш 1-го уровня Ll). Ограниченность объема кристалла не позволяет реализовать в процессоре внутренний кэш большой емкости. Объем внутренней кэш-памяти процессоров редко превышает 16-32 Кбайт. В большинстве современных компьютеров используют 2- или 3-уровневую кэш-память (рис). Раздельные кэш команд и кэш данных 1-го уровня размещаются внутри кристалла процессора. Кэш-память 2-го уровня - L2 (ее размер составляет 256-512 Кбайт) часто располагается в одном корпусе с процессором и соединяется с ним с помощью специальной локальной шины, работающей на основной или половинной частоте процессора. Кэш-память 3-гоуровня - L3 объемом несколько Мбайт размещается на системной плате компьютера. Обычно все содержимое кэш Ll находится в кэш L2, а все содержимое кэш L2 является частью кэш L3. Принципы построения кэш-памяти всех уровней сходны. В целом ОП вместе с кэшами всех уровней представляет собой единую систему памяти, непосредственно доступную процессору для чтения и записи данных, а также считывания команд программы.

Вторая проблема организации взаимодействия процессора с ОП связана с автоматизацией распределения ОП между процессами (задачами) в многозадачном режиме работы ВМ и автоматизацией обменов ОП с внешней памятью.

При всех достоинствах ОП (относительно малое время доступа, возможность произвольного обращения к любым ячейкам памяти и др.) стоимость ОП сравнительно велика, кроме того, она не обладает энергонезависимостью. Поэтому основной по информационному объему в системе памяти компьютера является внешняя память ВЗУ. Она представлена в виде различных накопителей со сменными и несменными носителями (ЖД, ГД, накопитель на оптических магнитных дисках и т. п.). Внешняя память является самой медленной, но ее важным достоинством является большой объем хранимой информации, энергонезависимость и существенно более низкая стоимость по сравнению с другими типами памяти. В частности, информационная емкость ЖД достигает уже нескольких сотен Гбайт, а относительная стоимость памяти ЖД более чем на два порядка ниже стоимости оп. Большой объем ВЗУ позволяет хранить программы и данные, размер которых может существенно превышать объем оп. Однако процессор не имеет прямого доступа к командам и данным, размещенным в ВЗУ, и вынужден осуществлять опосредованную связь с ВЗУ через программно-аппаратное обеспечение. При отсутствии требуемой части программы и данных в ОП осуществляется подкачка недостающих данных из ВЗУ.

Проблема автоматизации обмена с внешней памятью решается с использованием концепции «виртуальной памяти» и созданием в составе кристалла процессора средств аппаратной поддержки управления виртуальной памятью.

Кэш-память используется в качестве промежуточного буфера ОП для хранения копий блоков информации ОП, вероятность обращения к которым в ближайшее время велика. Дополнительно адресуемой памяти кэш не добавляет, и его использование не расширяет адресного пространства процессора. При наличии кэш-памяти требуемых данных и команд процессор быстро обменивается информацией с КЭШем, не выполняя непосредственных обращений к ОП. В системах с кэш-памятью информация пересылается по цепочке: внешняя память – основная память-кэш –память - операционный блок процессора и обратно. Организация кэш-памяти предусматривает ее обмен с ОП блоками фиксированного размера (32-128 байт). Управляет работой КЭШа специальный контроллер, одной из функций которого является проверка наличия запрашиваемой команды и данных (кэш-попадание, кэш-промах).

Проблема автоматизации обмена с внешней памятью решается с использованием концепции виртуальной памяти аппаратными средствами.

Модель памяти определяет способ организации программ и данных в памяти компьютера. В 32-разрядной архитектуре процессора Intel Pentium используются три модели памяти:

1. Плоская, или линейная, модель памяти (flat memory model) – память представляет собой непрерывное пространство адресов. Программный код, данные, область стека располагаются в этом пространстве адресов. Адресное пространство в этой модели адресуется побайтно, а диапазон адресов равен 2 32. Схематично эта модель памяти показана на рисунке;

Рис. Линейная модель памяти

2. Сегментированная модель памяти (segmented memory model) – память состоит из трех отдельных пространств адресов, которые называются сегментами. При этом программный код, данные и стек размещаются в отдельных сегментах памяти. Для того чтобы обратиться к байту в памяти, программа формирует логический адрес, состоящий из адреса сегмента (селектора сегмента) и смещения. Программы, выполняющиеся в 32-разрядном режиме, могут использовать до 16 383 сегментов разного размера, каждый из которых может иметь размер 2 32 байт. Схема адресации для сегментированной модели памяти показана на рисунке.

Механизм преобразования адресов при использовании сегментированной модели таков: вначале все адреса сегментов, определенных в программе, отображаются на общее линейное пространство адресов, доступное процессору. Затем логический адрес операнда в памяти преобразуется в линейный адрес из пространства адресов. Все эти преобразования прозрачны для работающей программы. Подобная модель позволяет повысить надежность работы программ. Например, если разместить программный код и область стека в разных сегментах, то в случае резкого увеличения размера стека не произойдет перекрытия программного кода данными из стека;

3. Модель реального режима адресации (real-address mode memory model) – это модель памяти, используемая в процессорах 8086. Данная модель памяти поддерживается для того, чтобы обеспечить совместимость с ранее разработанными 16-разрядными приложениями. В этой модели применяется механизм сегментации, причем максимальный размер сегмента не превышает 64 Кбайт. Максимальный размер линейного адресного пространства, доступного в этом режиме, равен 220 Кбайт.

Рис. Сегментированная модель памяти

При выполнении любой программы процессор обращается к памяти, в которой хранятся команды и данные. Для доступа к данным необходимо определять их адрес в памяти. Способ формирования адреса операнда или метки перехода на другую команду называется режимом адресации, или адресацией.

Некоторые команды требуют явного указания операндов, в то время как другие используют операнды по умолчанию. Данные операнда-источника могут находиться в регистре, памяти, в порту ввода-вывода или задаваться непосредственно в инструкции. Операнд-приемник может располагаться в оперативной памяти, в регистре или быть портом ввода-вывода.

Адрес операнда формируется по схеме адрес сегмента + cмещение. В зависимости от используемой модели памяти адрес переменной в памяти может формироваться как 16 : 16 или 16 : 32. Смещение операнда называется его эффективным или исполнительным адресом (Effective Address, EA).

Обычно адрес сегмента загружается в сегментный регистр, а сам регистр выбирается в зависимости от типа выполняемой операции.

Процессор автоматически выбирает сегмент в зависимости от типа операции. При сохранении операнда в памяти или загрузке из памяти в качестве сегментного регистра по умолчанию используется DS, но можно и явным образом указать сегментный регистр, применяемый в операции.

Подсистемы управления памятью.

Для управления адресным пространством используются подсистемы управления памятью. Существует несколько вариантов таких посистем.

Подсистема управления памятью решает две основные задачи – защита выполняющихся в ЭВМ процессов и распределение памяти между процессами. Процессор обращается к памяти в терминах адресов: у каждого байта есть номер или физический адрес. Который однозначно определяет этот байт. Набор из адресов всех байтов памяти называют физическим адресным пространством. Для решения задач управления памятью используются аппаратные средства, именуемые виртуальной памятью. Её функция состоит в том, что бы обеспечить дополнительное адресное пространство и механизмы преобразования адресов из одного пространства в другое. Это дополнительное адресное пространство называют виртуальным адресным пространством, а адреса в нем – виртуальными адресами. В отличие от физического виртуальное адресное пространство – это ничему не соответствующий набор адресов. Внести смысл в его существование можно присваивая по определенному правилу виртуальным адресам адреса физические, тогда виртуальный адрес станет номером реального байта памяти.

Для защиты памяти одного процесса от случайного посягательства на нее со стороны других процессов каждому процессу ставится в соответствие свое виртуальное пространство – набор адресов от от 0 до максимального номера, допустимого для данного процесса, и правило преобразования виртуальных адресов в физические Для обозначения виртуального пространства процесса применяют термин «адресное пространство процесса». Работая в своем адресном пространстве процесс не в состоянии записать что либо в пространство другого процесса.

Для использования механизма виртуальной памяти необходимо включить в ЭВМ специальное устройство – диспетчер управления памятью – осуществляющее преобразование пары номер процесса и виртуальный адрес в в физический адрес. В современных процессорах это отдельный блок в составе процессора. Но ранее диспетчер был часто отдельным чипом в составе ЭВМ.

Обычно правила преобразования задаются в форме таблицы, в которой хранятся соответствия между диапазонами физических и виртуальных адресов. Адреса группируют в наборы по нескольку тысяч последовательных адресов в каждом, например в наборы по 4096 адресов. Такой набор называется страницей. Если это страница физических адресов, то ее именуют физической страницей или страницей памяти. Соответственно страницу виртуальных адресов называют виртуальной страницей. Страницы пронумерованы и номер страницы является ее адресом. Для диспетчера управления памятью имеется таблица адресов физических страниц. Диспетчер по адресу виртуальной страницы вычисляет место в таблице, где находится адрес соответствующей физической страницы. При замене одного активного процесса другим в многозадачном режиме диспетчеру указывают адрес в памяти, где находится таблица страниц нового процесса, которую нужно будет использовать для нового процесса. Для ускорения работы по преобразованию виртуальных адресов в физические в процессоре организуют память небольшого объема – буфер преобразования адреса, в котором хранится копия отдельных элементов таблицы страниц. При преобразовании виртуального адреса в физический процессор вначале ищет соответствие между страницами в буфере и только если не находит заданного адреса обращается к таблице страниц в памяти. Это приводит к заметному снижению количества обращений в памяти повышению производительности.