- •АРХИТЕКТУРЫ

- •ВЕНТИЛИ

- •ТРАНЗИСТОРНЫЙ ИНВЕРТОР

- •ВЕНТИЛЬ НЕИ

- •ВЕНТИЛЬ НЕИЛИ

- •ИЗОБРАЖЕНИЯ 5 ОСНОВНЫХ ВЕНТИЛЕЙ

- •БУЛЕВА АЛГЕБРА

- •ФУНКЦИЯ

- •ТАБЛИЦА ИСТИННОСТИ ДЛЯ ФУНКЦИИ БОЛЬШИНСТВА

- •АЛЬТЕРНАТИВНЫЙ ВИД ЗАПИСИ

- •РЕАЛИЗАЦИЯ БУЛЕВЫХ ФУНКЦИЙ

- •РЕАЛИЗАЦИЯ БУЛЕВЫХ ФУНКЦИЙ С ИСПОЛЬЗОВАНИЕМ ТОЛЬКО ОДНОГО ВИДА ВЕНТИЛЕЙ

- •ЭКВИВАЛЕНТНОСТЬ СХЕМ

- •ВЫПОЛНЕНИЕ

- •ЗАКОНЫ БУЛЕВОЙ АЛГЕБРЫ

- •ИСКЛЮЧАЮЩЕЕ ИЛИ: ПРИМЕР ЗАПИСИ ЧЕРЕЗ ОДИНАКОВЫЙ ВЕНТИЛЬ

- •ОСНОВНЫЕ

- •ИНТЕГРАЛЬНЫЕ СХЕМЫ

- •ИНТЕГРАЛЬНЫЕ СХЕМЫ

- •МИС(МАЛАЯ ИНТЕГРАЛЬНАЯ СХЕМА)

- •НЕКОТОРЫЕ СООБРАЖЕНИЯ

- •МУЛЬТИПЛЕКСОРЫ

- •МУЛЬТИПЛЕКСОРЫ

- •МУЛЬТИПЛЕКСОРЫ

- •ДЕКОДЕРЫ

- •КОМПАРАТОРЫ

- •ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ

- •АРИФМЕТИЧЕСКИЕ СХЕМЫ: СХЕМА СДВИГА

- •АРИФМЕТИЧЕСКИЕ СХЕМЫ: ПОЛУСУММАТОР

- •АРИФМЕТИЧЕСКИЕ СХЕМЫ: ПОЛНЫЙ

- •СУММАТОР СО СКВОЗНЫМ ПЕРЕНОСОМ

- •АРИФМЕТИКОЛОГИЧЕСКОЕ УСТРОЙСТВО

- •АРИФМЕТИКОЛОГИЧЕСКОЕ УСТРОЙСТВО

- •АРИФМЕТИКОЛОГИЧЕСКОЕ УСТРОЙСТВО

- •ТАКТОВЫЕ ГЕНЕРАТОРЫ

- •ТАКТОВЫЕ ГЕНЕРАТОРЫ

- •ОСНОВНЫЕ

- •SRЗАЩЕЛКИ

- •SRЗАЩЕЛКИ

- •СИНХРОННЫЕ SRЗАЩЕЛКИ

- •СИНХРОННЫЕ DЗАЩЕЛКИ

- •ТРИГГЕРЫ

- •DТРИГГЕР

- •DЗАЩЕЛКИ И DТРИГГЕРЫ

- •РЕГИСТРЫ

- •ОРГАНИЗАЦИЯ ПАМЯТИ

- •ВОПРОСЫ?

СУММАТОР СО СКВОЗНЫМ ПЕРЕНОСОМ

Чтобы построить сумматор для 32битных слов, нужно использовать 32 однобитных сумматора.

Суммирование осуществляется справа налево с переносом бита переноса.

Можно ли ускорить данный процесс?

31

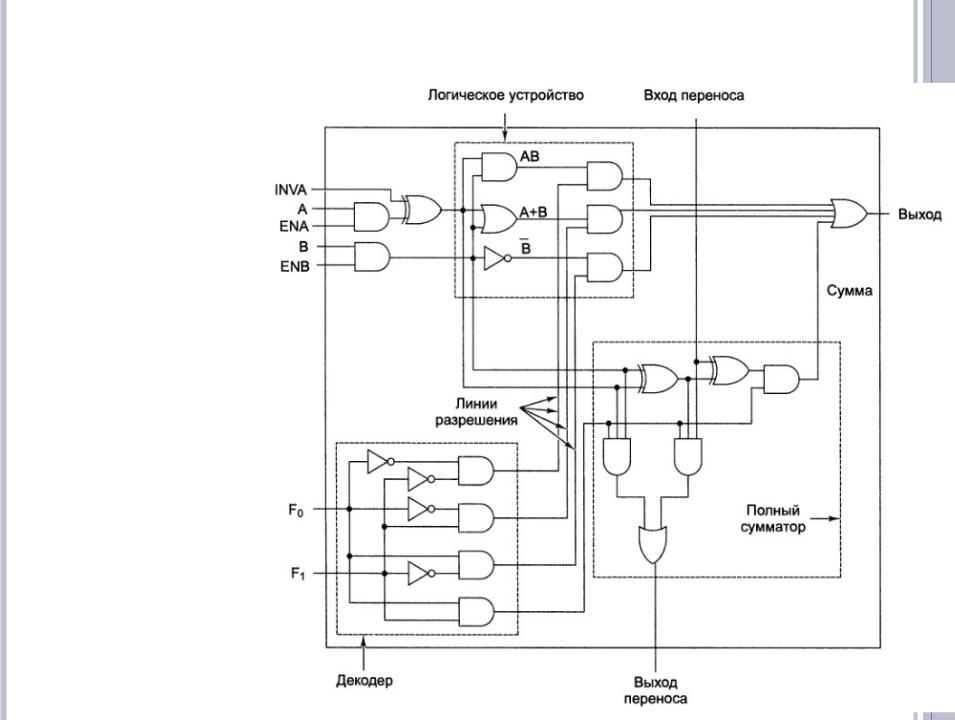

АРИФМЕТИКОЛОГИЧЕСКОЕ УСТРОЙСТВО

Большинство компьютеров содержат 1 схему для выполнения операций И, ИЛИ и сложения над двумя машинными словами. Для Nбитных слов такая схема состоит из N одинаковых схем для индивидуальных битовых позиций.

32

АРИФМЕТИКОЛОГИЧЕСКОЕ УСТРОЙСТВО

В левом нижнем – декодер

В левом верхнем – логическое устройство

В нижнем правом – полный сумматор

33

АРИФМЕТИКОЛОГИЧЕСКОЕ УСТРОЙСТВО

34

ТАКТОВЫЕ ГЕНЕРАТОРЫ

Для контроля временных отношений в цифровые схемы встраиваются тактовые генераторы

Тактовый генератор – это схема, вызывающая серию импульсов, одинаковых по времени

Временной интервал между началом одного импульса и началом следующего называется временем такта

35

ТАКТОВЫЕ ГЕНЕРАТОРЫ

|

Более мелкие |

промежутки |

|

|||

|

времени |

можно |

получить |

|

||

|

поставив |

схему |

задержки |

|

||

|

сигнала (а). |

|

|

|

|

|

|

Возможны |

следующие |

|

|||

|

дискретные |

|

события: |

|

||

|

нарастающий |

фронт |

С1, |

|

||

|

задний |

фронт |

С1, |

|

||

|

нарастающий |

фронт |

С2, |

|

||

|

задний фронт С2. |

|

|

|

||

|

Иногда |

делают |

привязку |

|

||

|

события к уровню импульса |

|

||||

|

– (С1=0 и С2=0) |

(С1=1 и |

|

|||

|

С2=0) (С1=0 и С2=1) (С1=1 и |

|

||||

|

С2=1) |

|

|

|

|

|

|

Классифицируют |

|

на |

|

||

|

синхронные |

|

|

и |

|

|

|

несинхронные генераторы. |

36 |

||||

|

|

|

|

|

|

|

ОСНОВНЫЕ

ЦИФРОВЫЕ ЛОГИЧЕСКИЕ СХЕМЫ

ПАМЯТЬ: SRЗАЩЕЛКИ,

СИНХРОННЫЕ SRЗАЩЕЛКИ,

СИНХРОННЫЕ DЗАЩЕЛКИ, ТРИГГЕРЫ, РЕГИСТРЫ, ОРГАНИЗАЦИЯ ПАМЯТИ, ОЗУ И ПЗУ

37

SRЗАЩЕЛКИ

Чтобы создать 1 бит памяти, надо какимто образом запоминать предыдущие входные значения. Такую схему можно сконструировать из двух вентилей НЕИЛИ.

В результате получим SRзащелку. S – setting – установка, R – resseting – сброс. В отличие от комбинационной схемы, выходные сигналы защелки не определяются текущими входными сигналами.

38

SRЗАЩЕЛКИ

39

СИНХРОННЫЕ SRЗАЩЕЛКИ

Требуется, чтобы защелка меняла свое состояние только в определенное время. Схема имеет синхронизирующий вход. Если он равен 0, то оба вентиля И равны 0 независимо от S и R, и защелка не меняет состояние. Когда значение синхронизирующего сигнала равно 1, действие вентилей И исчезает и состояние защелки становится зависимо от S и R. 40

Какие проблемы наблюдаются в случае, если S и R принимают одинаковые значения одновременно?