- •Память

- •Двоично-десятичный код

- •Двоично-десятичный код

- •Address

- •Address

- •Код с исправлением ошибок

- •Иллюстрация кода с исправлением ошибок (метод Хэмминга) для 4-битных слов

- •Алгоритм Хэмминга для 16- битных слов

- •Алгоритм Хэмминга для 16- битных слов

- •Алгоритм Хэмминга для 16- битных слов

- •Алгоритм Хэмминга для 16-битных слов

- •Кэш-память

- •Кэш-память

- •Оперативная память

- •FPM DRAM (Fast Page Mode DRAM)

- •EDO-DRAM (Extended Data Out)

- •BEDO (Burst EDO) - пакетная EDO RAM

- •SDRAM (Synchronous DRAM) - синхронная DRAM

- •SDRAM (Synchronous DRAM) - синхронная DRAM

- •DDR SDRAM, SDRAM II (Double Data Rate SDRAM) SDRAM с удвоенной скоростью передачи

- •Сравнительная характеристика основных типов памяти

- •Конструктивные исполнения памяти DRAM

- •Конструктивные исполнения памяти DRAM

- •Конструктивные исполнения памяти DRAM

- •Конструктивные исполнения памяти DRAM

- •Конструктивные исполнения памяти DRAM

- •Конструктивные

- •Конструктивные исполнения памяти DRAM

- •Конструктивные исполнения памяти DRAM

- •Конструктивные исполнения памяти DRAM

- •Иерархическая структура памяти

- •Магнитный диск

- •Магнитный диск

- •Магнитный диск

- •Большинство магнитных дисков состоит из нескольких пластин, расположенных друг под другом.

- •ESDI

- •SCSI

- •SCSI

- •SCSI

- •SCSI

- •SCSI

- •Сравнение дисковых интерфейсов

- •RAID уровня 0

- •RAID уровня 2

- •RAID-массивы

- •RAID-массивы

- •RAID-массивы

- •RAID-массивы

- •RAID уровня 4

- •RAID-массивы

- •RAID-массивы

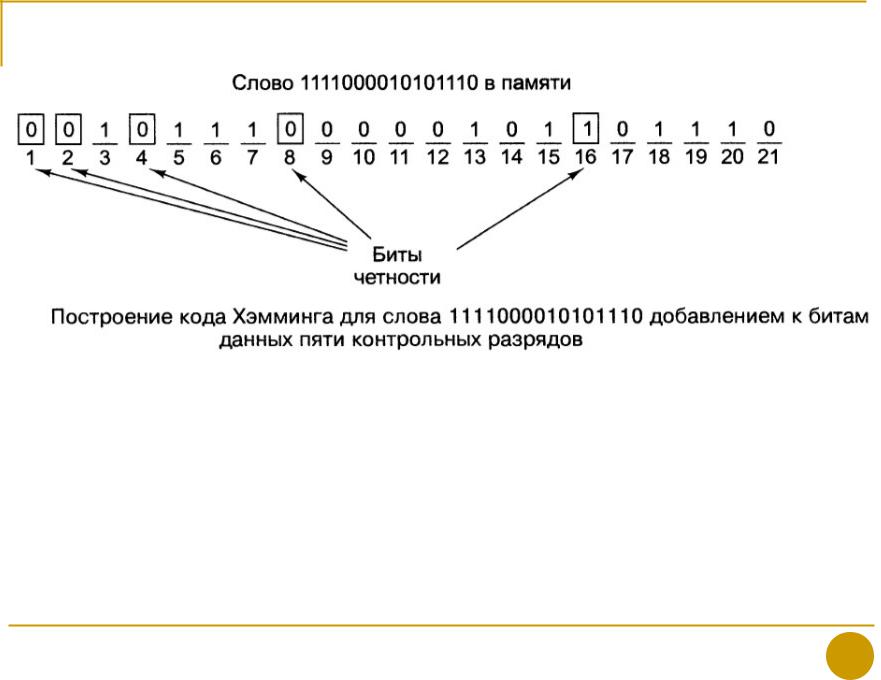

Алгоритм Хэмминга для 16- битных слов

Возьмем слово 1111000010101110

Кодированное слово 001011100000101101110

Допустим произошла одиночная ошибка

001001100000101101110

Проверим биты четности

Биты 2,8,16 – правильные, 1,4 – неправильный. В результате исключений приходим к выводу, что ошибка в 5 бите.

12

A

B

Ошибка

0 10 C

C

1 1 1

0

0

КорреОшибкатно

13

Алгоритм Хэмминга для 16-битных слов

Найти неправильный бит можно и гораздо быстрее:

Сначала нужно подсчитать все биты четности;

Если они правильные, ошибки нет (или есть, но ошибка не однократная)

Если обнаружились неправильные биты четности, нужно сложить их номера. Сумма, полученная в результате, даст номер позиции неправильного бита.

14

Кэш-память

Процессоры работали всегда быстрее, чем память.

На практике получается следующее: после того как процессор дает запрос памяти, должно пройти несколько циклов, прежде чем он получит запрашиваемое.

Два способа решения:

программное (пустые циклы),

аппаратное (сложно реализуемое).

Оба варианта ведут к снижению производительности

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 0 1 0 10 1 1 0 0 0 |

0 |

0 |

1 |

0 |

1 1 |

0 |

1 |

1 |

1 |

0 |

|||||||

|

||||||||||||||||||

|

1 2 3 4 |

5 6 7 |

8 |

9 10 11 12 |

13 14 |

15 16 17 18 19 20 |

21 |

|||||||||||

|

1,3,5,7,9,11,13,15,17,19,21 сумма нечетна |

|

|

|

|

Ошибка |

|

|

||||||||||

|

|

|

|

|

|

|||||||||||||

|

2,3,6,7,10,11,14,15,18,19 |

сумма четна |

|

|

|

|

|

|

|

|

|

|

||||||

|

4,5,6,7,12,13,14,15,20,21 |

сумма нечетна |

|

|

|

Ошибка |

|

|

||||||||||

|

|

|

|

|

|

|||||||||||||

|

8,9,10,11,12,13,14,15 сумма четна |

|

|

|

|

|

|

|

|

|

|

|

||||||

|

16,17,18,19,20,21 сумма четна |

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Бит 5 – содержит ошибку

Кэш-память

Технологически можно построить память, размещаемую прямо на микросхему процессора, однако это экономически не оправдано, а так же есть ограничения на размеры процессора.

Поэтому используют маленькую память с большой скоростью работы (кэш-память) и большую память с невысокой скоростью работы.

17

ОЗУ

Поскольку динамическому ОЗУ нужен только 1 транзистор и 1 конденсатор на бит (статическому ОЗУ требуется в лучшем случае 6 транзисторов на бит), динамическое ОЗУ имеет очень высокую плотность записи (много битов на одну микросхему). По этой причине основная память почти всегда строится на основе динамических ОЗУ.

Однако динамические ОЗУ работают очень медленно (время доступа занимает десятки наносекунд). Таким образом, сочетание кэш-памяти на основе статического ОЗУ и основной памяти на основе динамического ОЗУ соединяет в себе преимущества обоих устройств.

18

Оперативная память

Множество поколений интерфейсной логики, соединяющей ядро памяти с "внешним миром", сменилось за это время. Эволюция носила ярко выраженный преемственный характер - каждое новое поколение памяти практически полностью наследовало архитектуру предыдущего, включая, в том числе, и свойственные ему ограничения.

Ядро памяти (за исключением совершенствования проектных норм таких, например, как степень интеграции) не претерпело никаких принципиальных изменений.

19

FPM DRAM (Fast Page Mode DRAM)

Самыйбыстраядревний тип,страничнаякоторый все еще используетсяпамять— FPM. Основным отличием стала поддержка сокращенных

адресов. Если очередная запрашиваемая ячейка находится в той же самой строке, что и предыдущая, ее адрес однозначно определяется одним лишь номером столбца и передача номера строки уже не требуется.

При последовательном чтении ячеек памяти, (равно как и обработке компактных одно-двух килобайтовых структур данных), время доступа сокращается на 40%, а то и больше, ведь обрабатываемая строка находится во внутреннем буфере микросхемы, и обращаться к матрице памяти нет никакой необходимости.

20

EDO-DRAM (Extended Data Out)

память с усовершенствованным выходом

FPM постепенно замещается EDO, которая позволяет обращаться к памяти еще до того, как закончилось предыдущее обращение.

Такой конвейерный режим не ускоряет доступ к памяти, но зато увеличивает пропускную способность, выдавая больше слов в секунду.

21