- •Предмет и задачи дисциплины

- •1 Электронные системы.Назначение, структурная схема и порядок функционирования систем управления технологическими процессами.

- •Структура

- •Структуризация системы

- •2 Информация и сигнал

- •2.1 Определения

- •2.2 Сигналы

- •2.3 Классификация сигналов На рисунке 3 представлена структура….

- •2.4 Формы представления детерминированных сигналов

- •2.5 Дискретизация непрерывных сигналов

- •2.6 Равномерная дискретизация. Теорема Котельникова

- •2.7 Ряды Фурье

- •2.8 Интегрирование по частям

- •Дискретное преобразование Фурье (дпф)

- •3. Системы сбора и распределения данных

- •Здесь dс – стробируемый импульсом спроса дешифратора адреса на n входов и выходов. Стробирующий импульс опроса необходим:

- •Цифроаналоговые преобразователи

- •Аналогоцифровые преобразователи

- •Техника датчиков

- •1. Понятие датчика

- •2. Специфика современных требований

- •3. Принцип действия и классификация

- •4. Основные виды

- •5. Перспективы развития

Аналогоцифровые преобразователи

АЦП с двоично-взвешенным приближением.

Рисунок 19 - АЦП с двоично-взвешенным приближением.

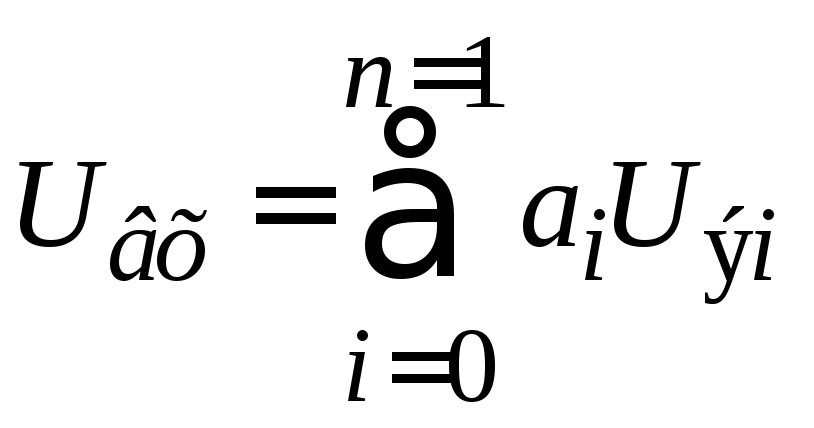

Выходное напряжение

поступает на один из выходов компаратора,

на другой вход подается

![]() .

При сравнении этих напряжений компаратор

вырабатывает команды, которые подаются

на управляющие устройство УУ. Оно состоит

изn-разрядного

регистра

.

При сравнении этих напряжений компаратор

вырабатывает команды, которые подаются

на управляющие устройство УУ. Оно состоит

изn-разрядного

регистра

![]() и триггеров

и триггеров![]() со схемами И. выходные сигналы УУ

управляют работой ЦАП.

со схемами И. выходные сигналы УУ

управляют работой ЦАП.

При поступлении

импульса запуска триггер старшего

разряда

![]() устанавливается в состояние 1, а все

остальные – в состояние 0. В первом такте

работы АЦП компаратор сравнивает

устанавливается в состояние 1, а все

остальные – в состояние 0. В первом такте

работы АЦП компаратор сравнивает![]() с эталонным напряжением

с эталонным напряжением![]() ,

которое подается из ЦАП и соответствует

единицы его старшего разряда.

,

которое подается из ЦАП и соответствует

единицы его старшего разряда.

Если

![]() ,

то на выходе компаратора нет импульса

и в старшем разряде ЦАП (в триггере

,

то на выходе компаратора нет импульса

и в старшем разряде ЦАП (в триггере![]() )

сохранится 1. Если

)

сохранится 1. Если![]() ,

то компаратор выдает импульс. Импульс

проходит через схему

,

то компаратор выдает импульс. Импульс

проходит через схему![]() и устанавливает триггер

и устанавливает триггер![]() в состояние 0. Одновременно происходит

сдвиг в регистре

в состояние 0. Одновременно происходит

сдвиг в регистре![]() и единица переходит в

и единица переходит в![]() разряд. Это обеспечит подачу эталонного

напряжения с ЦАП на компаратор. Аналогично

выполняются и все остальные такты работы

АЦП. Заn

тактов происходит уравновешивание

разряд. Это обеспечит подачу эталонного

напряжения с ЦАП на компаратор. Аналогично

выполняются и все остальные такты работы

АЦП. Заn

тактов происходит уравновешивание

![]() суммой эталонных напряжений, снимаемых

с ЦАП

суммой эталонных напряжений, снимаемых

с ЦАП

.

.

Временная диаграмма работы пятиразрядного АЦП приведена на рисунке 20.

Рисунок 20

Здесь преобразуемому

напряжению соответствует код 11011. По

сравнению с АЦП единичного приближения

преобразователь производит преобразование

за n шагов

вместо

![]() .

Получаем выигрыш в быстродействии.

Статистическая погрешность и быстродействие

определяются параметрами ЦАП и

компаратора.

.

Получаем выигрыш в быстродействии.

Статистическая погрешность и быстродействие

определяются параметрами ЦАП и

компаратора.

Аналогово-цифровые множители. Схема и прядок функционирования.

Аналоговые перемножители предназначены для перемножения двух аналоговых величин. Могут использоваться для построения умножителей частоты, фазовых детекторов, модуляторов, в системах автоматического регулирования. Они могут выполнять умножение, деление, извлечения корней и выделение тригонометрической функции. Важные параметры: диапазоны входных и выходных напряжений, коэффициенты подавления синфазных сигналов по входам, диапазонов, частот обрабатываемых сигналов. Электрическая схема состоит из множительного узла, преобразователя напряжения Y-канала, входного эмиттерного повторителя Х-канала и схемы стабилизации режима по постоянному току.

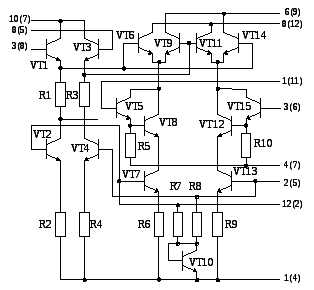

Рисунок 21

Множительный узел

выполнен на 2-х дифференциальных парах

транзисторов: VT6, VT9 и VT11, VT14. Базы

транзисторних

пар соединены

параллельно, а коллекторы – перекрестно,

поэтому разность выходных токов схемы

пропорциональна разности базовых токов

![]() (на каналХ)

и разности эммитерных

(на каналХ)

и разности эммитерных

![]() (на каналY)

(на каналY)

![]() .

Дифференциальный усилитель выполнен

на транзисторах VT5, VT8 и VT12, VT15 и преобразует

входное напряжение в разность токов

эмиттеров узла перемножения. Токи

транзисторов VT7, VT13 зафиксированы,

разность этих токов

.

Дифференциальный усилитель выполнен

на транзисторах VT5, VT8 и VT12, VT15 и преобразует

входное напряжение в разность токов

эмиттеров узла перемножения. Токи

транзисторов VT7, VT13 зафиксированы,

разность этих токов

.

.

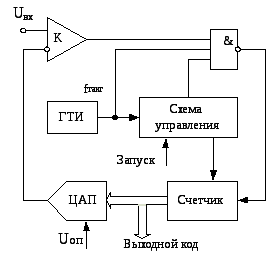

АЦП с единичным приближением. Схема и порядок функционирования.

Этот преобразователь типичным примером последовательных АЦП с единичными приближениями и состоит из компаратора, счетчика и ЦАП (см. рисунок 22). На один вход компаратора поступает входной сигнал, а на другой – сигнал обратной связи с ЦАП.

Рисунок 22

Работа преобразователя

начинается с прихода импульса запуска

который включает счетчик, суммирующий

число импульсов, поступающих от генератора

тактовых импульсов ГТИ. Выходной код

счетчика подается на ЦАП, осуществляющий

его преобразование в напряжение обратной

связи

![]() .

.

Рисунок 23

Процесс преобразования продолжается до тех пор, пока напряжение обратной связи сравняется со входным напряжением и переключится компаратор, который своим выходным сигналом прекратит поступление тактовых импульсов на счетчик. Переход выхода компаратора из 1 в 0 означает завершение процесса преобразования. Выходной код, пропорциональный входному напряжению в момент окончания преобразования, считывается с выхода счетчика.

Время преобразования

АЦП этого типа является переменным и

определяется входным напряжением. Его

максимальное значение соответствует

максимальному входному напряжению и

при разрядности двоичного счетчика N и

частоте тактовых импульсов

![]() равно

равно

![]() .

.

Статистическая погрешность преобразования определяется суммарной статистической погрешностью используемых ЦАП и компаратора.

При работе без устройства выборки-хранения апертурное время совпадает с временем преобразования. Как следствие, результат преобразования зависит от пульсации в входного напряжения. При наличии высокочастотных пульсаций среднее значение выходного кода нелинейно зависит от среднего значения входного напряжения. Это означает, что АЦП данного типа без устройства выборки-хранения пригодны для работы с постоянными или медленно изменяющимися напряжениями, которые за время преобразования изменяются не более, чем на значение кванта преобразования.

АЦП последовательного приближения. Схема и порядок функционирования.

Преобразователь

этого типа, называемые также АЦП с

поразрядным уравновешиванием, является

наиболее распространенным вариантом

последовательных АЦП. В основе работы

этого класса преобразователей лежит

принцип последовательного сравнения

измеряемой величины с

![]() ,

,![]() ,

,![]() и т.д. от возможного максимального

значения ее. Это позволяет выполнить

весь процесс преобразованияN

последовательных шагов вместо

и т.д. от возможного максимального

значения ее. Это позволяет выполнить

весь процесс преобразованияN

последовательных шагов вместо

![]() и получить выигрыш в быстродействии.

Статическая погрешность этого типа

преобразователей, может быть очень

малой.

и получить выигрыш в быстродействии.

Статическая погрешность этого типа

преобразователей, может быть очень

малой.

Принципы построения и работы АЦП последовательного приближения состоит из трех основных узлов: компаратора, регистра последовательного приближения (РПП) и ЦАП.

Рисунок 24

После подачи команды «Пуск» с приходом первого тактового импульса РПП задает на входе ЦАП код, равный половине его шкалы.

Напряжение обратной

связи

![]() на выходе ЦАП

на выходе ЦАП![]() ,

где

,

где![]() - квант выходного напряжения ЦАП. Если

входное напряжение больше, чем эта

величина, то на выходе компаратора

устанавливается 1, если меньше, то 0. В

этом случае схема управления должна

переключить старший разряд

- квант выходного напряжения ЦАП. Если

входное напряжение больше, чем эта

величина, то на выходе компаратора

устанавливается 1, если меньше, то 0. В

этом случае схема управления должна

переключить старший разряд![]() обратно в состояния нуля.

обратно в состояния нуля.

Остаток

![]() сравнивается с ближайшим младшим

разрядом и т.д. После четырех выравнивающих

шагов в регистре последовательного

приближения оказывается двоичное число,

из которого после цифро-аналогового

преобразования получается напряжение,

соответствующее

сравнивается с ближайшим младшим

разрядом и т.д. После четырех выравнивающих

шагов в регистре последовательного

приближения оказывается двоичное число,

из которого после цифро-аналогового

преобразования получается напряжение,

соответствующее![]() с точностью до 1 ЕМР. Выходное число

может быть считано с РПП в виде

параллельного двоичного кода поN

линиями.

с точностью до 1 ЕМР. Выходное число

может быть считано с РПП в виде

параллельного двоичного кода поN

линиями.

Быстродействие АЦП:

1. Определяется

временем установления

![]() ЦАП установившегося значения с

погрешностью, превышающей 0,5 ЕМР.

ЦАП установившегося значения с

погрешностью, превышающей 0,5 ЕМР.

2. Временем

переключения компаратора

![]() и задержки распространения сигнала в

регистре последовательного приближения

и задержки распространения сигнала в

регистре последовательного приближения![]() .

Сумма

.

Сумма![]() является величиной постоянной, а

является величиной постоянной, а![]() уменьшается с уменьшением веса разряда.

уменьшается с уменьшением веса разряда.

При работе без устройства выборки-хранения апертурное время зависит от входного сигнала, является переменным. Возникающие при этом апертурные погрешности носят нелинейный характер. Поэтому для эффективного использования АЦП последовательного приближения между его входом и источником преобразуемого сигнала следует включать УВХ. Большинство выпускаемых в настоящее время ИМС АЦП имеет встроенные устройства выборки-хранения или устройства слежения-хранения, управляемые сигналом запуска АЦП. Устройство слежения-хранения отличается тем, что постоянно находится в режиме выборки, переходя в режим хранения только на время преобразования сигнала. Данный класс АЦП занимает промежуточное положение по быстродействию, стоимости и разрешающей способности между последовательно-параллельными интегрирующими АЦП и находят широкое применение в системах управления, контроля и цифровой обработки сигналов.

Следящие АЦП. Схема и порядок функционирования

Рисунок 25 - Схема последовательного АЦП с единичным приближением

Схему можно легко

превратить в АЦП следящего типа. Для

этого нужно суммирующий счетчик заменит

на реверсивный и использовать прямой

и реверсивный выходы компаратора для

управления импульсом. В этом случае

![]() ,

выходной код АЦП колеблется вокруг

среднего положения с точностью до

единицы младшего разряда (ЕМР).

,

выходной код АЦП колеблется вокруг

среднего положения с точностью до

единицы младшего разряда (ЕМР).

Рисунок 26

А это есть в любой

дискретной следящей системе. Если в

состоянии динамического равновесия

![]() начинает изменяться, то выходной код

АЦП отслеживает его с погрешностью

равной ЕМР. Но должно выполняться

условие, что за период счетных импульсов

начинает изменяться, то выходной код

АЦП отслеживает его с погрешностью

равной ЕМР. Но должно выполняться

условие, что за период счетных импульсов![]() входной сигнал изменится не более чем

на значение шага квантования

входной сигнал изменится не более чем

на значение шага квантования![]() ,

т.е.

,

т.е.![]() .

.

АЦП двухтактного интегрирования. Схема, порядок функционирования и временная диаграмма работы

Упрощенная схема АЦП (двухтактного интегрирования), приведена на рисунке 27.

Рисунок 27 – Упрощенная схема АЦП двухтактного интегрирования

Преобразование

проходит две стадии: стадию интегрирования

и стадию счета. В начале первой стадии

ключ

![]() замкнут, а ключ

замкнут, а ключ![]() разомкнут. Интегратор И интегрирует

напряжение

разомкнут. Интегратор И интегрирует

напряжение![]() .

Время интегрирования входного напряжения

.

Время интегрирования входного напряжения![]() постоянно, в качестве таймера используется

счетчик с коэффициентом пересчета

постоянно, в качестве таймера используется

счетчик с коэффициентом пересчета![]() ,

так что

,

так что![]() к моменту окончания интегрирования

выходное напряжение интегратора

составляет

к моменту окончания интегрирования

выходное напряжение интегратора

составляет

,

,

где

![]() - среднее за время

- среднее за время![]() входное напряжение. После окончания

стадии интегрирования ключ

входное напряжение. После окончания

стадии интегрирования ключ![]() размыкается, а ключ

размыкается, а ключ![]() замыкается, и опорное напряжение

замыкается, и опорное напряжение![]() поступает на вход интегратора. При этом

выбирается опорное напряжение,

противоположное по знаку входному

напряжению. На стадии счета выходное

напряжение интегратора линейно

уменьшается по абсолютной величине,

как показано на рисунке 28.

поступает на вход интегратора. При этом

выбирается опорное напряжение,

противоположное по знаку входному

напряжению. На стадии счета выходное

напряжение интегратора линейно

уменьшается по абсолютной величине,

как показано на рисунке 28.

Рисунок 28 – Временная диаграмма АЦП двухтактного интегрирования

Стадия счета заканчивается, когда выходное напряжение интегратора переходит через нуль. При этом компаратора К переключается и счет останавливается. Интервал времени, в котором проходит стадия счета, определяется уравнением

.

.

Содержимое счетчика после окончания стадии счета

![]() .

.

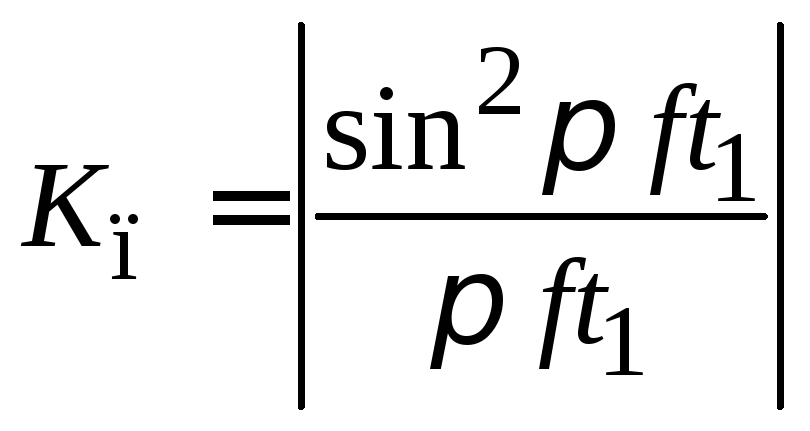

Из этой формулы

следует, что отличительной особенностью

метода многотактного интегрирования

является то, что ни тактовая частота,

постоянная интегрирования RC не влияют

на результат. Необходимо, чтобы тактовая

частота в течении времени

![]() оставалась постоянной. Это можно

обеспечить при использовании простого

тактового генератора. Коэффициент

передачи помехи

оставалась постоянной. Это можно

обеспечить при использовании простого

тактового генератора. Коэффициент

передачи помехи![]() для АЦП двухтактного интегрирования

для АЦП двухтактного интегрирования

.

.

Следует, что

переменное напряжение, период которого

в цело число раз меньше

![]() ,

подавляется совершенно. Необходимо

выбрать тактовую частоту такой, чтобы

произведение

,

подавляется совершенно. Необходимо

выбрать тактовую частоту такой, чтобы

произведение![]() было бы равным, или кратным периоду

напряжения промышленной сети.

было бы равным, или кратным периоду

напряжения промышленной сети.

Принципы подавления помех в интегрирующих АЦП

Статическая точность АЦП интегрирования определяется только точностью источника опорного напряжения и смещением нуля интегратора и компаратора, которые суммируются с опорным напряжением. Смещения нуля можно устранить автоматической компенсацией. Для этого в цикле преобразования вводят дополнительную стадию установки нуля, во время которой интегратор отключается от источников сигналов и совместно с компаратором охватывается глубокой отрицательной обратной связью, это показано на рисунке 29.

Рисунок 29 – АЦП двухтактного интегрирования с автоматической компенсацией смещения нуля

Здесь в качестве

компаратора используется ОУ. Между

интегратором и входом АЦП включен

неинвертирующий повторитель в качестве

буферного усилителя Б. в фазе автоматической

компенсации нуля ключи

![]() ,

,![]() ,

,![]() разомкнуты, ключи

разомкнуты, ключи![]() ,

,![]() ,

,![]() ,

,![]() - замкнуты.

- замкнуты.

Интегратор,

компаратор и буферный усилитель образует

повторитель напряжения, выходное

напряжение которого

![]() ,

подается на конденсатор автоматической

компенсации

,

подается на конденсатор автоматической

компенсации![]() буферного усилителя равно нулю, а

выходное – его смещению нуля

буферного усилителя равно нулю, а

выходное – его смещению нуля![]() .

.

После окончания

переходных процессов на конденсаторе

![]() установится напряжение равное

установится напряжение равное

![]() ,

,

где

![]() - напряжение нуля интегратора.

- напряжение нуля интегратора.

Одновременно

конденсатор

![]() заряжается от источника опорного

напряжения.

заряжается от источника опорного

напряжения.

На стадии

интегрирования входного напряжения

ключи

![]() и

и![]() размыкаются, а

размыкаются, а![]() - замыкается. На это время напряжение

на конденсаторе

- замыкается. На это время напряжение

на конденсаторе![]() запоминается, смещение нуля в течении

фазы интегрирования компенсируется.

При этом дрейф нуля определяется только

кратковременной нестабильностью,

которая очень мала. То же самое сохраняется

на стадии счета.

запоминается, смещение нуля в течении

фазы интегрирования компенсируется.

При этом дрейф нуля определяется только

кратковременной нестабильностью,

которая очень мала. То же самое сохраняется

на стадии счета.

В контуре компенсации

смещение нуля последовательно включены

два усилителя, то легко могут возникнуть

автоколебания. Для стабилизации

последовательно с ключом

![]() следует включить резистор.

следует включить резистор.

После окончания

фазы интегрирования схема управления

анализирует выходное напряжение

компаратора. Если среднее значение

входного напряжения положительно, то

на выходе компаратора устанавливается

напряжение высокого уровня. В этом

случае одновременно с размыканием ключа

![]() замыкаются ключи

замыкаются ключи![]() и

и![]() ,

подключая ко входу буферного усилителя

конденсатор

,

подключая ко входу буферного усилителя

конденсатор![]() с сохраненным на нем опорным напряжением,

так, что это напряжение имеет полярность

противоположную полярности источника

опорного напряжения. Если среднее

значение входного напряжения отрицательно,

то на выходе компаратора устанавливается

напряжение низкого уровня. Тогда

замыкаются ключи

с сохраненным на нем опорным напряжением,

так, что это напряжение имеет полярность

противоположную полярности источника

опорного напряжения. Если среднее

значение входного напряжения отрицательно,

то на выходе компаратора устанавливается

напряжение низкого уровня. Тогда

замыкаются ключи![]() и

и![]() ,

подключая ко входу буферного усилителя

опорный другими полюсам. В обеих случаях

в стадии счета происходит изменение

напряжения интегратора

,

подключая ко входу буферного усилителя

опорный другими полюсам. В обеих случаях

в стадии счета происходит изменение

напряжения интегратора![]() в направлении, противоположном тому,

которое имело место в стадии интегрирования.

в направлении, противоположном тому,

которое имело место в стадии интегрирования.

Принципы построения параллельных АЦП и их сравнительная оценка

Результаты АЦ–преобразования записываются, как правило, в запоминающее устройства, существует вероятность получить неверную величину. Решить эту проблему можно, например, с помощью устройства выборки-хранения (УВХ). Некоторые интегральные микросхемы параллельных АЦП, например, МАХ 100, снабжаются сверхскоростными УВХ, имеющими время выборки порядка 0,1 нс. Другой путь состоит в использовании кода Грея, особенностью которого является изменение только одной кодовой позиции при переходе от одного кодового значения к другому. В некоторых АЦП, например МАХ1151, для снижения вероятности сбоев при параллельном АЦ- преобразовании используется двухтактный цикл. Как видно из таблицы 1, при увеличение входного сигнала компараторы устанавливаются в состояние 1 по очереди – снизу вверх.

Таблица 1

|

Входное напряжение |

Состояние компараторов |

Выходы | ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

2 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

|

3 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

|

4 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

|

5 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

|

6 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

|

7 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

Такая очередность не гарантируется при быстром нарастании входного сигнала. Приоритетное кодирование позволяет избежать ошибки благодаря тому, что единицы в младших разрядах не принимаются во внимание приоритетным шифратором. Благодаря одновременной работе компараторов параллельный АЦП является самым быстрым. Недостатком этой схемы является высокая сложность.

Конвейерная архитектура позволяет существенно (в несколько раз) повысить максимальную частоту выборок многоступенчатого АЦП. За счет этого можно без проигрыша в быстродействии увеличить число ступеней АЦП, понизив разрядность каждой ступени. Увеличение числа ступеней преобразования уменьшает сложность АЦП.

Конвейерную архитектуру имеет большое количество выпускаемых в настоящее время многоступенчатых АЦП: двухступенчатый 10-разрядный АД9040А выполняющий до 40 млн. преобразований в секунду (МПс); четырехступенчатый 12-разрядный АД9220 (10МПс), потребляющий всего 250мВт.

При выборе конвейерного АЦП следует иметь в виду, что многие из них не допускают работу с низкой частотой выборок.

Параллельные АЦП. Схемы и порядок функционирования

Параллельные АЦП – осуществляют квантование сигнала одновременно с помощью набора компараторов, включенных параллельно источнику входного сигнала. На рисунке 30 показана реализация параллельного метода АЦ-преобразования для 3-разрядного числа.

Рисунок 30

C помощью трех двоичных разрядов можно представить восемь различных чисел, включая нуль. Необходимо, следовательно, семь компараторов. Семь соответствующих опорных напряжений образуются с помощью резистивного делителя.

Если приложенное

входное напряжение не выходит за пределы

диапазона от

![]() h

до

h

до

![]() h,

где

h,

где

![]() - квант входного напряжения, соответствующий

единице младшего разряда АЦП, то

компараторы с 1-го по 3-ий устанавливаются

в состояние 1, а компараторы с 4-го по

7-ий устанавливаются в состояние 0.

Преобразование этой группы кодов в

трехзначное двоичное число выполняет

логическое устройство называемое

приоритетным шифратором, диаграмма

состояний которого приведена в таблице

2.

- квант входного напряжения, соответствующий

единице младшего разряда АЦП, то

компараторы с 1-го по 3-ий устанавливаются

в состояние 1, а компараторы с 4-го по

7-ий устанавливаются в состояние 0.

Преобразование этой группы кодов в

трехзначное двоичное число выполняет

логическое устройство называемое

приоритетным шифратором, диаграмма

состояний которого приведена в таблице

2.

Таблица 2.

|

Входное напряжение |

Состояние компараторов |

Выходы | ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

2 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

|

3 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

|

4 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

|

5 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

|

6 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

|

7 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

Подключение приоритетного шифратора непосредственно к выходу АЦП может привести к ошибочному результату при считывании выходного кода и получить неверную величину. Рассмотрим, например, переход от трех к четырем, или в двоичном коде от 011 к 100. Если старший разряд вследствие меньшего времени задержки изменит свое состояние раньше других разрядов, то временно на выходе возникнет число 111, т.е. семь. Величина ошибки в этом случае составит половину измеряемого диапазона.

Параллельно-последовательные АЦП. Принципы построения и функционирования

Это АЦП позволяют снизить затраты на аппаратуры и увеличить быстродействие для реализации шестиразрядного АЦП. В схеме используются два трехразрядных параллельных АЦП.

Рисунок 31

Первый из них

вырабатывает три старших разряда

выходного кода. Они представляют собой

грубо квантованное значение

![]() усилить в 8 раз можно использовать два

АЦП с одним и тем же диапазоном входного

напряжения. В этом случае точность в

АЦП должна быть такой же как у

шестиразрядного АЦП. Иначе разность

между грубо квантованным значением и

входным напряжением

усилить в 8 раз можно использовать два

АЦП с одним и тем же диапазоном входного

напряжения. В этом случае точность в

АЦП должна быть такой же как у

шестиразрядного АЦП. Иначе разность

между грубо квантованным значением и

входным напряжением![]() не будет иметь смысла.

не будет иметь смысла.

При разработке параллельно-последовательных АЦП появляется задача выбора структуры и согласования шкал отдельных ступеней АЦП.

АЦП с промежуточным преобразованием во временной интервал. Схема и порядок функционирования

Рисунок 32

Схема с промежуточным

преобразованием входного сигнала в

пропорциональный ему временной интервал

![]() ,

который заполняется счетными импульсами

эталонной частоты

,

который заполняется счетными импульсами

эталонной частоты![]() .

Число импульсов, попавших в измерительный

интервал

.

Число импульсов, попавших в измерительный

интервал![]() ,

фиксируется счетчиком и выдается как

цифровой эквивалент преобразуемого

сигнала.

,

фиксируется счетчиком и выдается как

цифровой эквивалент преобразуемого

сигнала.

Рисунок 33

При этом соотношения между кодом и входным сигналом имеет вид

![]()

![]() - скорость д.изменения

напряжения генератора пилообразного

напряжения (ГПН)

- скорость д.изменения

напряжения генератора пилообразного

напряжения (ГПН)

![]()

Статистическая

погрешность данной АЦП определяется

не стабильностью частоты

![]() ,

отклонением характеристики ГПН от

идеальной, погрешностью компараторов.

,

отклонением характеристики ГПН от

идеальной, погрешностью компараторов.

Динамическая погрешность данного АЦП аналогична АЦП со ступенчатым пилообразным напряжением. Для уменьшения динамической погрешности АЦП используют совместимо с УВХ.

АЦП с промежуточным преобразованием в частоту. Схема и принцип работы

Рисунок 34

При работе с УВХ

частоту работы АЦП можно довести до

![]() ,

,![]() - максимальное время преобразования.

- максимальное время преобразования.

![]() ,

,

![]() - период следования

счетных импульсов.

- период следования

счетных импульсов.

Рисунок 35

УВХ состоит из

накопительного конденсатора С (см. рис.

34), аналогового ключа Кл, операционного

усилителя ОУ. По сигналу с генератора

тактовых импульсов АЦП преобразует

сигнал

![]() ,

который представляет собой выходной

сигнал УВХ (в режиме хранения). По

окончании цикла преобразования

формируется управляющий сигнал. Он

действует на ключ Кл и переводит УВХ в

режим выборки (сложения). На временной

диаграмме (рис. 35) области А, В, С обозначают

время преобразования АЦП.

,

который представляет собой выходной

сигнал УВХ (в режиме хранения). По

окончании цикла преобразования

формируется управляющий сигнал. Он

действует на ключ Кл и переводит УВХ в

режим выборки (сложения). На временной

диаграмме (рис. 35) области А, В, С обозначают

время преобразования АЦП.

Сравнительная оценка схем построения АЦП

Аналогово-цифровые преобразователи (АЦП) являются устройствами, которые принимают входные аналоговые сигналы и генерируют соответствующие им цифровые сигналы, пригодные для обработки микропроцессорами и другими цифровыми устройствами.

Рисунок 36 - Классификация АЦП

К последовательным АЦП относятся: на уравновешивании входного аналогового значения суммой минимальных (для данного преобразователя) по весу эталонов (квантов). Уравновешивание входного аналогового значения осуществляется суммой n-эталонов (n – число разрядов АЦП), взвешенных по двоичному закону. С промежуточным преобразованием входного аналогового значения в интервал времени или частоту, с последующим преобразованием в цифровой код. Отнести преобразователи напряжения –частоты, т.е. частота повторения выходных импульсов таких АЦП пропорциональна входному аналоговому значению, использующие в процессе преобразования операцию интегрирования входного аналогового сигнала за фиксированный интервал времени.

Параллельные АЦП

основаны на использовании

![]() -

эталонов с весами, отличающимися на

один квант. Сравнение входного аналогового

значения с каждым эталоном производится

одновременно с помощью

-

эталонов с весами, отличающимися на

один квант. Сравнение входного аналогового

значения с каждым эталоном производится

одновременно с помощью![]() схем сравнения (компараторов).

схем сравнения (компараторов).

Последовательно-параллельные АЦП разделяют на многоступенчатые, в которых принимают несколько параллельных АЦП, работающих последовательно несколько раз с соответствующим управлением пороговыми напряжениями.

Аналоговые микропроцессоры. Структурная схема и порядок функционирования

Микропроцессор (МП) – это программно-управляемое цифровое устройство обработки информации, выполненное в виде одной или нескольких интегральных микросхем.

Два вида МП: разрядно- модульный и одно кристальный. Структурная схема разрядно-модульного МП представлена на рис. 37.

Рисунок 37 –

Микропроцессор состоит из двух блоков центрального процессора ЦП и блока управления БУ. БУ состоит из модуля памяти микро-команд ПМК и контроллера микропрограммного управления КМУ. Размещение ПМК в отдельном сменном модуле дает возможность менять набор микропрограмм код команды КК поступает на входы КМУ, там формируется необходимая последовательность адресов микрокоманд АМК. Микрокоманда МК с ПМК поступает на входы ЦП. После выполнения микрооперации ЦП выдает в КМУ признаки результата П, которые влияют на формирование следующего АМК. Признаки результата фиксируются в КМУ и учитываются при выполнении следующих МК.

Потом КМУ формирует адрес следующей команды, поступающей в память. Разрядно-модульные МП имеют большую гибкость и быстродействие по сравнению с однокристальным. В однокристальных МП БУ размещается на одном кристалле с ЦП. Схема БУ здесь намного сложнее.

Устройство выборки-хранения. Назначение, принципы построения и работы

Для уменьшения динамической погрешности АЦП используются устройства выборки и хранения (УВХ). Оно включается между входом АЦП и выходом источника аналогового сигнала.

Работа УВХ –

фиксировать мгновенное значение

изменяющегося во времени входного

сигнала

![]() на время, необходимое для следующего

преобразования в АЦП. УВХ имеет 2

устойчивых режима работы: выборки и

хранения. В режиме выборки выходной

сигнал УВХ с максимально возможной

скоростью достигает значения преобразуемого

сигнала

на время, необходимое для следующего

преобразования в АЦП. УВХ имеет 2

устойчивых режима работы: выборки и

хранения. В режиме выборки выходной

сигнал УВХ с максимально возможной

скоростью достигает значения преобразуемого

сигнала![]() и отслеживает его до тех пор, пока не

появится команда «хранение.». С этого

момента УВХ будет хранить на выходе

мгновенное значение преобразуемого

входного сигнала.

и отслеживает его до тех пор, пока не

появится команда «хранение.». С этого

момента УВХ будет хранить на выходе

мгновенное значение преобразуемого

входного сигнала.

В УВХ входят: ОУ, которые выполняют роль буферов между входом АЦП и запоминающим элементом, ключи, которые обеспечивают переход схемы из режима хранения.

Датчики информации СУ