- •2. Архитектура микроконтроллеров семейства 8051

- •2.1. Общие сведения

- •2.2. Структурная схема микроконтроллера

- •2.3. Процессорное ядро

- •2.4. Организация памяти

- •2.5. Регистры специальных функций

- •2.6. Модуль системы прерываний

- •2.7. Модуль параллельных портов ввода-вывода

- •2.8. Модуль таймеров/счетчиков

- •2.9. Модуль универсального асинхронного приемопередатчика

- •2.10. Система команд микроконтроллеров семейства 8051

- •2.10.1. Общие сведения о системе команд

- •2.10.2. Описание команд

- •2.10.3. Методы адресации операндов

2.4. Организация памяти

Вся серия МК семейства 8051 имеет гарвардскую архитектуру с раздельными адресными пространствами памяти программ и данных. Физическое распределение памяти базового МК 8051 представлено на рис. 2.9.

|

|

|

Рис. 2.9. Организация памяти базового микроконтроллера 8051 |

CSEG (Code Segment) – пространство памяти программ, которое включает и резидентную и внешнюю память;

DSEG (Data Segment) – пространство внутренней памяти данных;

RSEG (Register Segment) – пространство регистров;

BSEG (Bite Segment) – пространство битовой памяти данных;

XSEG (eXternal Segment) – пространство внешней памяти данных.

Резидентная память программ CSEG, структура которой показана на рис. 2.10, представляет собой постоянное запоминающее устройство с байтовой организацией. Она доступна только для чтения и предназначена для хранения команд прикладной программы, констант, таблиц и т. п. Базовая модель МК 8051 имеет емкость РПП 4 Кбайт.

Рис. 2.10. Структура резидентной памяти программ |

Область нижних адресов памяти программ CSEG занята векторами прерываний, которые представляют собой 8-байтовые области памяти для каждого из пяти источников прерываний базовой модели МК. При запросе прерывания от одного из источников МК автоматически передает управление на начальный адрес соответствующего этому источнику вектора прерывания. По адресу вектора должна быть расположена либо подпрограмма обслуживания прерывания длиной не более 8 байт, либо, чаще всего, команда безусловной передачи управления на начальный адрес подпрограммы обслуживания прерывания в памяти программ.

В ряде новых моделей МК число источников прерывания увеличено. Естественно, что при этом расширяется и область векторов прерываний.

Первые три байта CSEG являются стартовым адресом, на который автоматически передается управление при включении питания или перезапуске МК. Они предназначены для записи команды безусловного перехода на первую команду прикладной программы.

Резидентная память данных DSEG, структура которой представлена на рис. 2.11, предназначена для хранения оперативных данных и переменных в процессе выполнения прикладной программы.

|

|

Побайтно адресуемая область ОЗУ | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

П

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Б назначения

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Рис. 2.11. Структура резидентной памяти данных | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Она адресуется одним байтом и имеет емкость 128 байт. Кроме того, к адресному пространству РПД примыкают адреса регистров специальных функций. В новых версиях МК семейства 8051 область РПД расширена до 256 байт. В этом случае верхняя область РПД с адресами 80H до 0FFH доступна только при косвенной адресации, а совпадающая с ней область регистров специальных функций доступна только при прямой адресации.

Младшие 32 байт РПД образуют подпространство регистровой памяти RSEG. Они сгруппированы в четыре банка регистров общего назначения, каждый из которых состоит из восьми регистров R0-R7. В любой момент времени программе доступен только один банк регистров, номер которого задается битами слова состояния программы PSW.

Следующие после последнего банка РОН 16 байт (адреса 20H…2FH) или 128 бит (адреса 00H…7FH) образуют подпространство битовой области BSEG, состоящей из ячеек памяти, к которым возможно побитовое обращение. Набор команд МК 8051 содержит значительное количество инструкций, позволяющих работать с указанными битами. Адрес прямо адресуемых битов может быть записан либо в виде абсолютного битового адреса из диапазона 00H…7FH, либо в виде <Адрес Байта>.<Разряд>. Например, запись 27.5 означает пятый разряд ячейки памяти с адресом 27H. Другое подпространство битовой области BSEG расположено в области регистров специальных функций, которая будет рассматриваться в следующем разделе.

Оставшееся адресное пространство РПД c адресами 30H…7FH является побайтно адресуемой областью. Обращение к ячейкам памяти данных возможно двумя способами. При первом способе, использующем режим прямой адресации, прямой физический адрес ячейки памяти является операндом соответствующей команды. Второй способ – косвенная адресация с помощью регистров R0 или R1: перед выполнением соответствующей команды в один из этих регистров должен быть занесен адрес ячейки памяти, к которой необходимо обратиться для получения операнда.

Резидентные сегменты памяти могут быть дополнены внешней памятью программ и данных. В этом случае общий максимально допустимый объем памяти может составлять 64 Кбайт для каждой области памяти. МК 8051 имеет 16-разрядную шину адреса, через которую обеспечивается доступ к внешней памяти программ и данных с помощью счетчика команд PC или регистра-указателя данных DPTR соответственно.

Внешняя память программ CSEG. Для подключения микросхемы ПЗУ, используемой в качестве внешней части области памяти программ CSEG, предназначены параллельные порты P0 и P2. При этом через выход порта P0 передается младший байт адреса команды, а выходы порта Р2 содержат старший байт адреса команды. Сигнал ALE используется для фиксации младшего байта адреса во внешнем регистре-защелке. Адресная информация достоверна в момент окончания сигнала ALE. Поскольку порт P0 используется и для передачи адреса, и для приема-передачи данных, то после фиксации адреса во внешнем регистре-защелке через порт P0 принимается байт очередной извлекаемой команды. Такой режим временного разделения передачи адреса и данных по одной шине называется мультиплексированием.

Строб чтения внешней памяти PSEN генерируется МК аппаратно только при обращении к ВПП и во время обращения к РПП не формируется.

Для включения внешней памяти программ в адресное пространство памяти программ CSEG используется внешний вывод EA. При подключении на этот вывод напряжения высокого уровня обеспечивается выборка кодов команд из адресного пространства ячеек с 0 по 4095 резидентной памяти программ и начиная с 4096 по 65 535 – выборка из внешней памяти программ. При использовании только резидентной памяти внешний вывод EA «заземляется».

Внешняя память данных XSEG. Память данных, так же как и память программ, может быть расширена до 64 Кбайт подключением внешних микросхем ОЗУ с использованием портов P0 и P2. При обращении к внешней области памяти XSEG на выходах P0 младший байт адреса внешней памяти мультиплексируется с вводимым или выводимым байтом данных. Выходы порта Р2 содержат старший байт адреса внешней памяти. В качестве сигналов, задающих режимы чтения и записи микросхемы запоминающего устройства внешней памяти, используются сигналы RD и WR, вырабатываемые аппаратно при обращении в прикладной программе к внешней памяти данных, а сигнал ALE служит для фиксации младшего байта адреса во внешнем регистре-защелке. Для обращения к внешней памяти данных XSEG используется только косвенная адресация с помощью 16-разрядного регистра-указателя данных DPTR или страничная адресация посредством регистров R0 и R1.

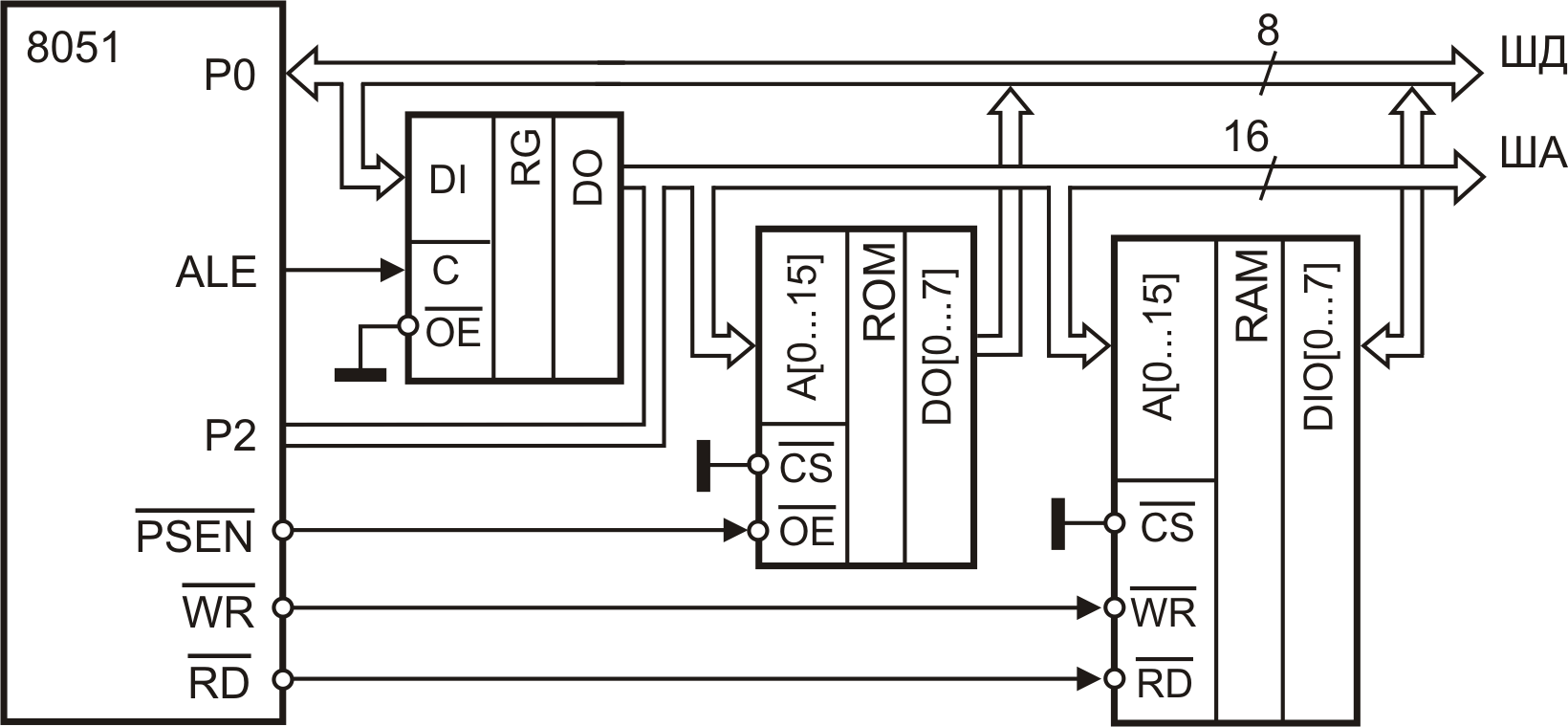

Схема подключения микросхем внешней памяти программ и данных приведена на рис. 2.12. Она содержит регистр-защелку RG для фиксации младшей части адреса, внешние микросхемы постоянного (ROM) и оперативного (RAM) запоминающих устройств. Младший байт адреса передается через порт P0 и по стробу ALE фиксируется в регистре-защелке RG. Вместе со старшим байтом, выдаваемым через порт Р2, он образует 16-разрядную шину адреса ША, через которую требуемый адрес передается на внешние микросхемы памяти. Разряды шины данных ШД формируется из линий порта Р0.

|

|

|

Рис. 2.12. Подключение внешней памяти программ и данных |

При низком уровне сигнала PSEN, который вырабатывается автоматически при обращении к внешней памяти программ и подается на вход разрешения чтения выходных данных OE (Output Enable) микросхемы ПЗУ, выполняется чтение команды из ROM, а при высоком выходы DO[7...0] (Data Output) отключаются. Низким уровнем сигнала WR производится запись байта с шины данных в RAM, а низким уровнем сигнала RD – чтение байта из RAM. При высоких уровнях сигналов записи WR и чтения RD выводы DIO[7...0] (Data Input/Output) внешнего ОЗУ отключаются. Данные из памяти программ читаются в регистр команд устройства управления и синхронизации, а память данных через регистры обменивается данными с операционным устройством.

бласть

программ

бласть

программ

обитно

адресуемая область ОЗУ

обитно

адресуемая область ОЗУ анки

регистров общего

анки

регистров общего