- •1.4. Типовые периферийные модули микроконтроллеров

- •1.4.1. Модули параллельных портов ввода-вывода

- •1.4.2. Модули таймеров/счетчиков и процессоров событий

- •1.4.3. Модули последовательного обмена

- •1.4.4. Модуль аналого-цифрового преобразователя

- •1.4.5. Модуль цифроаналогового преобразователя

- •1.4.6. Модуль аналогового компаратора

- •1.5. Система команд микроконтроллера

- •1.5.1. Формат команд

- •1.5.2. Система команд

- •1.5.2. Методы адресации

- •1.6. Разработка прикладных программ

1.4.3. Модули последовательного обмена

Прежде чем перейти к изучению модулей последовательного обмена, кратко рассмотрим общие сведения о принципах последовательной передачи данных, заложенные еще при внедрении в практику телеграфных аппаратов и телетайпов.

Как в параллельном, так и в последовательном способе передачи в качестве единицы передаваемой информации используется чаще всего один байт. Но в отличие от параллельного способа, при котором передача данных осуществляется порциями в один байт за единицу времени, при последовательном способе данные передаются порциями в один бит за единицу времени. Это приводит к необходимости использования различных способов выделения из принятой на стороне приемника непрерывной последовательности битов информационных байтов. Наиболее распространенные способы такого выделения основаны на применении синхронного и асинхронного принципов передачи данных.

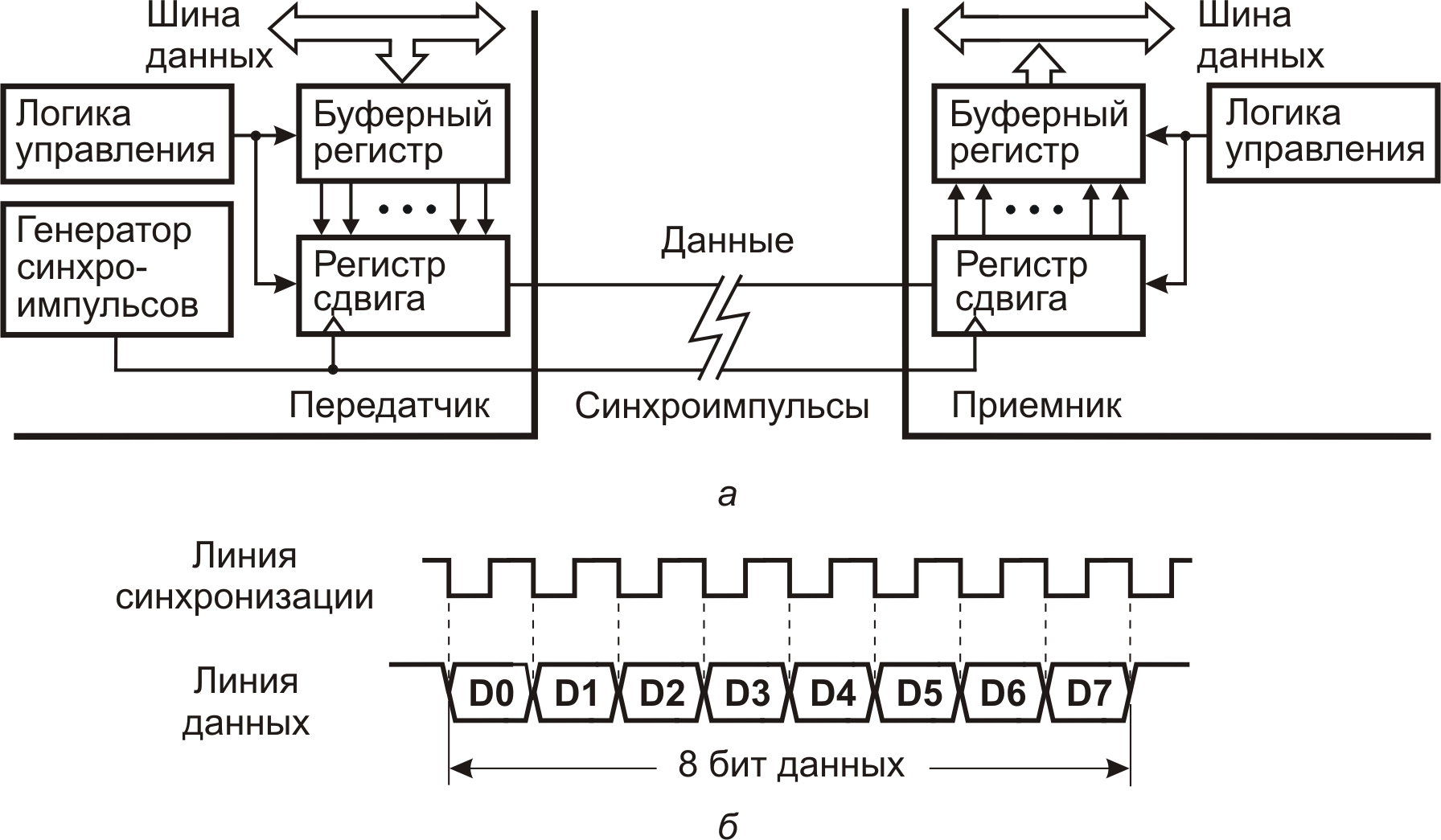

Синхронная передача данных. Этот способ передачи данных предполагает синхронизацию работы приемника и передатчика посредством включения тактовой информации в передаваемый сигнал или, чаще всего, путем использования общей для источника и приемника линии синхронизации, импульсы на которой служат для выделения индивидуальных битов в канале. Структура организации синхронной передачи данных показана на рис. 1.19, а.

Начало передачи инициируется занесением передаваемых данных в буферный регистр передатчика, затем передатчик загружает информацию в сдвиговый регистр с параллельной записью, запускает генератор синхроимпульсов и счетчик. С каждым синхронизирующим сигналом данные сдвигаются на одну позицию и поступают на линию данных. При этом каждый передаваемый бит данных сопровождается импульсом по линии синхронизации, информирующим приемник о наличии на линии данных информационного бита. Приемник состоит из регистра сдвига с последовательной записью, счетчика и логической схемы, которые управляются теми же синхросигналами. После того как счетчик зарегистрирует поступление необходимого количества синхросигналов (и, соответственно, бит данных), он инициирует параллельную передачу полученных данных из сдвигового регистра в буферный регистр приемника данных, откуда они могут быть считаны для дальнейшей обработки в прикладной программе. Временная диаграмма работы описанной системы приведена на рис. 1.19, б.

|

|

|

Рис. 1.19. Синхронная передача данных: а – структура; б – временная диаграмма |

Асинхронная передача данных. При асинхронной последовательной передаче, структура организации которой показана на рис. 1.20, а, между передатчиком и приемником нет линии синхронизации, импульсы на которой выделяли моменты передачи отдельных битов, и передача информационного слова может производиться асинхронно, в любой произвольный момент времени. Как же в таком случае приемник будет узнавать о моментах начала и завершения передачи битов данных и отделять друг от друга принимаемые слова? Стандартное решение проблемы заключается в следующем.

Во-первых, должна обеспечиваться одинаковая скорость работы приемника и передатчика, иначе пришедшие биты данных приемник будет либо пропускать, либо принимать повторно. Для задания скорости передачи и приема каждый передаваемый и принимаемый бит стробируется, то есть обрабатывается синхронно со специальным сигналом – стробом. Стробы формируются автономными генераторами стробов, имеющимися как в передатчике, так и в приемнике и обеспечивающими возможность задания одинаковых скоростей обмена. Для асинхронного режима принят следующий ряд стандартных скоростей обмена: 50, 75, 110, 150, 300, 600, 1200, 2400, 4800, 9600, 19 200, 38 400, 57 600 и 115 200 бит/с.

Во-вторых, для выделения начала и конца пересылаемого информационного слова его обрамляют стартовым (старт-бит) и стоповым (стоп-бит) битами. Промежутки времени от начала стартового бита до конца стопового бита одной посылки называются информационными кадрами.

|

|

|

Рис. 1.20. Асинхронная передача данных: а – структура; б, в – временные диаграммы кадров |

Информационные кадры асинхронной последовательной передачи данных могут иметь различные форматы. Наиболее распространенные форматы кадров содержат 8 бит пересылаемой информации и 2 или 3 дополнительных бита: старт-бит, всегда равный 0; стоп-бит, всегда равный 1 и бит контроля четности. В бит контроля четности заносят признак четного или нечетного количества единичных битов в передаваемом слове. На принимающей стороне проводится анализ этого бита, и если бит четности не соответствует числу полученных единичных битов, то принятый кадр считается недостоверным и пересылается заново. На рис. 1.20, б и 1.20, в показаны временные диаграммы 10- и 11-битовых кадров.

С учетом использования описанных форматов кадра процедура асинхронного последовательного обмена реализуется следующим образом. В отсутствие передачи на линии всегда обеспечивается уровень сигнала, соответствующий логической 1. Передача каждого кадра начинается посылкой стартового бита (изменением значения сигнала в линии из 1 в 0 на один период стробирующих сигналов). Сразу после этого начинают передаваться биты данных, по одному за период стробирования, начиная с младшего бита. Если в процессе обмена производится контроль по четности, то затем передается бит четности. В завершение посылается стоп-бит и линия данных в течение одного такта находится в состоянии простоя. Это необходимо для приведения приемника в исходное состояние перед передачей нового элемента данных. Старт-бит следующего кадра посылается в любой момент после стоп-бита, то есть между передачами возможны паузы произвольной длительности.

Прием начинается с фиксации старт-бита, передний фронт которого используется в приемнике как признак начала кадра и как начало отсчета времени для определения моментов прихода отдельных битов в кадре. Затем приемник начинает процедуру приема и подсчета принимаемых битов, причем для получения достоверных значений битов в период стробирования производится несколько считываний состояния линии и решение принимается по мажоритарному принципу, например при трехкратном считывании – два из трех. Процедура завершается с приходом стоп-бита занесением результата в буферный регистр приемника.

При обмене данных по последовательному каналу используются три режима: симплексный (от simplex – простой), полудуплексный и дуплексный (от duplex – двойной). Симплексная связь обеспечивает передачу данных только в одном направлении, при этом на одном конце линии имеется только передающее устройство, а на другом конце – только приемное. Полудуплексная связь обеспечивает обмен информации в обоих направлениях, но прием и передача в канале разделены во времени. Дуплексная связь обеспечивает передачу и прием данных в обоих направлениях одновременно.

Разработчики микроконтроллеров всегда испытывали дефицит выводов корпусов, в которые помещался МК, и естественно, что экономные двух- или трех проводные каналы последовательного обмена и реализующие их модули появились уже в первых МК и к сегодняшнему дню подавляющее большинство выпускаемых МК имеют их в своем составе.

Наиболее распространенное название модулей, реализующих подобного рода протоколы обмена – UART (Universal Asynchronous Receiver and Transmitter – универсальный асинхронный приемопередатчик). Несмотря на то, что в названии отсутствует упоминание о синхронном обмене, в большинстве подобных модулей он, тем не менее, реализован. Однако это название не является единственным, и некоторые производители МК используют свои имена: USART – Universal Synchronous/Asynchronous Receiver and Transmitter, SCI – Serial Communication Interface, USI – Universal Serial Interface, и др.

|

|

|

Рис. 1.21. Структура модуля последовательного обмена UART |

В обобщенном виде структура модуля UART может быть представлена так, как показано на рис. 1.21.

Основу модуля составляют передатчик и приемник, которые через внешние выводы передачи TxD и приема RxD реализуют выбранный с помощью бита Выбор режима регистра специальных функций UART режим последовательного обмена. Режим определяет способ обмена – синхронный или асинхронный, а так же используемый при асинхронном способе информационный кадр – 10 или 11 бит. При асинхронном обмене вывод TxD используется для передачи, а RxD – для приема. В синхронном режиме один из выводов используется как линия данных, а второй – как линия синхронизации.

Как было указано ранее, основу и передатчика и приемника составляют связка сдвигового и буферного регистров, с помощью которой достаточно легко реализуется преобразование параллельного кода в последовательный и обратно. Обращение к буферам данных приемника RDBUF и передатчика TDBUF осуществляется через единственный программно доступный буферный регистр SBUF в зависимости от выполняемой команды. При записи в регистр SBUF данные автоматически передаются в буферный регистр передатчика TDBUF, инициируя процедуру передачи. По завершении приема данные перемещаются из буферного регистра приемника RDBUF в регистр SBUF и могут быть затем считаны и использованы для дальнейшей обработки. Общее управление работой модуля осуществляется блоком логики управления и синхронизации.

Источниками задания скорости обмена, выбор которых определяется битом Источник задания скорости, могут служить как тактовый генератор МК, так и один из его таймеров. В случае использования тактового генератора скорость обмена задается с помощью делителя частоты битами Задание скорости обмена, а при использовании таймера – соответствующими настройками используемого для реализации этой функции таймера.

Передача данных инициируется любой командой записи в буферный регистр SBUF. При выполнении команды записи в регистр SBUF данные из него перемещаются в буфер передатчика TDBUF и блок логики управления и синхронизации реализует процедуру передачи. При этом содержимое TDBUF загружается в сдвиговый регистр и синхронно со стробами, поступающими из блока управления и синхронизации, биты из сдвигового регистра последовательно, начиная с младшего, передаются на вывод TxD MK. При асинхронном способе обмена в передаваемый кадр аппаратно добавляются стартовый и стоповый биты. При использовании 11-битового кадра в передаваемый бит D8 автоматически заносится значение из бита Передача 9-го бита, куда оно заранее должно быть занесено. Это может быть признак четного числа битов в передаваемом байте или любой другой необходимый пользователю признак или флаг.

По завершении передачи последнего в кадре стопового бита устанавливается триггер TI и соответствующий ему бит Флаг прерывания передачи TI в регистре специальных функций UART, который информирует МК о том, что передача кадра завершена, буфер передатчика пуст и в него могут быть загружены новые данные для передачи следующего кадра. Установка флага TI генерирует запрос на прерывание и, если прерывания от передатчика разрешены установкой бита Разрешение прерывания при передаче, выполняется соответствующая подпрограмма обслуживания.

В отличие от режима передачи, начало которого задается командой программы, переход в режим приема определяется состоянием на линии и происходит при приходе стартового бита (изменением состояния на линии из 1 в 0). Потому для разрешения процедуры приема в регистр специальных функций UART введен бит Разрешение приема. Если прием разрешен, то по переднему фронту принятого стартового бита блок управления и синхронизации начинает стробирование приемного сдвигового регистра в соответствии с заданной скоростью, а также прием и подсчет принятых битов. Для повышения достоверности приема каждого бита в состав приемника введен блок детектора битов, который несколько раз считывает уровень сигнала на входе RxD в интервале между стробами. Значение бита, заносимое в сдвиговый регистр приемника, определяется в детекторе битов мажоритарным способом, например по принципу два из трех. После завершения приема последнего бита данных в сдвиговом регистре приемника находится принятый байт данных, который автоматически переносится в регистр RDBUF. Если принимается 11-битовый кадр, то принятое значение 9-го бита в кадре автоматически переносится в бит Прием 9-го бита в регистре специальных функций UART, откуда оно может быть считано пользователем. Прием стоп-бита завершает процедуру приема и устанавливает триггер готовности принятых данных RI и одноименный бит Флаг прерывания приема RI в регистре специальных функций. Если при этом установлен бит Разрешение прерывания при приеме, то одновременно с установкой флага RI генерируется запрос на прерывание и вызывается подпрограмма обработки прерывания, в процессе выполнения которой принятый байт данных считывается из буферного регистра SBUF в память МК.

В некоторых семействах МК вектор прерывания UART один и для приема и для передачи, поэтому для определения источника прерывания в подпрограмме обслуживания производится программный опрос состояния флагов приема RI и передачи TI. В этом случае флаги RI и TI не сбрасываются автоматически при входе в подпрограмму обслуживания, а их сброс производится только после определения того, каким событием вызвано прерывание – приемом или передачей.