- •Санкт-петербургский государственный технический университет

- •Оглавление

- •Введение

- •1. Арифметические основы вычислительной техники

- •Позиционные системы счисления

- •1.2. Двоичная система счисления

- •1.3. Алгоритмы преобразования десятичных чисел в двоичные

- •В двоичную систему счисления методом вычитания

- •1.4. Восьмеричная и шестнадцатеричная системы счисления

- •Представление чисел в различных системах счисления

- •1.5. Представление символьной информации

- •Представление алфавитно-цифровых и управляющих символов в коде ascii

- •1.6. Представление отрицательных чисел

- •1.7. Сложение и вычитание двоичных чисел

- •Правила сложения двоичных чисел

- •Архитектура микроконтроллеров 80c51

- •Общие сведения о микроконтроллерах 80c51

- •2.2. Особенности архитектуры

- •2.3. Организация памяти

- •2.4. Программная память

- •2.5. Память данных

- •Адресное пространство внутренней памяти данных, доступное для побитовой адресации

- •Регистры специальных функций мк 80с51

- •2.6. Слово состояния программы

- •Формат слова состояния программы

- •2.7. Общая характеристика системы команд

- •Система команд микроконтроллеров семейства mcs-51

- •Команды, модифицирующие флаги psw

- •2.8. Способы адресации

- •2.9. Синхронизация процессора

- •А. Для всех команд, кроме movx; в. Для команды movx

- •2.10. Параллельные порты

- •2.11. Таймеры/счетчики

- •Альтернативные функции портов p0, p2 и p3 мк 80с51

- •Регистр управления режимом таймера/счетчика

- •Регистр управления таймера/счетчика

- •2.12. Последовательный порт

- •Регистр управления последовательного порта

- •Регистр управления мощностью

- •Программирование таймера 1 для обеспечения работы последовательного порта в режимах 1 и 3

- •2.13. Программный Счетчик

- •2.14. Стек

- •2.15. Подпрограммы

- •2.16. Система прерываний

- •Адреса векторов прерываний мк 80с51

- •Регистр разрешения прерываний

- •Регистр приоритетов прерываний

- •2.17. Аппаратный сброс

- •Включении электропитания

- •2.18. Энергосберегающие режимы работы

- •3. Технология программирования микроконтроллеров

- •3.1. Общие положения

- •3.2. Подготовка исходного текста программы

- •3.3. Трансляция программы

- •Трансляции программы

- •Ошибки в программе

- •3.4. Компоновка программы

- •3.5. Отладка программы

- •Литература

- •Система команд мк семейства mcs-51

- •Эмулятор пзу чип32-02

- •1. Назначение

- •2. Технические характеристики

- •3. Инструкция по эксплуатации

- •Англо-русский словарь специальных терминов и сокращений

- •195251, Г. Санкт-Петербург, ул. Политехническая, д. 29

2.3. Организация памяти

2.3.1. При организации взаимодействия CPUс памятью и другими функциональными устройствами используется единый принцип идентификации устройств–выбор по адресу. Совокупность всех возможных адресов называетсяадресным пространством.

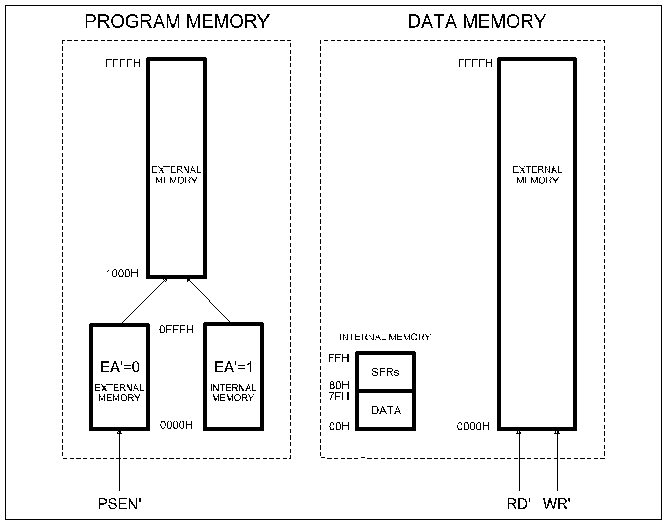

2.3.2. МК 80C51 имеют четыре раздельных адресных пространства: адресное пространство программной памяти (program memory) объемом 64К байт, адресное пространство внешней памяти данных (external data memory) объемом 64К байт, адресное пространство внутренней памяти данных (internal data memory) объемом 128 байт и адресное пространство регистров специальных функций (SFR – Special Function Register) объемом 128 байт (рис. 2.4).

Микроконтроллеры типа 80С51BHPотличаются от микроконтроллеров других типов тем, что имеют объемы адресных пространств программной памяти и внешней памяти данных по 4К байт.

2.3.3. Программная память предназначена для хранения кодов команд или констант. Это постоянная память, она доступна только для чтения и недоступна для записи (ROM – Read Only Memory). МК 80C51 выпускаются четырех типов (см. рис. 2.1): без внутренней постоянной памяти (80С31BH), с внутренней постоянной памятью масочного типа (80C51BH), с внутренней постоянной памятью масочного типа, защищенной от внешнего считывания (80C51BHP), с внутренней программируемой постоянной памятью, стираемой ультрафиолетовым светом (D87C51), и с однократно программируемой внутренней постоянной памятью (P87C51).МикросхемаP87C51 отличается от микросхемыD87C51 только тем, что она выпускается в пластмассовом корпусе, не имеющем окна для стирания памяти, в то время как микросхемаD87C51 имеет керамический корпус с окном, через которое осуществляется ультрафиолетовое облучение кристалла.

Для того, чтобы запретить доступ CPUк внутренней программной памяти, на МК требуется подать внешний логический сигналEA’=0(External Access). При чтении информации из внешней программной памяти МК вырабатывает стробPSEN’(ProgramStorage Enable).

Для разрешения доступа к внутренней программной памяти необходимо выполнение условия EA’=1. При обращенииCPUк внутренней программной памяти стробPSEN’ не вырабатывается.

Рис. 2.4. Структура памяти МК 80C51

2.3.4. Память данных (data memory) предназначена для хранения переменных в процессе выполнения программы. Это оперативная память, она доступна как для чтения, так и для записи (RAM – Random Access Memory). При обращении к внешней памяти данных МК вырабатывает строб чтенияRD’(read) и строб записиWR’(write).

2.3.5. Адресные пространства внешней памяти программ и внешней памяти данных могут быть объединены. Для этого нужно подать сигналы RD’ иPSEN’ на входы логического элемента И, выходной сигнал которого следует использовать в качестве строба чтения из единой внешней памяти программ/данных.

2.4. Программная память

2.4.1. При сбросе МК (по внешнему сигналу RST)CPUначинает выполнение программы с адреса 0000H. В том случае, когдаEA’=1 (см. рис. 2.4), начальный участок программы (младшие 4К байт) извлекается процессором из внутренней постоянной памяти, а остальная часть программы–из внешней памяти. Если МК не имеет внутренней постоянной памяти (или она не используется), то на входEA’ следует подать логический сигнал 0. При этом выборка всей программы будет осуществляться из внешней памяти

2.4.2. Область адресного пространства программной памяти, начиная с адреса 0003Н, отводится для размещения начальных участков подпрограмм обслуживания прерываний (8 байтов на каждую из пяти программ). Адрес первого байта подпрограммы обслуживания прерывания (0003Н, 000BH, 0013H, 001BH, 0023Н), называемый адресом вектора прерывания, формируется контроллером прерываний МК аппаратно при обработке соответствующего запроса прерывания (см. подраздел 2.17).

2.4.3. Подключение к МК микросхемы внешней программной памяти показано на рис. 2.5, где A0A7–входы младших разрядов адреса,A8A15–входы старших разрядов адреса,OE’ иCS’–управляющие входы,DATA–данные, считываемые из памяти,LATCH–регистр-защелка младшего байта адреса (8-разрядный параллельный регистр памяти, тактируемый уровнем).

При обращении к внешней программной памяти порт P0 МК работает в режиме временного мультиплексирования и служит как для вывода младшего байта адреса ячейки внешней памяти, так и для ввода в МК байта данных. ПортP2 используется для вывода старшего байта адреса.

Временным мультиплексированием(time-division multiplexing) называется предоставление канала ввода/вывода информации различным устройствам в разные промежутки времени.

Стробирование ввода/вывода информации через порт P0 при чтении данных из внешней программной памяти осуществляется с помощью управляющих сигналовALEиPSEN’, вырабатываемых МК. СигналALE(Address Latch Enable), поступающий с соответствующего выхода МК на тактовый вход регистра-защелки, предназначен для “защелкивания” младшего байта адреса, т.е. запоминания в регистре-защелке того кода, который был на выходах портаP0 в момент окончания сигналаALE. СигналPSEN’служит для управления считыванием данных из микросхемы памяти. Если на управляющий входCS’(Chip Select) микросхемы памяти поступает сигналCS’=0, то подача сигналаPSEN’=0 на управляющий входOE’(Output Enable) микросхемы приведет к тому, что байт данных (DATA) из адресуемой ячейки памяти поступит на вход портаP0 МК.

Рис. 2.5. Подключение микросхемы EPROM к МК 80C51

Временные диаграммы работы МК при выборке кодов команд из внешней программной памяти приведены в подразделе 2.9.

2.4.4. При обращении к внешней программной памяти всегда вырабатывается 16-разрядный адрес (даже тогда, когда объем исполняемой программы меньше, чем 64К байт), поэтому в тех случаях, когда для хранения программы или значений констант используется внешняя программная память, приходится “жертвовать” двумя портами МК.