лабы / Сети Петри / Документация / lection203

.pdf

зависимости от того, на сколько разрядов необходимо произвести нормализующий сдвиг и в какую сторону: вправо или влево. В этом случае, поскольку время t должно быть выбрано максимальным, необходимым для самого медленного блока конвейера, может оказаться так, что большую часть времени все единицы будут пребывать незагруженными, ожидая окончания t единиц времени.

В асинхронном конвейере в среднем процесс обработки может быть ускорен сигнализацией о завершении каждого шага конвейерной обработки и готовности передать свой операнд и получить новый. Результат шага k конвейерной обработки может быть послан на шаг (k + 1), как только шаг k выполнен, а блок (k.+ 1) свободен. Рассмотрим произвольный шаг конвейерной обработки. Очевидно, нужно иметь место, куда можно поместить входы и выходы в то время, как они используются или производятся. Обычно это предполагает наличие регистров: блок использует значение своего входного (буферного) регистра для вычисления значения выходного(буферного) регистра. После этого необходимо ждать, пока (1) — выходной регистр блока не будет очищен путем пересылки содержимого во входной регистр следующего блока и (2)

— новое входное значение не появится в его входном регистре. Таким образом, для управления блоком k конвейера необходимо знать, когда выполняются следующие условия:

входной регистр заполнен; входной регистр пуст; выходной регистр заполнен; выходной регистр пуст; блок занят; блок свободен;

пересылка осуществлена.

На рис. 3.18 и 3.19 показано, как можно промоделировать асинхронный конвейер такого типа. На рис. 3.18 приведена блок-схема конвейера, моделируемого сетью Петри на рис. 3.19.

Отметим, что в этой модели мы промоделировали реальную работу блоков конвейера как не примитивных событий. Это позволяет нам игнорировать на этом уровне конкретные детали того, что делают блоки, и сосредоточиться на их правильном взаимодействии. Каждая операция также может быть промоделирована сетью Петри. Затем сети Петри для каждого блока можно внести в сеть Петри на рис. 3.19, получив более детальную сеть. Такая возможность моделирования системы на нескольких различных уровнях абстракции, т. е. иерархическим образом, может быть весьма полезна.

Рис. 3.18. Блок-схема устройства управления асинхронной ЭВМ с конвейерной обработкой.

Рис. 3.19. Модель сети Петри устройства управления асинхронной ЭВМ с конвейерной обработкой.

3.3.3. Кратные функциональные блоки

Конвейерная структура управления, рассмотренная в предыдущем разделе, — это один из подходов к построению очень больших быстродействующих вычислительных систем. Другой подход, использованный, например, в CDC 6600 [291] и IBM 360/91 [10], использует кратные функциональные блоки. В CDC 6600 имеется 10 функциональных блоков: блок ветвления (для условных переходов); булев блок (для булевых операций); блок сдвига; блок сложения с плавающей точкой; блок сложения с фиксированной точкой; 2 блока умножения; блок деления и 2 блока приращения (для индексирования). Кроме того, имеется несколько регистров для хранения входных и выходных значений функциональных блоков. Устройство управления ЭВМ организует одновременное функционирование нескольких независимых блоков.

В качестве примера рассмотрим следующую последовательность, инструкций для вычислительной системы CDC 6600:

1.Умножить X1 на X1, результат поместить в Х0.

2.Умножить Х3 на X1, результат поместить в Х3.

.3. Сложить Х2 с Х4, результат поместить в Х4.

4.Сложить Х0 с Х3, результат поместить в Х3.

5.Разделить Х0 на Х4, результат поместить в Х6.

Для выполнения инструкций устройство управления выдает первую инструкцию в блок умножения.

Поскольку существуют два блока умножения, можно выдать также вторую инструкцию. При этом обоим блокам доступно содержимое X1. Инструкция 3 может быть выдана блоку сложения. Теперь, для того, чтобы выдать инструкцию 4, мы должны ждать, пока инструкции 1, 2 и 3 не будут завершены, так как инструкция 4 использует блок сложения (занятый выполнением инструкции 3), Х0 (вычисляемый инструкцией 1) и Х3 (вычисляемый инструкцией 2). Инструкция 5 должна ждать выполнения инструкции 1 (вычисление Х0) и инструкции 3 (вычисление Х4).

Организация параллелизма этого типа (выполнение нескольких инструкций программы одновременно) должна быть такой, чтобы результат выполнения программы с использованием параллелизма и без него был бы одинаков. Некоторые инструкции в программе требуют результата предыдущей инструкции до выполнения последующей. Система, которая организует параллелизм в последовательной программе таким способом для получения правильных результатов, обладает свойством детерминированности. Условия поддержания детерминированности были рассмотрены Бернстай-ном [28]. Вот они: для двух операций а и b, таких, что а предшествует b на линейном участке программы, b может начать выполняться прежде, чем выполнена а, тогда и только тогда, когда входные данные b не требуют результата а и результаты b не изменят ни входных данных, ни результатов а.

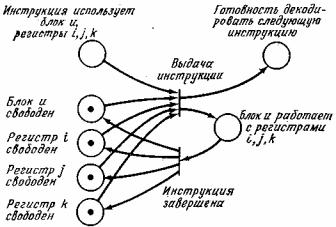

Один из методов применения таких ограничений для построения устройства управления, выдающего инструкции отдельным функциональным блокам, основан на таблице резервирования. Инструкция для функционального блока и, использующая регистры i, j и k, выдается только в том случае, если ни одна из четырех компонент не зарезервирована; при выдаче инструкции все эти компоненты

становятся зарезервированными. Если же из-за того, что либо •функциональный блок, либо один из регистров уже используются, инструкция не может быть выдана, то устройство управления перед переходом к следующей инструкции ожидает выполнения условий для выдачи этой инструкции.

Схему такого типа можно промоделировать сетью Петри. Каждому функциональному блоку и каждому регистру поставим в соответствие позицию: если блок или регистр свободен — в позицию будет помещена фишка, если нет — фишки в позиции не будет. Кратные идентичные функциональные блоки показываются соответствующим числом фишек в позициях. На рис. 3.20 изображена часть сети Петри, которая может быть использована для моделирования выполнения инструкции, использующей блок и и регистры i, j и k.

Рис. 3.20. Часть сети Петри, моделирующая устройство управления для ЭВМ, с кратными регистрами и кратными функциональными блоками.

Моделирование всего устройства управления, конечно же, потребует гораздо большей сети Петри. Схема, описанная выше, представляет собой очень простой способ введения параллелизма и не рассматривает, например, тот факт, что кратные функциональные блоки могут использовать одновременно одинаковые входные регистры. Таким образом, максимальный параллелизм в этой схеме может быть не получен [153]. Однако существуют другие схемы, с помощью которых это достигается. Такие более сложные схемы также моделируются (более сложными) сетями Петри. Эти сети могут быть очень велики. CDC 6600, например, имеет 24 различных регистра и 64 различных инструкции. Если для каждой инструкции и тройки регистров требуется позиция, соответствующая условию «блок и оперирует регистрами i, j и k», то необходимо более полумиллиона позиций и переходов. Главная трудность заключается в представлении того факта, что содержимое внутренних регистров может определять, какие

регистры и блоки будут использоваться (индексирование).

(Однако никакая программа не использует все возможные комбинации регистров и блоков. Это позволило [274] промоделировать вычислительную систему CDC 6600 с помощью сетей Петри. Эта модель сети Петри была затем использована для оптимальной генерации кода компилятором с Фортрана, что мы увидим в разд. 3.5.)