Добавил:

Upload

Опубликованный материал нарушает ваши авторские права? Сообщите нам.

Вуз:

Предмет:

Файл:БО_Презентации / Пр к лек БО 2014 -1ч / Лек 10 ОЗУ.ppt

X

- •2.2.2. Оперативные ЗУ

- •Статическая оперативная память

- •Ячейка статической двоичной памяти (двоичный триггер) на КМОП-технологии

- •Ячейка статической двоичной памяти (двоичный триггер) на КМОП-технологии

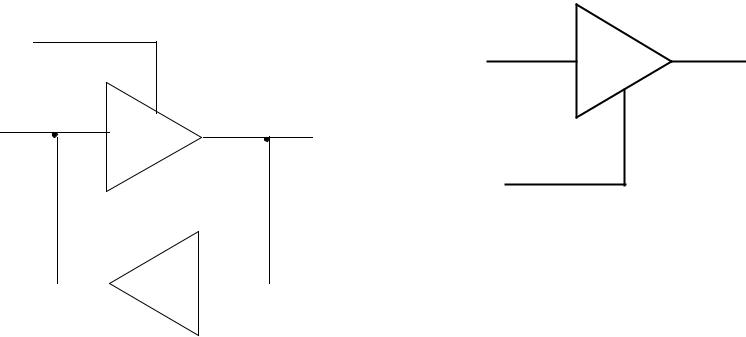

- •Буферная схема с тремя состояниями

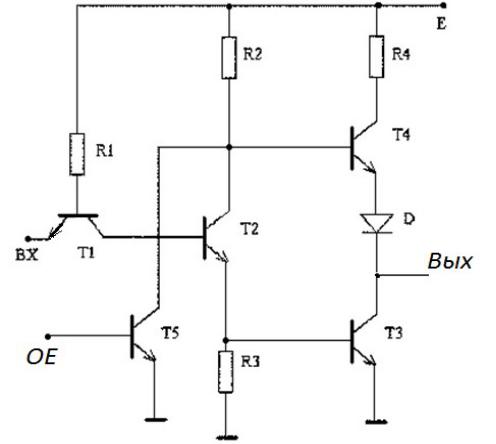

- •Буферный каскад с тремя состояниями

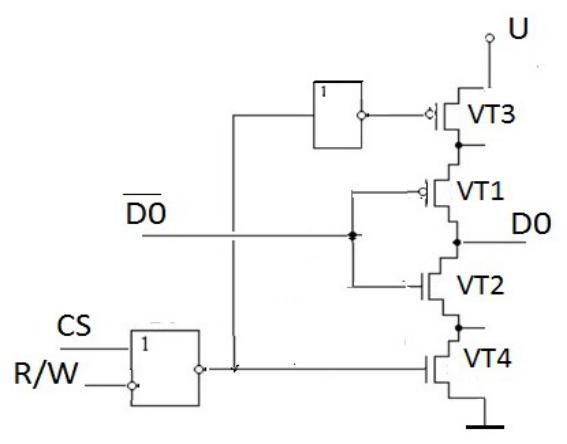

- •Выходной каскад с третьим состоянием в схемотехнике КМОП

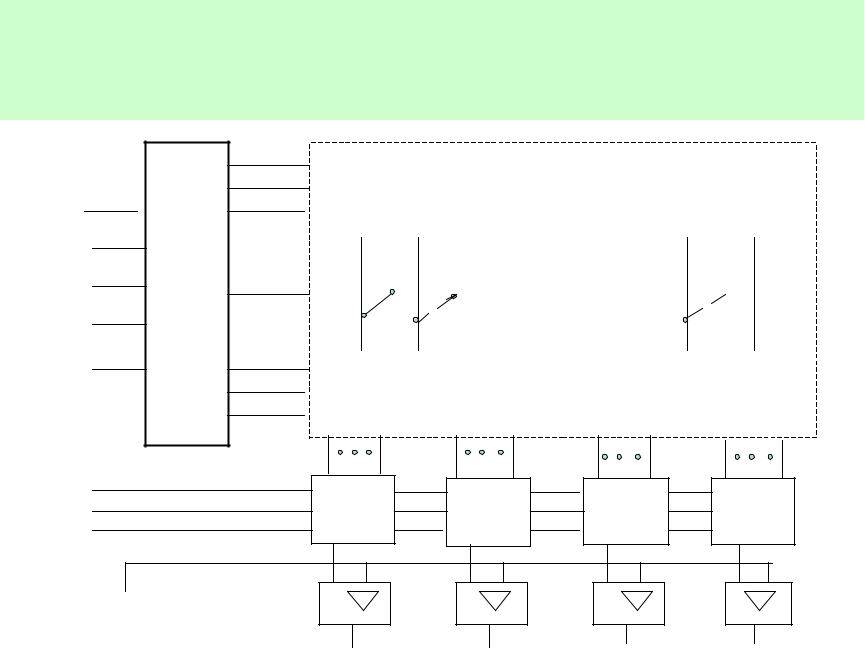

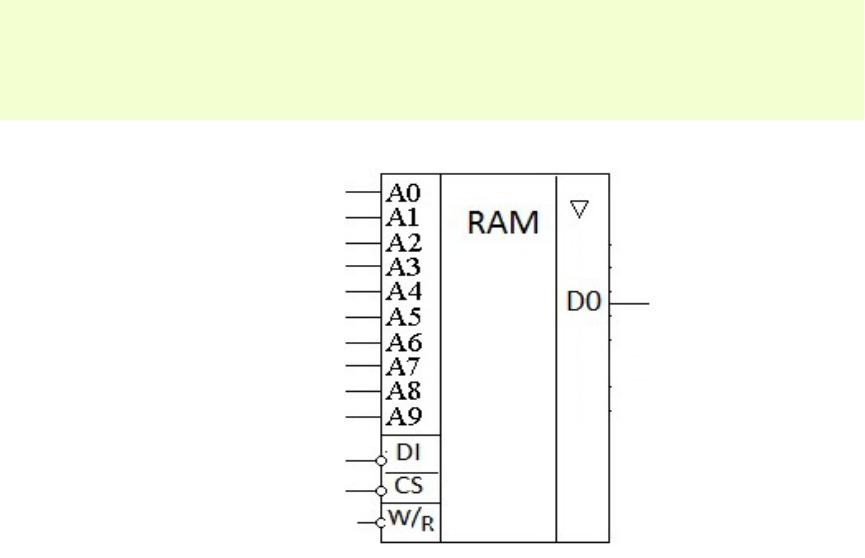

- •Микросхема статической оперативной памяти

- •Выборка запоминающих элементов

- •Динамическая оперативная память

- •Динамическая оперативная память

- •Устройство ячейки динамической памяти

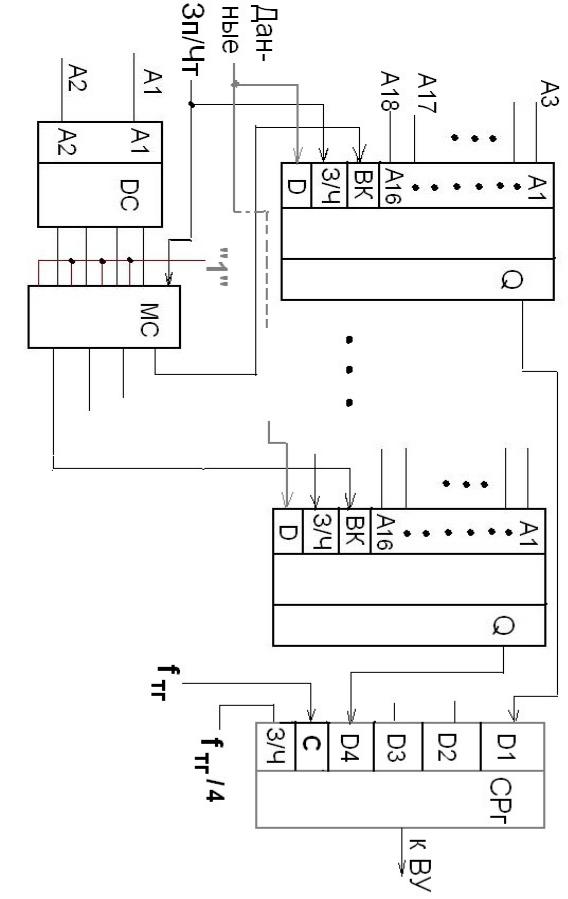

- •Регенерация динамической памяти

- •Структурная схема МС динамического ОЗУ

- •Память DDR SDRAM

- •Сравнение статических и динамических ОЗУ

- •Сравнение статических и динамических ОЗУ (окончание)

- •2.3. Флэш (Flash) память

- •Устройство элементарной ячейки флэшпамяти

- •Отличие flash-памяти от EEPROM

- •Современные технологии флэш-памяти

- •Структура матрицы накопителя флэш-памяти с паралл.

- •Последовательное соединение элементарных ячеек, образующих группы (структура И-НЕ)

- •Условно-графическое обозначение FLASH памяти на принципиальных схемах

- •Преимущества флэш-памяти по сравнению с EEPROM

- •Проблема интеграции на одном кристалле различных видов памяти

- •2.4.Новые виды памяти

- •Структура ячейки памяти FRAM

- •Магниторезистивная оперативная память (MRAM – англ. magnetoresistive random- access memory)

- •Битовые ячейки памяти MRAM

- •Битовая ячейка памяти MRAM

2.2.2. Оперативные ЗУ

(RAM - Random Access Memory)

•гл. достоинство – предельно малое время доступа (~ n нс); благодаря этому поддерживают высокую скорость обработки информации

•гл. недостаток – энергозависимость, из-за чего при отключении питания все, что не записано на внешний носитель, теряется

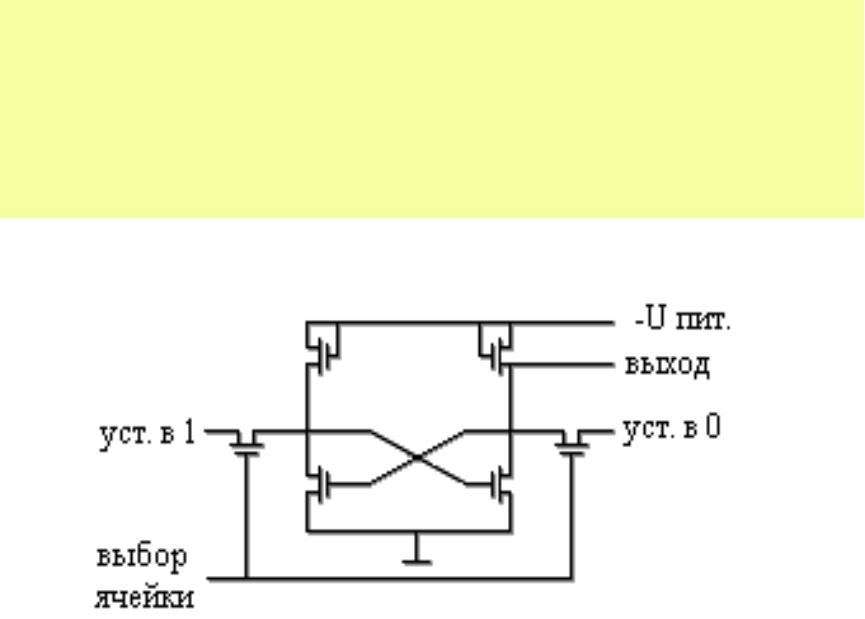

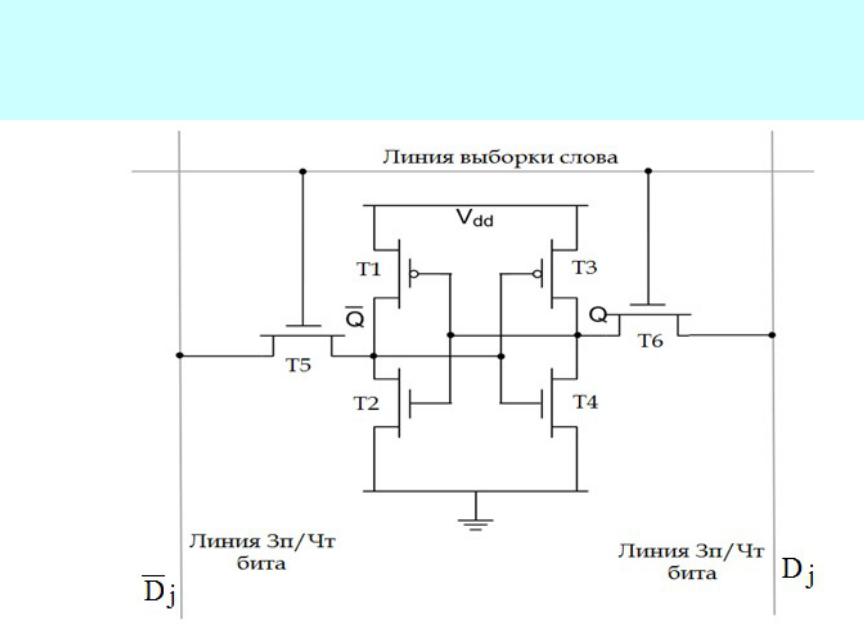

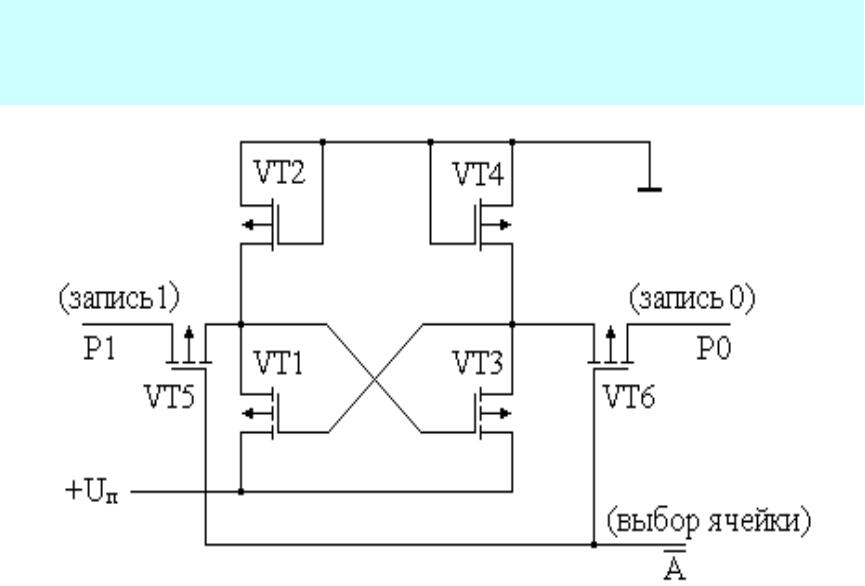

Статическая оперативная память

(Static Random Access Memory):

схема ячейки (кластер из 6-ти транз-ров)

Ячейка статической двоичной памяти (двоичный триггер) на КМОП-технологии

Ячейка статической двоичной памяти (двоичный триггер) на КМОП-технологии

Буферная схема с тремя состояниями

• OE – “разрешение по вых.” |

Q |

А |

I /O |

OE |

|

|

|

|

|

|

А |

|

0 |

0 |

1 |

1 |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

OE |

|

|

|

|

|

OE |

|

0 |

1 |

0 |

1 |

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

Z3 → ∞ Q |

|

0 Z3 |

1 Z3 |

||||

|

|

|

|

|

|

|||||||

Буферный каскад с тремя состояниями

В третье

состояние схема переводится сигналом ОЕ, запирающим оба транзистора Т3, Т4 При разреш. сигнале ОЕ входные “1” или

“0” появляются на вых.

Выходной каскад с третьим состоянием в схемотехнике КМОП

|

Статические ОЗУ имеют, как правило, |

||||

|

2DM-структуру |

|

|

||

|

0 |

|

|

|

|

А7 |

Дш |

|

|

|

|

x |

|

|

|

||

|

|

|

|

||

А5 |

|

|

|

|

|

А3 |

|

|

|

|

|

|

31 |

|

|

|

|

А2 |

MX |

MX |

MX |

MX |

|

А0 |

|||||

|

|

|

|

||

|

cs |

|

|

|

|

|

D0 |

D 1 |

D 2 |

D 3 |

|

Микросхема статической оперативной памяти

RAM

RAM

Соседние файлы в папке Пр к лек БО 2014 -1ч