- •Управление четырехфазным ШД

- •Использование регистров ЦП

- •START

- •Команды RRC и RLC: циклический сдвиг аккумулятора вправо и влево

- •Процедура COUNTER

- •Процедура WAIT

- •4.6. Система прерываний

- •Радиальная и векторная схемы организации прерываний

- •Радиальные прерывания

- •Радиальные прерывания

- •Векторная приоритетная система прерываний

- •Организация векторного прерывания

- •Типовая структура ЦП

- •Сигналы прерываний (на примере МП

- •Система прерываний применит. к МП-ру

- •Система прерываний применит. к МП-ру

- •Входы запросов радиального прерывания

- •МаскированиеМаскированиесостоит в запрещении действия соответствующего входа запроса прерывания.

- •Последовательность действий МП в режиме прерывания

- •Выполнение команды рестарта

- •Цикл М1: выдача на ША содерж. PC, на ШД – байта состояния, выборка

- •4.7. Прямой доступ к памяти

- •ВУ запрашивает режим ПДП сигналом высокого уровня на линии HOLD.

- •Цикл ЧТЕНИЯ ПАМЯТИ в режиме ПДП

- •МП формирует Н-уровень квитирующего сигнала HLDA подтверждения запроса ПДП по нарастающему фронту Ф1,

- •4.8.Память МПС

- •Сегментация памяти

- •Сегментация памяти: иллюстрация

- •Адрес сегмента нужно сдвинуть влево на 4 р-да (дописать 4 нуля справа) и

- •Преобразование логического адреса в физический в защищённом режиме

- •Разрядность МП

- •Построение модуля памяти

- •Увеличение числа хранимых слов при построении модуля памяти

- •Литература по теме «МП»

- •Доп. литература по МК-рам

- •Микроконтроллеры AVR

- •8-битный AVR микроконтроллер

- •Микроконтроллеры PIC

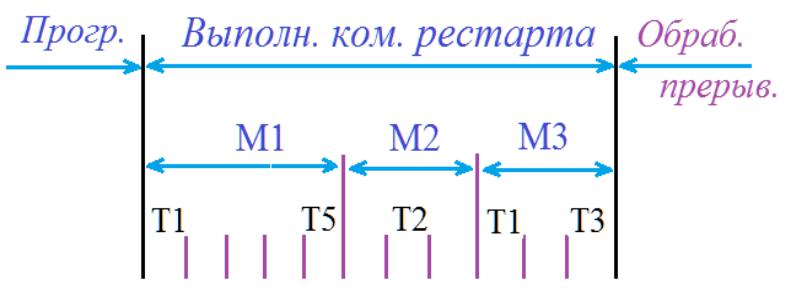

Цикл М1: выдача на ША содерж. PC, на ШД – байта состояния, выборка и дешифр. команды

RESTART

Циклы М2, М3: загрузка содерж. PC в стек

4.7. Прямой доступ к памяти

Этот режим используется для обмена МП с

периферийными устройствами, имеющими высокую

скорость передачи данных

ВУ запрашивает режим ПДП сигналом высокого уровня на линии HOLD.

МП имеет вход HOLD запроса захвата шин и выход HLDA подтверждения захвата

Реакция микропроцессора на сигнал HOLD: приостанавливается выполнение программы и переводит внутренние буферы шин адреса и данных в высокоимпедансное состояние. Шинами начинает управлять контролер ПДП, организуя обмен данными между периферийным устройством и памятью МП системы.

Цикл ЧТЕНИЯ ПАМЯТИ в режиме ПДП

МП формирует Н-уровень квитирующего сигнала HLDA подтверждения запроса ПДП по нарастающему фронту Ф1, а по нараст.

фронту Ф2 переводит буферы шин

адреса и данных в высокоимпедансное состояниеКогда между периферийным устройством и

памятью МП системы передан необходимый блок данных, контроллер ПДП устанавливает L-уровень на линии HOLD и микропроцессор выходит из состояния TWN

4.8.Память МПС

•СОЗУ (регистры)

•Внутр. кэш-

память

(встроенное в МП ОЗУ)

•ОЗУ

•ПЗУ

•ВЗУ

Сегментация памяти

•Решается проблема адресации 2n ячеек памяти c помощью m-разрядного регистра при m < n.

•Сегмент – независимый, поддерживаемый на

аппаратном уровне блок памяти.

•Для обращения к конкретному физическому адресу памяти надо задать адрес начала сегмента и смещение:

segment: offset

например, |

0041: 000Сh |

Сегментация памяти: иллюстрация

Адрес сегмента нужно сдвинуть влево на 4 р-да (дописать 4 нуля справа) и сложить с величиной смещения