MU_KP1_3494

.pdf

11

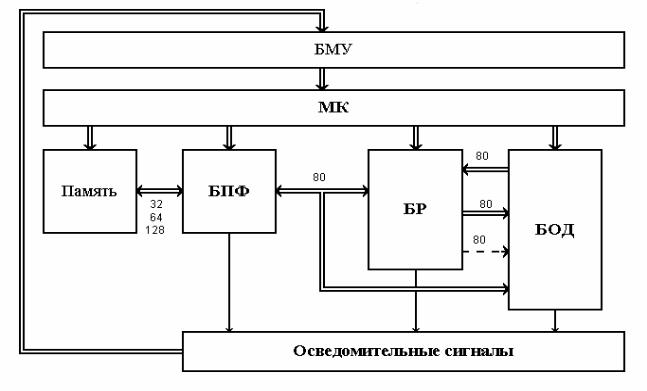

Рис.3.1.Укрупненная блок-схема процессора

3.2.Память

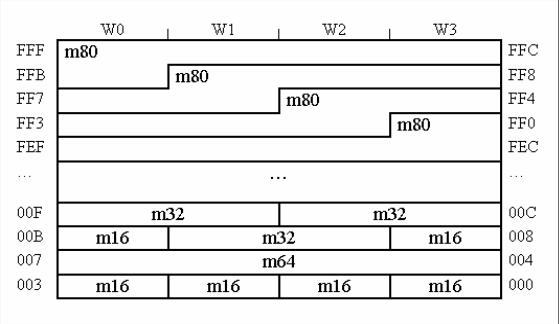

Вкурсовом проекте принято, что в процессоре используется одноуровневая память данных емкостью 8 кБ и длиной слова памяти MW 4, 8 или 16 байт, в зависимости от задания. Рассмотрим организацию памяти с длиной слова памяти равной 8 байт. Адрес данного к началу операции вычислен и находится в адресном регистре EA. В операциях с

ПТ минимальный размер данного 2 байта, поэтому адресация производится с точностью до двухбайтового слова W. Адрес содержит 12 бит, из них старшие 10 адресуют слово MW, а младшие 2 - слово W в MW. Данное длиной до 8 байт выбирается за одно, а данное длиной 10 байт - за два обращения. Адрес учетверенного слова QW (m64int или m64real) кратен четырем, адрес двойного слова QW (m32int или m32real) заканчивается битами 00, 01 или 10, но не 11. Адрес W (m16int) может быть любым в пределах заданной емкости памяти. Адрес 10-байтового значения (m80real или m80dec) также может быть любым, но не должен превышать FFBH. Адресом любой единицы данных является адрес ее младшего двухбайтового слова. Адресация памяти и примеры размещения данных приведены на рис.3.2.

12

Рис.3.2. Размещение данных в памяти

При выборке из П читается всегда полное слово MW. Данное формата m64 совпадает с MW. Выделение из MW данных форматов m16, m32 или части данного формата m80 происходит в БПФ.

При записи данное должно быть размещено в П в соответствии со своим форматом и адресом, поскольку запись полного слова может привести к разрушению информации в соседних полях MW. Для этого память выполняется в виде четырех банков Б3, Б2, Б1, Б0, которые хранят соответственно двухбайтовые слова W3, W2, W1, W0 всех слов памяти. Управляют записью в банки биты разрешения записи Z3, Z2, Z1, Z0, формируемые в зависимости от формата двух младших битов адреса, как показано в табл. 3.1. Прочерки в таблице относятся к запрещенным комбинациям. Обозначения m80(1) и m80(2) соответствуют записи первой и второй части 80-битового значения.

Схема организации памяти приведена на рис 3.3. Здесь Б3-Б0 - банки памяти, EAR - регистр исполнительного адреса, ФСРЗ - формирователь сигналов разрешения записи Z3-Z0. Схема управляется сигналами (битами микрокода) WR - запись, RD - чтение, FD - формат данного (4 варианта), Т - такт записи. Сигнал Т используется при записи 10-байтовых значений m80: Т=0 - первый такт записи, Т=1 - второй такт. ФСРЗ вырабатывает также код IncA (инкремент адреса) при чтении или записи данных типа m80. К EAR прибавляются значения 1,2,3 или 4 по числу двухбайтовых слов, прочитанных или записанных при первом обращении.

|

|

|

|

13 |

|

|

|

|

|

|

Формирование битов разрешения записи |

|

Таблица 3.1 |

|

|||||

|

Формат данного |

|

|

Младшие биты адреса |

|

|

|

||

|

|

11 |

10 |

|

01 |

|

00 |

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

||

|

m16 |

|

1000 |

0100 |

|

0010 |

|

0001 |

|

|

m32 |

|

- |

1100 |

|

0110 |

|

0011 |

|

|

m64 |

|

- |

- |

|

- |

|

1111 |

|

|

m80(1) |

|

1000 |

1100 |

|

1110 |

|

1111 |

|

|

m80(2) |

|

1111 |

0111 |

|

0011 |

|

0001 |

|

|

|

|

|

|

|

|

|

|

|

Рис.3.3. Организация чтения и записи памяти

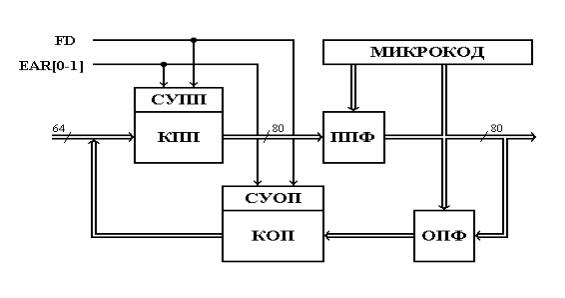

3.3. Блок преобразования форматов

БПФ преобразует читаемое данное из формата источника в формат РТ (прямое преобразование) и записываемое данное из формата РТ в формат получателя (обратное преобразование). При преобразованиях учитываются случаи денормализованного операнда и нуля, а также размещение данного в памяти в зависимости от формата и младших битов адреса.

Прямое преобразование включает в себя следующие действия:

позиционирование прочитанного данного, то есть размещение его в приемном регистре в некотором стандартном виде, независящем от его положения на шине данных;

довыборка данного, если необходимо;

преобразование в прямой двоичный код (для десятичных чисел);

преобразование из целочисленного представления в расширенный вещественный формат (для целых чисел);

14

преобразование из форматов ОТ или ДТ в формат РТ ( для вещественных чисел);

передача в блок регистров БР или в блок обработки данных БОД.

Обратное преобразование:

прием данного из БР;

преобразование в формат ОТ или ДТ, если формат получателя 32real

или 64real;

преобразование в прямой 64-битный целочисленный двоичный код, если формат получателя 16int, 32int, 64int или 80dec;

преобразование целого в обратный двоичный код заданной длины, если формат получателя 16int, 32int или 64int;

преобразование целого в упакованный десятичный код, если формат получателя 80dec;

позиционирование записываемого данного, то есть размещение его в слове памяти в соответствии с младшими битами адреса, и передача в память;

дозапись данного в память, если это необходимо.

Укрупненная схема БПФ приведена на рис 3.4. Она включает в себя прямой (ППФ) и обратный (ОПФ) преобразователи форматов, коммутаторы прямого (КПП) и обратного (КОП) позиционирования со схемами управления СУПП и СУОП. Коммутаторы управляются сигналами EAR[0:1] (2 младших бита адреса) (это при длине слова ОП 64), микрокодом формата данного FD, битом такта записи Т.

Рис.3.4.Укрупненная схема БПФ

Преобразователями управляют специальные последовательности микрокодов, вырабатываемые БМУ в зависимости от вида преобразования и его шага, а также от промежуточных результатов преобразования.

15

Некоторые варианты позиционирования и преобразования рассматриваются ниже.

3.3.1. Прямое позиционирование

Коммутатор прямого позиционирования КПП преобразует 64-битное слово W64, прочитанное из памяти, в 80-битное слово W80. КПП может быть выполнен на базе нескольких мультиплексоров или программируемого сдвигателя. Знак в W64 располагается в битах 63, 47, 31 или 15. Позиция знака в W80 - бит 79. Коммутировать знаковый бит можно с помощью одноразрядного 4-входового мультиплексора. Управляющий код мультиплексора вырабатывается СУПП в зависимости от формата данного и младших битов адреса.

Позиционирование вещественных чисел выполняется следующим образом.

8 битов порядка и 23 бита мантиссы чисел формата ОТ могут располагаться в битах [62:32], [46:16] или [30:0] W64 при значениях EAR[0:1] 10, 01 или 00 соответственно. В W80 они заполняют биты [71:41]. Позиционирование выполняется путем передачи сдвинутых влево кодов: CASE (EAR[0:1])

{10B : W80[78:0]:=L9 (W64);

01B : W80[78:0]:=L25 (W64);

00B : W80[78:0]:=L41 (W64);} W80[78:72,40:0]:=0.

11 бит порядка и 52 бита мантиссы чисел формата ДТ размещаются в битах [62:0] W64. В W80 они занимают биты [74:12]. Позиционирование выполняется передачей сдвинутого на 12 бит влево W64 и обнулением битов 78:75 и 11:0 W80. Числа формата РТ выбираются за 2 шага. На первом шаге выбираются 2, 4, 6 или 8 младших байтов, на втором - соответственно 8, 6, 4 или 2 старших байта. При первой выборке передача W64 - W80 идет со сдвигом вправо на 48, 32, 16 битов или без сдвига. При второй выборке происходит сдвиг влево на 16, 32, 48 или 64 бита.

Позиционирование целых чисел выполняется следующим образом.

Значащая часть целых чисел длиной 15, 31 или 63 бита пересылается в старшие биты мантиссы слова W80. При передаче из W64 в W80 чисел формата 16int происходит сдвиг влево на 1, 17, 33 или 49 битов, при передаче слова формата 32int - сдвиг на 1 или 33 бита, формата 64int - на 1 бит. Затем обнуляются 15 старших и 1, 32 или 49 младших битов значащей части W80.

16

Позиционирование 80-битных десятичных чисел выполняется так же, как и чисел формата РТ.

Прямое преобразование вещественных чисел

Числа форматов ОТ или ДТ в формат РТ преобразуются в следующей последовательности.

Если число равно нулю, то результатом будет соответственно код нуля в формате РТ. Код нуля во всех форматах: Е=0, М=0.

Если число нормализовано:

прибавить к смещенному порядку (биты 78-64 W80) разность между смещением порядка в формате РТ и в исходном формате, то есть

16383-127=16256 для ОТ и 16383-1023=15360 для ДТ;

сдвинуть мантиссу (биты 63-0) на один бит вправо и записать 1 в бит

63.

Если число денормализовано (Е=0, М<>0) провести его нормализацию. Для этого:

прибавить к порядку 16256 или 15360;

произвести сдвиг мантиссы влево до появления 1 в ее старшем бите, при каждом сдвиге вычитать 1 из порядка.

При наличии программируемого сдвигателя сдвиг производят сразу

на nZ разрядов, где nZ - количество ведущих нулей в коде мантиссы, с вычитанием nZ из порядка. Значение nZ определяется специальной схемой.

3.3.2. Прямое преобразование целых чисел

Последовательность преобразования ненулевых чисел в формат РТ из форматов 16int, 32int или 64int:

если число отрицательное, преобразовать его в прямой код;

записать в биты порядка значение 16383 + r, где r - разрядность значащей части целого числа (15, 31 или 63 );

если старшие биты мантиссы нулевые, сдвигать ее влево до появления 1 в старшем бите, вычитая при каждом сдвиге 1 из порядка.

3.3.3. Прямое преобразование десятичных чисел

Числа формата m80dec сначала преобразуются в двоичное целое 64int, а затем уже в формат РТ, как было описано выше.

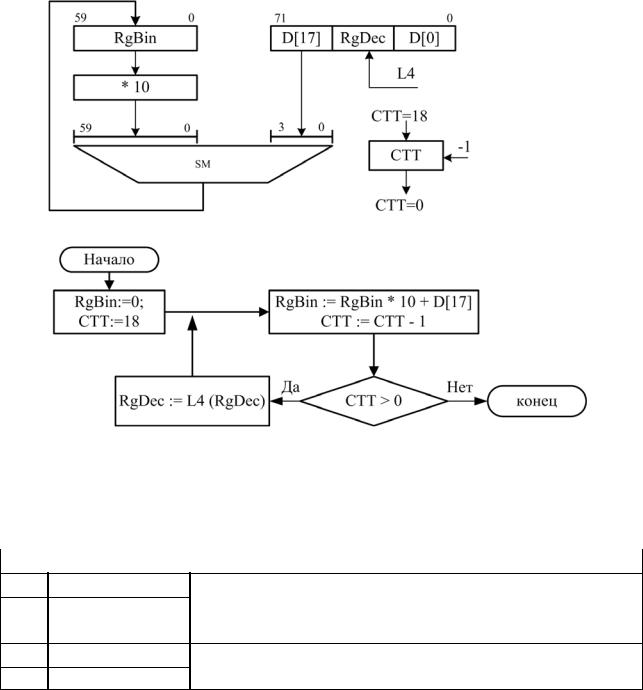

В преобразователе BCD-кода в двоичный имеются два регистра - десятичный RgDec и двоичный RgBin. Преобразование может выполняться путем последовательного умножения двоично-десятичного числа на 10. Двоичный код вычисляется по формуле:

17

B=(...((D[n]*10+d[n-1])*10+D[n-2])*10+...+D[1])*10+D[0],

где В - двоичное число, D[i] - тетрада i десятичного числа.

Десятичное число записано в 9-ти младших байтах W80 и содержит тетрады с D[17] по D[0]. Выделение очередной тетрады выполняется путем сдвига BCD-кода на 4 бита влево. Схема и алгоритм преобразования приведены на рис 3.5. Двоичный регистр RgBin содержит 60 битов, десятичный RgDec - 72 бита (18 тетрад). RgDec снабжен цепью сдвига на тетраду влево. В качестве RgDec могут использоваться биты 71-0 регистра W80. Счетчик тетрад СТТ служит для подсчета обработанных тетрад. Умножение на десять может выполняться путем сложения сдвинутого влево на 3 бита (умножение на 8) и на 1 бит (умножение на 2) кода RgBin.

3.3.4. Обратное преобразование вещественных чисел

Такое преобразование необходимо, если формат получателя ОТ или ДТ. Для формата РТ преобразование не требуется.

Рассмотрим порядок преобразования из формата РТ в формат ОТ:

1)проверить исходное данное на равенство нулю, в этом случае результатом будет код нуля, в формате ОТ;

2)вычесть из смещенного порядка Е разность смещений 16256; если

Е> 254, перейти к п. 6, если E < 1, перейти к п. 7;

3)проверить младшие отбрасываемые 40 бит мантиссы; если они не равны нулю, зафиксировать особый случай Р (потеря точности); если особый случай не замаскирован, перейти к обработчику прерывания, если замаскирован - продолжить преобразование;

4)округлить мантиссу до 24 бит в соответствии со значением поля RC; порядок округления описывается таблицей 3.2 где через r обозначен двоичный код в отбрасываемых битах мантиссы;

5)сдвинуть мантиссу на 1 бит влево и закончить преобразование;

6)зафиксировать особый случай переполнения O; если он не замаскирован, перейти к обработчику прерывания, если замаскирован - сформировать результат, равный наибольшему положительному или отрицательному числу, и закончить преобразование;

7)зафиксировать особый случай антипереполнения U; если он незамаскирован, перейти к обработчику прерывания, если замаскирован - продолжить преобразование;

8)если Е < 23, произвести денормализацию числа – сдвинуть мантиссу на Е битов вправо , округлить ее и установить Е = 0.

18

Рис.3.5. Схема и алгоритм преобразования десятичного кода в двоичный

Аналогичным образом происходит преобразование в формат ДТ с учетом разрядности порядка и мантиссы и величины смещения.

|

Округление результата |

Таблица 3.2 |

|

RC |

Режим |

|

Действие округления |

00 К ближайшему

10 Вверх

01 Вниз

11 Усечение

Если r < 1000, то отбросить младшие биты. Если старший отбрасываемый бит 1(r >= 1000), то прибавить 1 к младшему сохраняемому биту

При любом значении r отбрасываются младшие биты

3.3.5. Преобразование в целое

Преобразование начинается с проверки исходного числа в формате РТ на равенство нулю. В этом случае результат будет равен нулю. Если исходное число денормализовано (Е=0), результат будет нулевым (мантисса меньше единицы).

В случае преобразования нормализованных чисел переполнение фиксируется, если истинный порядок Е-16383>=r, где r - разрядность значащей части получателя (15, 31 или 63). При отсутствии переполнения мантисса сдвигается вправо на k разрядов, где k = r - (E - 16383). Значение k изменяется от 1 до r - 1. При r<63 младшие 64-r бит мантиссы

19

обнуляются. Если число отрицательное, оно преобразуется в дополнительный код.

Преобразование чисел из формата РТ в формат УПК (80dec)

происходит в два этапа. На первом происходит преобразование из 80real в 64int, как было описано выше, а на втором этапе происходит преобразование двоичного кода в двоично-десятичный. Разрядность r=60, т.к. двоичный код десятичного числа содержит не более 60 значащих разрядов.

В случае маскированного переполнения устанавливается код десятичной неопределенности FFFFUU...UH, где U - любая 16-ричная цифра. Проверку на переполнение можно выполнить до преобразования, сравнив двоичное целое с максимальным десятичным значением

99..9=DEFC74793E7FFFFH.

Преобразование двоичного кода в десятичный можно выполнить различными способами. Обычно используют метод последовательного умножения на 2 или "сдвиг-коррекцию". Преобразователь содержит регистры для десятичного и двоичного кодов , схему коррекции и счетчик циклов. Число циклов равно разрядности двоичного кода. Цикл состоит из двух тактов: совместный сдвиг регистров влево (удвоение) и коррекция десятичного кода. Для коррекции прибавляется число 6 к тетрадам, из которых была выдвинута единица, и к псевдотетрадам. Возможен вариант предварительной коррекции тетрад прибавлением числа 3 и последующего сдвига. Оба действия можно объединить в одном такте.

3.3.6. Обратное позиционирование

Порядок позиционирования зависит от формата данного, его исходного положения в слове W80 и младших битов адреса EAR[0:1]. Исходное положение данных в W80 описывается таблицей 3.3, а их размещение в W64 после позиционирования - таблицей 3.4.

Размещение данных |

Таблица 3.3 |

|||

в слове W80 |

|

|

|

|

Формат |

|

Знак |

Остальные |

|

|

|

|

биты |

|

m16int |

|

63 |

62:48 |

|

m32int |

|

63 |

62:32 |

|

m64int |

|

63 |

62:0 |

|

m32real |

|

79 |

71:41 |

|

m64real |

|

79 |

74:12 |

|

m80real |

|

79 |

78:0 |

|

m80dec |

|

79 |

78:0 |

|

Размещение данных в |

Таблица 3.4 |

|||

слове W64 |

|

|

|

|

EAR[0:1] |

11 |

10 |

01 |

00 |

|

|

|

|

|

m16 |

63:48 |

47:32 |

31:16 |

15:0 |

m32 |

- |

63:32 |

47:16 |

32:0 |

m64 |

- |

- |

- |

63:0 |

m80(1) |

63:48 |

63:32 |

63:16 |

63:0 |

m80(2) |

63:0 |

47:0 |

32:0 |

15:0 |

Примечание. Обозначения m80(1), m80(2) соответствуют первому и второму шагам сохранения данных формата m80.

20

Выборка битов из слова W80 для форматов m80real и m80dec на первом и втором шагах сохранения числа описывается таблицей 3.5.

Выборка битов из W80 |

|

Таблица 3.5 |

|||

EAR[0:1] |

11 |

10 |

01 |

|

00 |

Шаг 1 |

15:0 |

31:0 |

47:0 |

|

63:0 |

Шаг 2 |

79:16 |

79:32 |

79:48 |

|

79:64 |

Коммутация данных при передаче из W80 в W64 осуществляется с помощью мультиплексоров или программируемого сдвигателя. Управляет мультиплексорами или сдвигателем схема СУОП.

3.4. Блок регистров

Блок регистров БР (рис.3.6) включает в себя регистровый стек ST, регистр тэгов TW, регистр управления CW, регистр состояния SW, регистры 1-го и 2-го операндов RGA, RGB, схему СхАиМ анализа и модификации TW, CW и SW, схему сравнения и анализа операндов и 3- разрядный сумматор SM. Регистры операндов могут быть отнесены и к блоку обработки данных БОД.

Выборка из ST происходит по шинам А и В, запись - только по шине А. ST имеет адресные входы А=ТОР (адресует вершину стека) и В=ТОР+i (адресует регистр ST(i)). Чтение происходит по сигналу RD. Если при этом подан сигнал разрешения обращения к ST(i) EI=1, чтение происходит одновременно по обоим адресам. Запись происходит по сигналу WR в ST(0) при EI=0 и в ST(i) при EI=1.

Запись может производиться из регистров RGA и RGB, из блока преобразования форматов БПФ и из регистра результата БОД. Необходимый выбор осуществляется с помощью мультиплексора MX.