- •Введение.

- •Цели и задачи дисциплины.

- •Связь с другими дисциплинами и необходимый уровень подготовки.

- •Кодирование логической и двоичной информации электрическими сигналами.

- •Характеристики электрических сигналов.

- •Простейшие логические операции и их схемотехническая реализация (диодные схемы).

- •Ттл элемент, работа схемы, основные характеристики.

- •Разновидности логических элементов и серии интегральных микросхем.

- •Соединения логических элементов и радиокомпонентов.

- •Схемотехника функциональных устройств.

- •Схемотехника последовательностных устройств.

- •Триггеры.

- •Счётчики.

- •Двоичные счетчики.

- •Недвоичные счетчики.

- •Регистры.

- •Параллельные регистры.

- •Последовательные (сдвиговые) регистры.

- •Комбинационные устройства.

- •Дешифраторы.

- •Линейный дешифратор.

- •Матричный дешифратор.

- •Пирамидальный дешифратор.

- •Дешифраторы интегрального исполнения.

- •Мультиплексор и демультиплексор.

- •Мультиплексоры интегрального исполнения.

- •Сумматоры.

- •Одноразрядные комбинационные сумматоры.

- •Многоразрядные сумматоры.

- •Последовательный многоразрядный сумматор.

- •Параллельный многоразрядный сумматор.

- •Ускоренный перенос.

- •Арифметико-логическое устройство.

- •Устройства памяти.

- •Статические элементы оперативных запоминающих устройств.

- •Запоминающий элемент на биполярных транзисторах.

- •Запоминающий элемент на полевых транзисторах.

- •Динамический запоминающий элемент оперативных запоминающих устройств.

- •Запоминающие элементы пзу.

- •Организация бис зу.

- •Построение запоминающих устройств эвм.

- •Программируемые логические матрицы.

- •Формирователи.

- •Определение интервала времени по заданным уровням сигналов в цепях первого порядка.

- •Формирователи периодических сигналов.

- •Несимметричный мультивибратор на логических элементах.

- •Формирователь фронтов (спадов) — триггер Шмитта.

- •Формирователи импульсов.

- •Формирователь на интегрирующей rc цепи.

- •Одновибратор с дифференцирующей rc цепью.

- •Одновибраторы интегрального исполнения.

- •Интерфейсные устройства.

- •Буферные устройства.

- •Передача сигналов по линиям связи.

- •Несимметричные линии связи.

- •Согласование линий связи.

- •Симметричные линии связи.

- •Цифро-аналоговые и аналого-цифровые преобразователи.

- •Цифро-аналоговые преобразователи (цап).

- •Цифро-аналоговый преобразователь на суммировании токов.

- •Цифро-аналоговый преобразователь на матрице r-2r.

- •Аналого-цифровые преобразователи (ацп).

- •Параллельный ацп.

- •Ацп последовательного приближения (последовательные ацп).

- •Ацп двойного интегрирования.

- •Системы индикации.

- •Индикация состояния логического элемента.

- •Индикация состояния шин.

Комбинационные устройства.

Комбинационными устройствами называют такие у которых, состояние выходов в любой момент времени однозначно определяется состоянием входов. В этом разделе рассмотрим построение и работу следующих устройств: дешифраторы, мультиплексоры, сумматоры и арифметико-логические устройства.

Дешифраторы.

По способу схемотехнической реализации дешифраторы подразделяются на: линейные, матричные и пирамидальные.

Линейный дешифратор.

Дешифратор комбинационное устройство

с n входами и не более чем

![]() выходами, обеспечивающее для каждого

значения n-разрядного входного слова

появление активного сигнала только на

одном из к выходов. Если количество

выходов дешифратора определяется

соотношением

выходами, обеспечивающее для каждого

значения n-разрядного входного слова

появление активного сигнала только на

одном из к выходов. Если количество

выходов дешифратора определяется

соотношением![]() ,

то дешифратор называется полным. Если

разряды входного слова обозначим

,

то дешифратор называется полным. Если

разряды входного слова обозначим![]() ,

а выходы дешифратора ─

,

а выходы дешифратора ─![]() , то состояния выходов дешифратора

описываются системой уравнений:

, то состояния выходов дешифратора

описываются системой уравнений:

![]()

![]()

![]()

. . . . . . .

![]()

Система уравнений показывает, что для получения выходных переменных дешифратора нужно использовать элементы “И”, у которых количество входов определяется разрядностью входного слова, и количество таких элементов должно быть равно количеству уравнений.

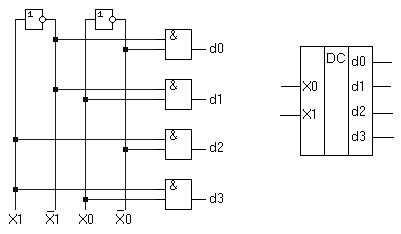

Рассмотрим на примере построение дешифратора для двухразрядного входного слова: n=2 и, следовательно, k=4. Уравнения дешифрации будут иметь вид:

![]()

![]()

![]()

![]()

Уравнения дешифрации показывают, что для построения схемы дешифратора необходимо четыре элемента 2И.

На рис. 54 приведена схема дешифратора для двухразрядного входного слова и изображение такого дешифратора на электрических схемах устройств ЭВМ. При построении схемы левее линейки элементов 2И проведены четыре линии, на которые подаются сами входные переменные (разряды входного слова) и их инверсии, т.е. используется парафазное представление информации. Соединение входов элементов 2И с входными переменными производится в соответствии с уравнениями дешифрации и соответственно выходы элементов, являющиеся выходами дешифратора, получают обозначения (d0 -- d3). В связи с тем, что основой такого дешифратора является линейка логических элементов его называют -- линейный дешифратор. Для уменьшения количества входов нужно перейти к однофазному представлению входной информации.

Рис. 54. Линейный дешифратор.

Схемотехнически это осуществляется

установкой инверторов между линиями

прямых и инверсных значений входных

переменных. Максимальное время задержки

прохождения сигнала через линейный

дешифратор

![]() .

Удобно при построении схемы дешифратора

использовать элементы И-НЕ, при этом

выходы дешифратора будут активны низким

уровнем. Однако построение линейных

дешифраторов ограничено максимальным

количеством входов элементов И.

Ограничение в возможности построения

линейных дешифраторов привело к

необходимости поиска других схемотехнических

решений для дешифраторов.

.

Удобно при построении схемы дешифратора

использовать элементы И-НЕ, при этом

выходы дешифратора будут активны низким

уровнем. Однако построение линейных

дешифраторов ограничено максимальным

количеством входов элементов И.

Ограничение в возможности построения

линейных дешифраторов привело к

необходимости поиска других схемотехнических

решений для дешифраторов.

Матричный дешифратор.

Матричный дешифратор относится к многоступенчатым дешифраторам. В первой ступени такого дешифратора используют несколько линейных дешифраторов. Во второй и остальных ступенях используют объединение выходов дешифраторов первой ступени по матричной схеме.

Рис. 55. Матричный дешифратор.

Рассмотрим построение матричного дешифратора на примере, возьмем разрядность входного слова пять --М=5. Для построения первой ступени входное слово разобьем на две части М1=2 и М2=3, тогда первая ступень будет состоять из двух линейных дешифраторов: один на два входа, а второй на три входа, соответственно у первого будет четыре выхода, а у второго -- восемь. Вторую ступень построим как матрицу совпадения выходов обоих дешифраторов первой ступени. На рис.55 это показано пересечением линий выходов дешифраторов D1 и D2, на каждом пересечении вертикальных и горизонтальных линий установлен элемент, выполняющий функцию 2И-НЕ (установка элемента показана в окружности). Общее количество пересечений 4*8=32, следовательно, матричный дешифратор будет иметь 32 выхода. На рисунке все, что обведено пунктирной линией, входит в матричный дешифратор. Имея в первой ступени дешифраторы с выходом активным высоким уровнем и используя во второй ступени элементы с инверсией, получаем матричный дешифратор с выходами активными низким уровнем. В рассмотренном примере получили двухступенчатый дешифратор, это объясняется тем, что в первой ступени имеем всего два линейных дешифратора. Если в первой ступени будет три дешифратора, то выходы двух из них образуют вторую ступень, а выходы второй ступени и третьего дешифратора первой ступени образуют третью ступень. Входное слово можно разбивать на группы самыми разными способами, но это приводит к использованию различного количества логических элементов, поэтому эта схема построения дешифраторов подлежит оптимизации по количеству используемых при построении дешифратора элементов.

Основным недостатком рассмотренных дешифраторов является разнообразие элементной базы, что не позволяет использовать эти дешифраторы в интегральных конструкциях. С целью упрощения и удешевления конструкций дешифраторов в различных интегральных применениях был разработан пирамидальный дешифратор.

Лекция 19.