Лабораторная работа 5 ПЛИС

.docxПечаткин С. В. 10В2

Лабораторная работа №5

Реализация проекта и подготовка файла конфигурации

Цель работы: ознакомление с основными этапами реализации проекта и средствами подготовки файла конфигурации

Выполнение работы:

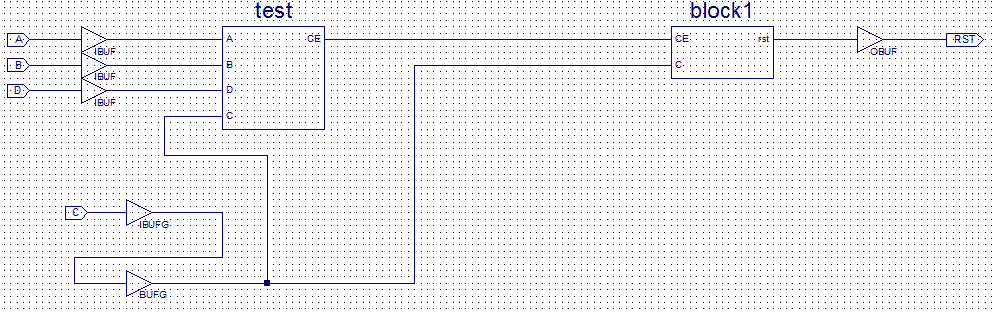

Рисунок 5.1. Подключение входов и выходов схемы к контактам ПЛИС

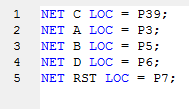

Рисунок 5.2. Описание подключений контактов схемы к контактам микросхемы

Отчет о синтезе:

=========================================================================

* Final Report *

=========================================================================

Final Results

RTL Top Level Output File Name : general_sch.ngr

Top Level Output File Name : general_sch

Output Format : NGC

Optimization Goal : Speed

Keep Hierarchy : NO

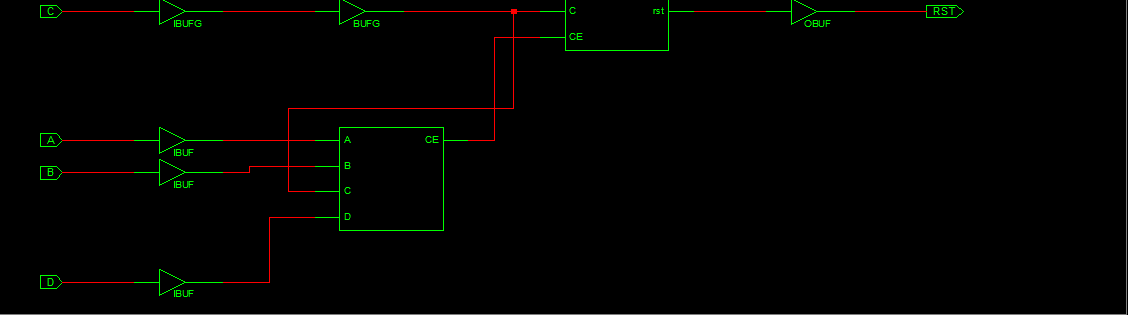

Design Statistics

# IOs : 5

Cell Usage :

# BELS : 28

# AND2 : 5

# AND3 : 2

# AND4 : 4

# AND5 : 1

# GND : 1

# INV : 5

# OR2 : 1

# VCC : 1

# XOR2 : 8

# FlipFlops/Latches : 10

# FD : 2

# FDCE : 8

# Clock Buffers : 1

# BUFG : 1

# IO Buffers : 5

# IBUF : 3

# IBUFG : 1

# OBUF : 1

# Others : 3

# FMAP : 3

=========================================================================

Рисунок 5.3. Результат синтеза на уровне RTL

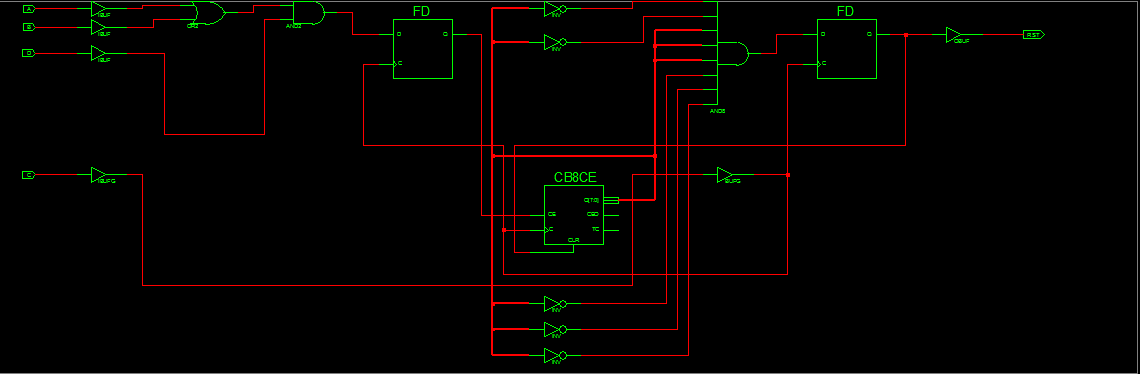

Рисунок 5.4. Результат синтеза технологическом уровне

Release 10.1 ngdbuild K.31 (nt)

Copyright (c) 1995-2008 Xilinx, Inc. All rights reserved.

Command Line: D:\Xilinx\10.1\ISE\bin\nt\unwrapped\ngdbuild.exe -ise

D:/P01/P01.ise -intstyle ise -dd _ngo -nt timestamp -i -p xc2s15-vq100-6

general_sch.ngc general_sch.ngd

Reading NGO file "D:/P01/general_sch.ngc" ...

Reading in constraint information from 'constr.ucf'...

Gathering constraint information from source properties...

Done.

Resolving constraint associations...

Checking Constraint Associations...

Done...

Checking Partitions ...

Checking expanded design ...

Partition Implementation Status

-------------------------------

No Partitions were found in this design.

-------------------------------

NGDBUILD Design Results Summary:

Number of errors: 0

Number of warnings: 0

Total memory usage is 104784 kilobytes

Writing NGD file "general_sch.ngd" ...

Writing NGDBUILD log file "general_sch.bld"...

Рисунок 5.5. Отчет о трансляции

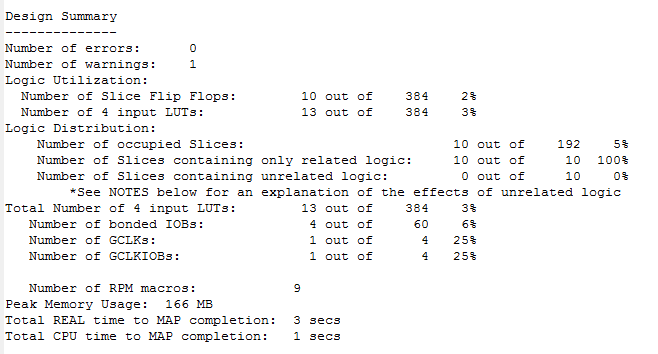

Рисунок 5.6 – Отчет об отображении. Раздел Design Summary

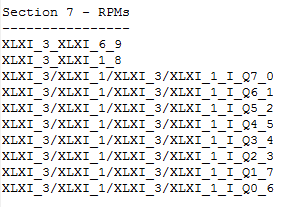

Рисунок 5.7. - Отчет об отображении. Раздел RPMs

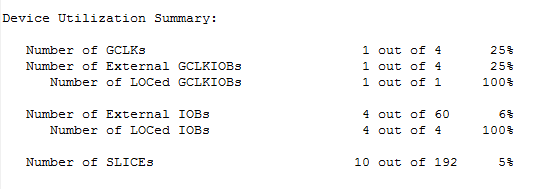

Рисунок 5.8. - Отчет о размещении и трассировки. Раздел Device Utilizatiom Summary

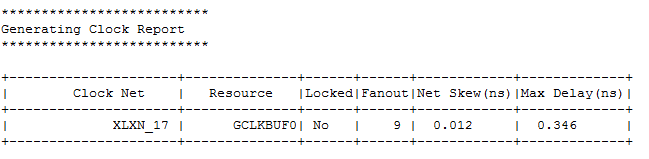

Рисунок 5.9. - Отчет о размещении и трассировки. Раздел Generating Clock Report

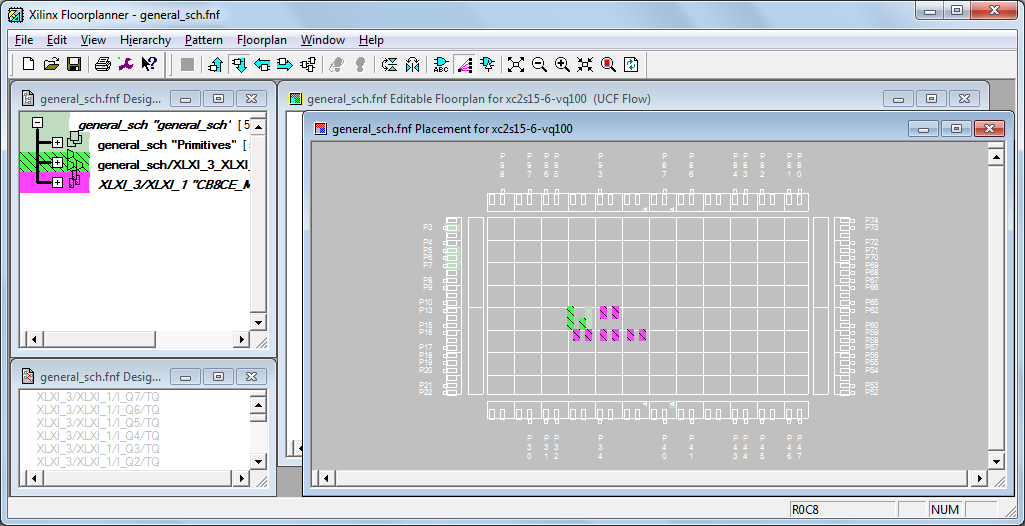

Рисунок 5.10. - Скриншот программы Floorplanner

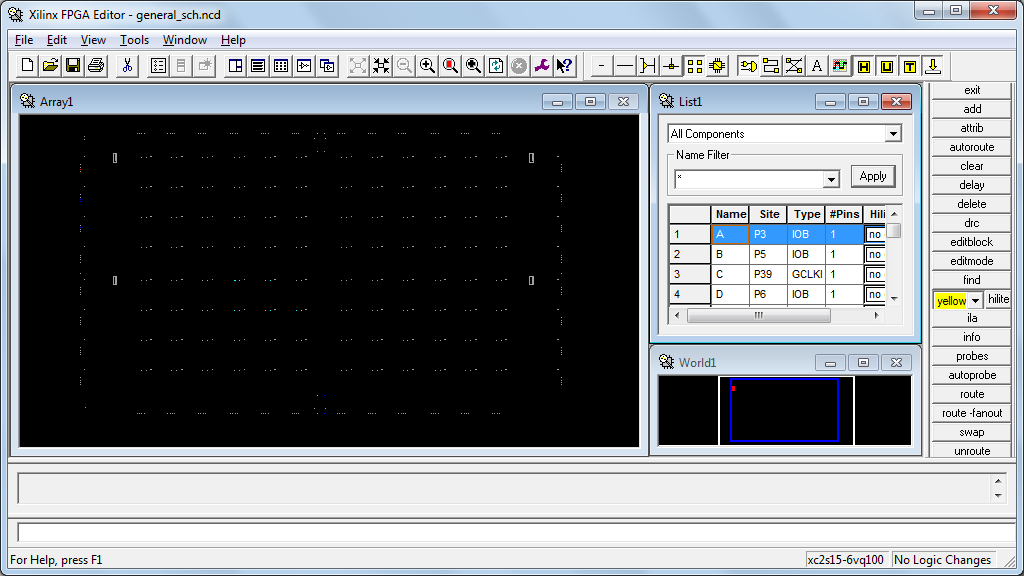

Рисунок 5.11. - Скриншот программы FPGA Editor

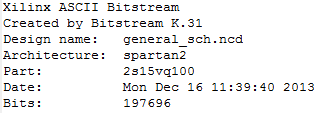

Рисунок 5.13 – Скриншот файла shema_top.rbt

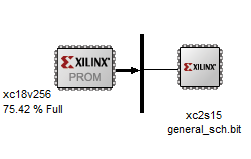

Рисунок 5.14- Конфигурационная цепочка