КУРС лекций Электротехника, электронное / Курс лекций. Электротехника и электроника. РАЗДЕЛ 4. Электроника

.pdf

363

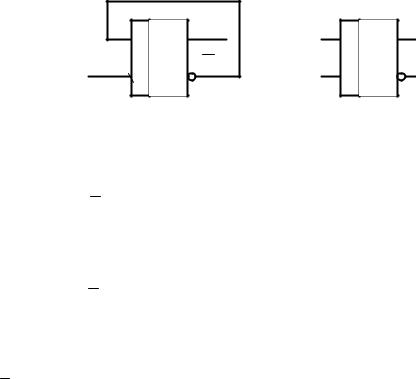

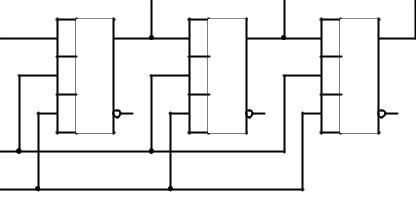

а б

Рисунок 18 – Тактовый триггер: а – на основе D-триггера; б – условное

обозначение

Рассмотрим его работу. Пусть первоначально D-триггер находится в состоянии: Q =0, Q=D =1. На вход С поступают следующие с некоторой час- тотой импульсы.

Тогда, после прихода первого же спада импульса от 1 до 0 на вход С, информация со входа D=1 перепишется в триггер и на его выходах возникнет

состояние: Q =1, Q=D =0. После этого триггер будет готов к следующему пе- реключению.

После прихода следующего спада импульса на вход С, информация со входа D=0 перепишется в триггер и на его выходах возникнет состояние

Q =0, Q=D =1.

Процесс будет повторяться далее по тому же алгоритму. В результате на выходе триггера будут формироваться импульсы с частотой вдвое ниже частоты входного сигнала.

Обычно, кроме тактового входа Т, Т-триггеры имеют вход R для уста- новки триггера в нулевое исходное состояние. В этом состоянии при R=1 на прямом выходе триггера Q = 0 - логический нуль. Вход R, как правило, имеет приоритет. Это означает, что пока на входе R действует логическая 1 триггер не реагирует на импульсы поступающие на счетный вход Т и начинает рабо- тать, только после подачи на вход R логического нуля.

Т-триггеры применяют для деления частоты, в счетчиках импульсов и других устройствах.

4.7.4 Делитель частоты на триггерах. Счетчик импульсов

Счетчики импульсов - непременные узлы электронных часов, микро- калькуляторов, частотомеров и многих других приборов и устройств цифро- вой техники. Основой их служат триггеры со счетным входом.

Счетчиками в цифровой технике называются специальные элементы, позволяющие подсчитывать число поступивших на вход импульсов. Понятие

«счетчик импульсов» тесно связано с понятием «делитель частоты». По сути дела, это одно и то же устройство. Но рассмотрим все по порядку.

В качестве простейшего делителя/счетчика частоты может выступать рассмотренный выше тактовый триггер. Для того, чтобы этот триггер работал как делитель, нужно на вход R подать низкий логический уровень. Теперь,

364

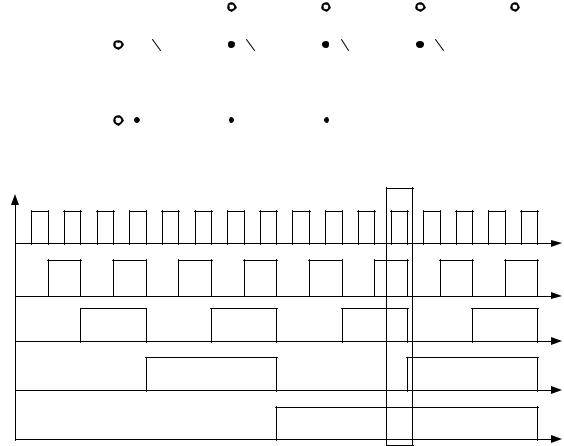

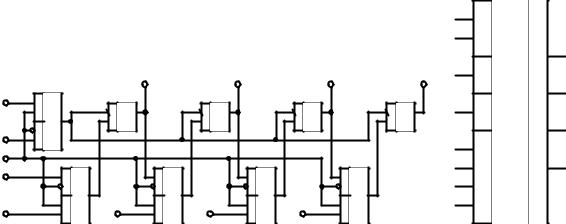

если на вход С подать импульсный сигнал некоторой постоянной частоты, то по спаду каждого входного импульса триггер будет переключаться в проти- воположное состояние. Если делитель частоты снабдить выходами после ка- ждого триггера, как показано на рисунке 19,а, то получим счетчик импульсов.

Один триггер считает до двух, два соединенных последовательно счи-

тают до четырех, п триггеров - до 2n импульсов.

Работа цепочки из 4-х таких триггеров показана на рисунке 19.

Врезультате на выходе каждого Т-триггера мы получим другой сигнал

счастотой следования импульсов в два раза меньшей, чем частота импульсов на его входе. Как видно из рисунка, период сигнала на выходе каждого триг- гера делителя ровно в два раза больше периода входного сигнала. А частота выходного сигнала, соответственно, в два раза ниже входного. Если частота сигнала на входе равна f, то на выходах делителя мы получим сигналы со сле- дующими частотами:

Q0 — f/2; |

Q1 —f/4; |

|

Q2 —f/8; |

|

|

Q3 — f/16. |

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

|

|

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

Uвх |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

б |

|

|

|

|

|

|

|

|

Рисунок 19 – Двоичный счетчик импульсов: а – схема; б – диаграмма работы |

|||||||||||||||

Анализируя одновременно состояние выходов счетчика, можно опре- делить, сколько импульсов прошло в счетчик.

365

Таким образом, состояние выходов характеризует число, записанное в

счетчик. Если каждому выходу присвоить свой вес: Q1 =1; |

Q2 = 2 ; Q3 = 4 ; |

Q4 = 8 , то число импульсов, пришедшее на вход счетчика можно определить |

|

N =1 Q1 + 2 Q2 + 4 Q3 +8 Q4 . |

(1) |

Например, на рисунке 19, б выделенное состояние выходов счетчика дает число

N =1 1+ 2 1 + 4 0 +8 1 =11.

Но линейки Т-триггеров могут образовывать только двоичные счетчи- ки, то есть такие, которые имеют максимальную емкость N max равную

N max = 2n , |

(2) |

где n - число триггеров в цепочке.

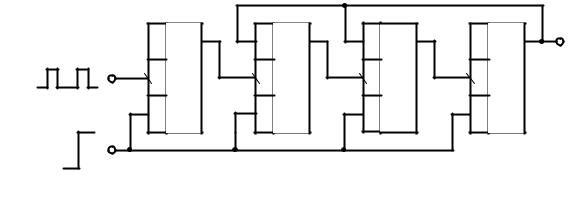

Для построения счетчика имеющего другой коэффициент счета, напри- мер 10, используются обратные связи, как показано на рисунке 20. Для этого Т-триггера счетчика должны иметь асинхронный вход S . При подаче на этот вход логической 1, триггер устанавливается в положение 1.

Рисунок 20 – Десятичный счетчик

Благодаря обратным связям, в схеме на рисунке 20, с поступлением 8-го импульса на выходе Т4 появится логическая 1, которая переведет триггеры Т2 и Т3 так же в состояние логической 1. Девятый импульс переводит Т1 в со- стояние 1 и все триггеры счетчика оказываются в состоянии логической 1. Десятый импульс устанавливает все триггеры в логический 0 и счет начинает- ся снова.

В данном случае, благодаря обратным связям, состояние счетчика про- скакивают позиции с 9-го по 13-й импульс, оказываясь после 8-го импульса в 14-й позиции счета.

Обратные связи могут быть и другими. Выпускается широкая номенк- латура как ТТЛ, так и КМОП счетчиков.

Результат счета формируется в заданном коде, который может хранить- ся в памяти счетчика или быть считанным другим устройством цифровой техники - дешифратором.

366

Контрольные вопросы

1.Цифровые микросхемы. Аналоговые и цифровые сигналы.

2.Цифровые коды. Двоичный код. Преимущества цифровых систем пе- ред аналоговыми схемами.

3.Логические элементы: повторитель, инвертор, элементы И, И-НЕ, ИЛИ и ИЛИ-НЕ. Элемент исключающее ИЛИ.

4.Микросхемы ТТЛ. Схемы внутреннего устройства. Принцип работы. Основанные характеристики.

5.Микросхемы КМОП. Схемы внутреннего устройства. Принцип рабо- ты. Основанные характеристики.

6.Триггеры: RS - триггер; D - триггер; Т – триггер. Логика работы, примеры применения.

7.Делитель частоты на триггерах.

8.Двоичный счетчик импульсов.

9.Применение обратных связей в цепочке триггеров для получения де- сятичного счетчика.

367

Лекция 4.8 Регистры. Преобразователи кода. Мультиплексоры и демультиплексоры. Ключи. Индикаторы

План лекции

1)Регистры.

2)Преобразователи кодов

3)Мультиплексоры и демультиплексоры.

2)Ключи КМОП.

4)Устройства отображения информации. Индикаторы: жидкокри- сталлические; светодиодные; вакуумно-люминисцентные. Схемы включе- ния и принципы управления.

4.8.1Регистры

Назначение регистров – хранение и преобразование многоразрядных

двоичных чисел.

Наряду со счетчиками – это наиболее распространенное устройство цифровой техники. Регистры используются в качестве управляющих и запо- минающих устройств, генераторов и преобразователей кодов, счетчиков, де- лителей частоты, узлов временной задержки.

Основой построения регистров являются синхронные D-триггеры, RS- триггеры.

Как отмечалось, одиночный триггер может запоминать один разряд (бит) двоичной информации. Такой триггер можно считать одноразрядным регистром. Для работы с многоразрядными числами используются цепочки триггеров – по количеству разрядов числа.

Занесение информации в регистр называют операцией ввода или запи- си. Выдача информации – операция вывода или считывания.

Понятие «весовой коэффициент» к разрядам регистра в отличие от счетчика неприменимо, поскольку весовая зависимость между отдельными разрядами целиком определяется записанной в регистр информацией. По этой причине на условных изображениях регистров нумерация меток информаци- онных входов и выходов идет подряд.

Все регистры делят на две большие категории:

-накопительные (регистры памяти, хранения);

-сдвигающие.

В свою очередь, сдвигающие регистры делятся:

-по способу ввода и вывода информации на следующие типы:

-параллельные, последовательные и комбинированные (параллельно- последовательные и последовательно-параллельные);

-по направлению передачи (сдвига) информации - однонаправленные и реверсивные.

368

Регистры памяти

Регистры памяти — простейший вид регистров. Их назначение— хра- нить двоичную информацию небольшого объема в течение короткого проме- жутка времени. Эти регистры представляют собой набор синхронных тригге- ров, каждый из которых хранит один разряд двоичного числа.

Ввод (запись) и вывод (считывание) информации производится одно- временно во всех разрядах параллельным кодом.

Ввод обеспечивается тактовым командным импульсом. С приходом очередного тактового импульса происходит обновление записанной инфор- мации. Сигналы на выходах триггеров характеризуют выходную информа- цию. Считывание может производиться в прямом или в обратном коде (в по- следнем случае — с инверсных выходов).

Регистры хранения представляют собой, по существу, наборы тригге- ров с независимыми информационными входами и обычно общим тактовым входом. В качестве регистров подобного рода могут быть использованы без дополнительных элементов многие типы синхронных триггеров.

Особенно пригодны микросхемы, содержащие в одном корпусе не- сколько самостоятельных триггеров, например: К155ТМ8, К155ТМ5, К155ТМ7, 564ТМЗ, 555ТМ8 и другие, которые можно рассматривать, как че- тырехразрядные регистры памяти.

Типичный пример применения регистра памяти — это промежуточное запоминание показаний счетчика на время отсчета. Например микросхема К155ТМ5 содержит четыре D -триггера со статическим управлением, рису- нок 1, а.

К десятичному счетчику |

дешифраторам индикатора |

|

К |

а  б

б

Рисунок 1 – Микросхемы регистров памяти: а – 4-х разрядный регистр на

Рисунок 1 – Микросхемы регистров памяти: а – 4-х разрядный регистр на

К155ТМ5; б – 4-х разрядный регистр хранения информации К155ИР15

369

При С=0 изменения сигналов на входах D не влияют на состояние триг- геров регистра, он хранит записанную ранее информацию. При С=1, триггер превращается в повторитель и сигналы на выходах соответствует сигналам на входах соответствующих триггеров. При С=0 триггер вновь переходит в ре- жим хранения, а его состояние определяется сигналами на входах D перед спадом импульса на входе С.

Наращивание разрядности регистров памяти достигается добавлением нужного числа триггеров, тактовые входы которых присоединяют к шине синхронизации.

Регистр хранения типа К155ИР15 может служить примером устройства с тремя выходными состояниями. Он состоит (рисунок 1,б) из четырех D- триггеров с независимыми информационными входами (D1 - D4) и общим синхронизирующим входом С. Выходы триггеров Ql - Q4 - прямые.

Имеются также два равноценных разрешающих входа E1 и Е2, вход установки нулей R и два EZ1 и EZ2 для перевода микросхемы в третье со- стояние (с высокоимпедансным выходом).

Параллельный ввод информации в триггеры с входов D1 - D4 происхо- дит по фронту 0,1 тактовых импульсов. При этом на обоих разрешающих входах Е1 и Е2 и на входе установки нулей R должны быть уровни логиче- ского нуля.

Если к моменту прихода тактового импульса на одном или обоих вхо- дах Е1 и Е2 действует уровень логической 1, то триггеры регистра хранят предыдущую информацию.

С приходом высокого потенциала на вход R происходит одновременно сброс показаний (установка нулей) независимо от состояния остальных вхо- дов.

Отличительная особенность микросхемы — наличие буферных каска- дов на выходе, управление которыми осуществляется по двум входам EZ1 и EZ2. Когда оба входа находятся под нулевым потенциалом, информация, за- писанная в регистр, присутствует на выходных выводах Qi. Если на одном или обоих входах EZ существует высокий потенциал, то все выходы отклю- чены (находятся в Z - состоянии). Действие выходных буферов не связано с остальными элементами. Перепады напряжения на входах EZ не отражаются на работе триггеров.

Сдвигающие (последовательные) регистры

Основную массу регистров, используемых на практике, представляют регистры сдвига. Этот вид регистров отличается большим разнообразием, как в функциональном отношении, так и в отношении схемных решений, времен- ных параметров, емкости и т. п.

Регистры сдвига, помимо операции хранения, осуществляют преобра- зование последовательного двоичного кода в параллельный, а параллельного

370

— в последовательный. Они могут выполнять арифметические и логические операции, служат в качестве цифровых элементов временной задержки и т.д.

Своим названием они обязаны характерной для этих устройств опера- ции сдвига. Сущность сдвига состоит в том, что с приходом каждого тактово- го импульса происходит перезапись (сдвиг) содержимого триггера каждого разряда в соседний разряд без изменения порядка следования единиц и нулей.

При сдвиге информации вправо после каждого тактового импульса бит из более старшего разряда сдвигается в младший, а при сдвиге влево — на- оборот.

На схемах символом регистра служат буквы RG. Для регистров сдвига указывается также направление сдвига: (→) вправо; (← ) влево; (↔) ревер- сивный (двунаправленный).

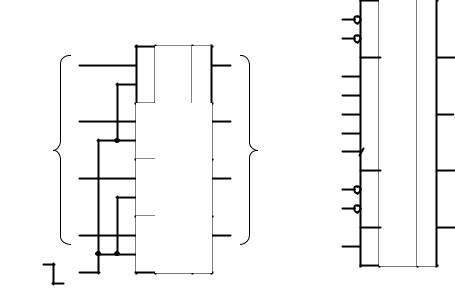

Посмотрим на структуру регистра сдвига на D-триггерах, рисунок 2.

Рисунок 2 - Регистр сдвига на D-триггерах

Как видно из рисунка, в регистре сдвига также объединяются входы R и C триггеров. Перед записью информации регистр устанавливается в нулевое состояние. Информация подается на D-вход первого триггера. При подаче импульса на вход С бит информации (логический 0 или логическая 1) записы- вается в триггер. При подаче следующего импульса этот бит записывается в следующий триггер. При этом в первый триггер записывается следующий бит информации и т. д. Другими словами, при воздействии тактовых импульсов информация продвигается по регистру от первого триггера к последнему. При заполнении всех триггеров число в параллельном коде можно вывести с вы- ходов Q0 - Q2. При этом первый бит информации будет присутствовать на выходе Q2, второй - на выходе Q1 и т. п.

Показанный на рисунке регистр сдвигает информацию только в одну сторону. Такие регистры называют регистром со сдвигом вправо или регистр со сдвигом влево (смотря, куда он сдвигает).

Существуют регистры, сдвигающие информацию в обе стороны. На- правление сдвига в таких регистрах определяется управляющим сигналом, подаваемым на специальный вход (подобно реверсивным счетчикам.)

371

Регистры сдвига как готовые изделия производятся в нескольких сериях микросхем ТТЛ и КМОП. Рассмотрим, в качестве примера, регистр сдвига К155ИР1 (ТТЛ).

Микросхема К155ИР1 представляет собой четырехразрядный регистр сдвига с последовательным или параллельным вводом информации и парал- лельным выводом ее.

Микросхема может быть использована в качестве буферной памяти, элемента задержки на несколько тактов, преобразователя' последовательных кодов в параллельные и наоборот, делителя частоты, кольцевого распредели- теля импульсов, элемента арифметических устройств и т. п.

Регистр может выполнять следующие операции:

-ввод информации параллельным кодом;

-сдвиг информации вправо;

-ввод информации последовательным кодом;

-сдвигом информации влево;

-хранение данных.

Условное изображение регистра К155ИР1 показано на рисунке 3, а. Там же (рисунок 3, б) показана его упрощенная функциональная схема.

Регистр имеет два тактовых входа С1 и С2, управляющий вход выбора режима V2, пять информационных входов (V1 для ввода информации в по- следовательном коде и четыре входа D1 - D4 для записи информации в па- раллельном коде), а также четыре выхода Ql - Q4 с каждого разряда регистра.

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

C1 |

RG |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

12 |

|

|

8 |

|

|

Q1 |

13 |

|

Q2 |

12 |

|

Q3 |

11 |

Q4 |

10 |

|

Q2 |

|

C1 |

& 1 |

|

|

|

|

|

|

|

|

|

|

1 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

C T |

|

C T |

|

C T |

|

C T |

I |

|

|

|||||

|

|

|

|

|

|

|

|

11 |

||||||||

C2 |

9 |

& |

D |

|

|

D |

|

|

D |

|

|

D |

2 |

|

Q3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V |

6 |

|

|

|

|

|

|

|

|

|

|

|

3 |

D1 |

|

10 |

1 |

|

|

|

|

|

|

|

|

|

|

|

D2 |

Q4 |

|||

I |

|

& 1 |

|

|

& 1 |

|

|

& 1 |

|

|

& 1 |

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

5 |

D3 |

|

|

|

2 |

& |

|

3 |

& |

|

4 |

& |

|

5 |

& |

|

D4 |

|

|

|

D1 |

D2 |

D3 |

D4 |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

||||||||

|

U п – 14 , общ . - 7 |

а |

б |

Рисунок 3 – Регистр сдвига К155ИР1: а - схема регистра сдвига К155ИР1; б – условное обозначение

Этот регистр содержит четыре тактируемых фронтом D-триггера, соединенных последовательно с помощью ячеек И-ИЛИ.

Если на вход V (вывод 6) регистра подан нулевой потенциал, то вы- ход каждого предыдущего триггера оказывается соединенным через ячей- ку И-ИЛИ со входом D последующего. При этом импульсы, приходящие

372

на тактовый вход C2, будут каждый раз устанавливать последующий триг- гер в состояние, в котором до этого находился предыдущий. Таким обра- зом, осуществляется сдвиг информации вправо.

Вход I регистра, связанный со входом D первого триггера, служит для приема информации в виде последовательного кода. С каждым такто- вым импульсом на этот вход должен подаваться код нового разряда вход- ной информации. После приема четырех разрядов последовательного кода соответствующий параллельный код может быть получен с выходов триг- геров Q1 - Q4.

Запись параллельного кода в регистр идет по входам D1 - D4 при по- даче высокого потенциала на вход V и тактового импульса на вход C1. Ус- танавливая затем V=0 и подавая тактовые импульсы на вход С2, мы обес- печим сдвиг записанного кода. При этом с выхода Q4 последнего триггера снимается последовательный выходной код.

Иногда требуется производить в регистре сдвиг информации как вправо, так и влево. В рассматриваемом устройстве такая возможность по- является, если попарно соединить выводы Q4 и D3, Q3 и D2, Q2 и D1. Вход V в этом случае будет играть роль переключателя направления сдви- га: если V=1, то тактовые импульсы С1 сдвигают информацию влево, а вход D4 служит для приема последовательного кода; если же V=0, то, как указывалось выше, импульсы С2 будут сдвигать информацию вправо.

4.8.2 Преобразователи кодов

Преобразователи кодов служат для перевода одной формы числа в другую. Их входные и выходные переменные однозначно связаны между собой. Эту связь можно задать таблицами переключений или логическими функциями. Примерами таких устройств служат шифраторы и дешифрато- ры. Преобразователи кодов обозначают через X/Y.

Шифратор (кодер) - (англ. encoder) логическое устройство, выпол- няющее логическую операцию - преобразование позиционного n-разряд- ного кода в m-разрядный двоичный, троичный или k-ичный код.

Например, десятичный шифратор – устройство, преобразующее де- сятичные числа в двоичную систему счисления, причем каждому входу может быть поставлено в соответствие десятичное число, а набор выход- ных логических сигналов соответствует определенному двоичному коду. Шифратор иногда и используют, например, для перевода десятичных чи- сел, набранных на клавиатуре кнопочного пульта управления, в двоичные числа.

Если количество входов настолько велико, что в шифраторе исполь- зуются все возможные комбинации сигналов на выходе, то такой шифра- тор называется полным, если не все, то неполным. Число входов и выходов в полном шифраторе связано соотношением