- •Архитектура вычислительных систем. Вычислительные машины, системы и сети

- •1. Основные понятия вычислительной техники и принципы организации вычислительных систем

- •1.1. Основные понятия и определения

- •1.2. Принципы организации вычислительных машин и систем

- •1.3. Основные характеристики вычислительных машин и систем

- •1.4. Многоуровневая организация вычислительных процессов

- •Вопросы для самопроверки

- •2. Простейшие типовые элементы вычислительных машин

- •2.1. Комбинационные схемы

- •1. Конъюнкция (логическое умножение) .

- •2. Дизъюнкция (логическое сложение) .

- •3. Отрицание (инверсия) .

- •4. Конъюнкция и инверсия (Штрих Шеффера) .

- •5. Дизъюнкция и инверсия (Стрелка Пирса) .

- •6. Эквивалентность .

- •7. Отрицание эквивалентности .

- •2.2. Автоматы с памятью

- •2.3. Триггеры

- •2.4. Проблемы и перспективы развития элементной базы вычислительных машин

- •Вопросы для самопроверки

- •3. Функциональные узлы комбинационного и последовательного типов

- •3.1. Функциональные узлы последовательного типа

- •3.1.1. Регистры

- •3.1.2. Счётчики

- •3.1. Функциональные узлы комбинационного типа

- •3.2.1 Шифраторы и дешифраторы

- •3.2.2 Компараторы

- •3.2.3 Сумматоры

- •Вопросы для самопроверки

- •4. Функциональная организация процессора

- •4.1. Основные характеристики и классификация процессоров

- •4.2. Физическая и функциональная структура процессора

- •4.2.1 Операционное устройство процессора

- •4.2.2 Шинный интерфейс процессора

- •4.3. Архитектурные принципы организации risc-процессоров

- •4.4. Производительность процессоров и архитектурные способы её повышения

- •Вопросы для самопроверки

- •5. Организация работы процессора

- •5.1 Классификация и структура команд процессора

- •5.2. Способы адресации данных и команд

- •5.2.1 Способы адресации данных

- •5.2.2 Способы адресации команд

- •5.3. Поток управления и механизм прерываний

- •Вопросы для самопроверки

- •6 Современное состояние и тенденции развития процессоров

- •6.1. Архитектурные особенности процессоров Pentium

- •6.2. Программная модель процессоров Pentium

- •6.2.1. Прикладная программная модель процессоров Pentium

- •6.2.2. Системная программная модель процессоров Pentium

- •6.2.3. Система команд и режимы адресации процессоров

- •6.3. Аппаратная организация защиты в процессорах Pentium

- •6.4. Аппаратные средства поддержки многозадачности

- •6.5. Перспективы развития процессоров

- •Вопросы для самопроверки

- •7. Память. Организация памяти

- •7.1. Иерархическая организация памяти

- •7.2. Классификация запоминающих устройств

- •7.3. Структура основной памяти

- •7.4. Память с последовательным доступом

- •7.5. Ассоциативная память

- •7.6. Организация флэш-памяти

- •7.7. Архитектурные способы повышения скорости обмена между процессором и памятью

- •Вопросы для самопроверки

- •8. Управление памятью. Виртуальная память

- •8.1. Динамическое распределение памяти

- •8.2. Сегментная организация памяти

- •8.3. Страничная организация памяти

- •8.4. Сегментно-страничная организация памяти

- •Вопросы для самопроверки

- •9. Организация ввода-вывода информации. Системная шина

- •9.1. Организация шин. Системная шина

- •9.1.1. Структура системной шины

- •9.1.2. Протокол шины

- •9.1.3. Иерархия шин

- •9.2 Организация взаимодействия между периферийными устройствами и процессором и памятью вычислительных машин

- •9.3. Внешние интерфейсы вычислительных машин

- •9.3.1. Параллельный порт lpt и интерфейс Centronics

- •9.3.1. Последовательный порт com и интерфейс rs-232c

- •9.3.3. Универсальная последовательная шина usb

- •9.3.4. Беспроводные интерфейсы

- •Вопросы для самопроверки

- •Модуль 2. Вычислительные системы

- •10. Вычислительные системы параллельной обработки. Многопроцессорные и многоядерные системы

- •10.1. Параллельная обработка информации

- •10.2. Классификация систем параллельной обработки данных

- •10.2.1 Классификация Флинна

- •10.2.2. Классификация Головкина

- •10.2.3. Классификация многопроцессорных систем по

- •10.3. Вычислительные системы на кристалле. Многоядерные системы

- •10.4. Тенденции развития вс

- •Вопросы для самопроверки

- •11. Организация микроконтроллеров и микроконтроллерных систем

- •11.1. Общие сведения о системах управления

- •11.2. Организация микроконтроллеров и микроконтроллерных систем

- •11.3. Области применения и тенденции развития мк

- •Вопросы для самопроверки

- •Модуль 3. Телекоммуникационные сети

- •12. Организация компьютерных сетей

- •12.1. Обобщённая структура компьютерных сетей

- •12.2. Классификация компьютерных сетей

- •Вопросы для самопроверки

- •13. Стандартизация компьютерных сетей. Эталонная модель взаимодействия открытых систем

- •13.1. Понятие «открытой системы». Взаимодействие открытых систем

- •13.2. Эталонная модель взаимодействия открытых систем

- •13.3. Структура блоков информации

- •7. Прикладной6. Представительный5. Сеансовый4. Транспортный3. Сетевой2. Канальный1. Физический

- •Вопросы для самопроверки

- •Литература

- •Архитектура вычислительных систем. Вычислительные машины, системы и сети

5.2. Способы адресации данных и команд

5.2.1 Способы адресации данных

Способы адресации данных определяют механизмы вычисления эффективных адресов операндов в памяти и доступа к операндам. Выделяют следующие способы (режимы) адресации [2, 6]:

1.Непосредственный. Позволяет задавать фиксированные значения операнда непосредственно в адресной части команды, т.е., искомое значение является частью команды (рис. 27). Такой режим адресации удобен при работе с константами.

Рис. 27 . Непосредственная адресация

Примеры: mov ax, 5564h

mov ah, ‘A’

add al, 1101001100b

Следует помнить, что непосредственный операнд может быть задан только как операнд-источник. Недостатком непосредственной адресации является необходимость расширения формата команд за счёт указания самого операнда в адресном поле команды.

2. Прямой. Адрес операнда содержится в коде команды (рис. 28). Используется при работе с переменными и константами, местоположение которых в памяти не меняется в процессе выполнения задачи.

Рис. 28. Прямая адресация

Таким образом, в коде команды указывается смещение операнда в памяти.

Пример: d_s segment

mm dw 3154h

d_s ends

c_s segment

assume ds:d_s, cs:c_s

begin:

…

mov ax, mm ;по адресу mm пересылается 3154h

…

c_s ends

end begin

После выполнения третьей команды в регистре ax будет записано значение по адресу mm в памяти, т.е., число 3154h.

3. Регистровый. Искомое значение операнда содержится в определённом командой регистре, т.е., в адресном поле команды указывается адрес регистра.

Примеры: mov ax, cx

add ah, al

Регистровую адресацию легко отличить от всех остальных по тому признаку, что все операнды команд являются регистрами. Такие команды являются наиболее компактными и выполняются быстрее других типов команд, поскольку отсутствуют обращения к памяти.

4. Регистровый косвенный. Является частным случаем косвенной адресации, когда адрес, указываемый в команде, является указателем ячейки, содержащей смещение операнда в памяти (рис. 29).

Фактически в команде указывается адрес адреса, причём в качестве регистра адреса может выступать базовый регистр BP или индексные регистры SI или DI.

Косвенная адресация является более эффективной, чем прямая, поскольку в адресном поле команды указывается только адрес регистра, который короче полного адреса операнда в памяти. Однако при этом режиме адресации требуется предварительная загрузка регистра косвенным адресом памяти, на что расходуется дополнительное время.

Пример: mov ax, [si]

Если в регистре si содержится 10, то в регистр ax будет помещено значение, находящееся по смещению 10 в сегменте данных.

Рис. 29. Косвенная адресация

Косвенную адресацию удобно использовать при решении задач, когда оставляя неизменным адрес регистра в команде, можно изменять содержимое ячейки с этим адресом.

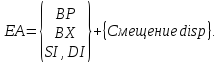

5. Регистровый относительный. Является обобщением методов адресации, обеспечивающих вычисление эффективного адреса (EA) операнда в памяти в виде суммы базового значения адреса и «смещения» disp, указываемого в команде (рис. 30) и (формула 5.1).

Рис. 30. Формирование эффективного адреса при

относительной адресации

(5.1)

(5.1)

Относительную адресацию широко применяют как для адресации памяти, представленной в виде блоков (например, сегментов), так и для адресации специальных структур данных: массивов, записей и др. В зависимости от способа использования адресуемого в команде регистра различают базовый и индексный режимы адресации.

5.1. Индексный. Применяется для обработки упорядоченных массивов данных; при этом каждый элемент массива определяется собственным номером. Тогда базовый адрес массива задаётся смещением disp, указываемым в команде, а значение индекса (номер элемента массива) определяется содержимым индексного регистра (формула 5.2).

(5.2)

(5.2)

Пример: d_s segment

mas db 3,5,1,8,9,’$’

d_s ends

c_s segment

assume ds:d_s, cs:c_s

begin:

…

mov si,0 ;в si-номер элемента массива

m1: mov ah, mas[si] ;mas- смещение

;в ah – значение элемента массива mas с

;номером в si

add si,1

jmp m1

…

c_s ends

end begin

Индексная адресация удобна, если необходимо записать или считать список данных из последовательных ячеек памяти не подряд, а с некоторым шагом, указанным в индексе.

5.2. Базовый. Применяется для доступа к структурам данных переменной длины. Тогда базовый адрес, определяющий начало набора элементов, хранится в базовом регистре, а смещение в команде определяет расстояние до определённого элемента (формула 5.3).

(5.3)

(5.3)

Этот режим адресации удобно использовать для записей – структур данных, содержащих поля различной длины и, возможно, различных типов.

Рассмотрим пример организации записи о сотрудниках некоторого отдела и доступа к ней и её полям. Условимся, что все поля символьные.

Пример:

worker struc ;информация о сотруднике

nam db 30 dup (' ') ;фамилия, имя, отчество

position db 30 dup (' ') ;должность

age db 2 dup(‘ ’) ;возраст

standing db 2 dup(‘ ’) ;стаж

salary db 5 dup(‘ ’) ;оклад в рублях

worker ends

d_s segment

;описание одного сотрудника

sotr1 worker <‘Иванов Пётр Сергеевич’,

‘программист’, ‘30’, ‘8’, ‘15000’>

d_s ends

c_s segment

assume ds:d_s, cs:c_s

begin:

…

;загружаем в bx адрес начала записи (базовый адрес)

lea bx, sotr1

;в ax – значение по адресу bx+смещение по полю age

;т.е., от начала записи находим ячейки,

;содержащие информацию о возрасте

mov ax, word ptr [bx].age

xchg ah, al

…

c_s ends

end begin

В записях с полями различной длины содержимое адресуемого регистра соответствует началу записи, а смещение в команде – расстоянию в записи.

6. Базово-индексный. Используется для доступа к элементам массива, адресуемого указателем. Базовый адрес массива задаётся указателем базы (базовым регистром), а номер элемента массива – содержимым индексного регистра (формула 5.4).

(5.4)

(5.4)

Пример: mov ax, bx[si]

Если в bx содержится 100, а в si находится 52, то по адресу (смещению) 152 в сегменте данных находится искомое данное.

Такой режим адресации удобно использовать при работе со сложными структурами данных, поскольку он позволяет изменять две адресные компоненты.

7. Относительный базовый индексный. Используется для адресации элементов в указываемом массиве записей. Базовый адрес массива задаётся указателем базы, номер записи (т.е., элемента массива) определяется содержимым индексного регистра, а смещение в команде указывает расстояние до записи (формула 5.5).

(5.5)

(5.5)

Пример:

…

d_s segment

;опишем массив из 5 сотрудников со значениями по

;умолчанию

mas_sotr worker 5 dup (<>)

d_s ends

c_s segment

assume ds:d_s, cs:c_s

begin:

…

;в bx – адрес начала массива сотрудников

lea bx, mas_sotr

;в si – смещение второй записи

mov si, (type worker)*2

; в ax – стаж второго сотрудника

mov ax,[bx][si].standing

…

c_s ends

end begin

Таким образом, чтобы получить доступ к конкретному полю массива записей, сначала необходимо определить начало массива, в нём найти нужную запись, а уже в ней – требуемое поле.

Выбор режима адресации определяется конкретной задачей и во многих случаях очевиден. Однако возникают ситуации, когда для обращения к одним и тем же элементам данных допускается использовать нескольких способов адресации. В конечном итоге, при написании программы сам пользователь осуществляет выбор конкретного режима адресации.