Шумахер У. Полупроводниковая электроника

.pdf

INFSEMI_2-Text.fm, стр. 242 из 589 (September 3, 2010, 17:05)

242 6. Память

Заметим, что попытка «отменить» муль- |

миться к тому, чтобы паузы в работе, свя- |

||||||||

типлексирование адреса (т.е. активизиро- |

занные с процессом обновления данных, |

||||||||

вать строку и столбец одновременно) нико- |

были минимальными. |

|

|

|

|||||

им образом не позволит ускорить работу |

Чтобы исключить возможность потери |

||||||||

DRAM. Принцип организации динамичес- |

данных в ячейках памяти, эти данные долж- |

||||||||

кой памяти предполагает наличие неболь- |

ны через определённые интервалы времени |

||||||||

шой, но обязательной временной задержки |

обновляться, т.е. считываться, усиливаться |

||||||||

с момента выбора (активации) строки до |

и записываться обратно в ячейки. Данный |

||||||||

того момента, когда данные станут доступ- |

процесс осуществляется каждый раз при |

||||||||

ны (считаны в буфер данных строки), и |

обращении к строке матрицы DRAM. Сиг- |

||||||||

можно будет активировать адрес столбца. |

нал выбора строки управляет открыванием |

||||||||

Обновление памяти |

коммутирующих |

транзисторов |

в ячейках |

||||||

памяти. Транзисторы, в свою очередь, под- |

|||||||||

|

|||||||||

Поскольку основой ячейки памяти |

ключают |

запоминающие |

конденсаторы к |

||||||

DRAM является конденсатор очень ма- |

входам усилителей считывания соответ- |

||||||||

ленькой ёмкости, с течением времени, |

ствующих столбцов. В процессе считыва- |

||||||||

вследствие различного рода утечек, неиз- |

ния данных, как указывалось выше, проис- |

||||||||

бежна потеря хранящегося в ней заряда. |

ходит утечка заряда из ячеек памяти. Поэ- |

||||||||

Одной из главных причин утечек является |

тому после завершения указанного процес- |

||||||||

повышение температуры, которое придает |

са усиленные напряжения, соответствую- |

||||||||

носителям заряда б=ольшую энергию и поз- |

щие |

исходным |

логическим |

уровням |

|||||

воляет им легче преодолевать изолирую- |

сигналов, поступают обратно на конденса- |

||||||||

щий барьер. Временной интервал с момен- |

торы ячеек памяти, восстанавливая их за- |

||||||||

та записи данных в ячейку до момента, ког- |

ряд. Как правило, для того чтобы ускорить |

||||||||

да данные из ячейки начинают считываться |

процесс обновления данных, используется |

||||||||

некорректно из-за потери части заряда на |

метод одновременной адресации несколь- |

||||||||

конденсаторе, называется временем обнов- |

ких строк. Так, например, у микросхем |

||||||||

ления, или временем хранения данных. |

SDRAM |

при |

выполнении |

команды |

|||||

Длительность этого интервала зависит от |

Auto Refresh |

происходит |

одновременное |

||||||

значения хранящегося в ячейке сигнала |

обращение к строкам длиной 8 Кбит в каж- |

||||||||

данных. Например, если в ячейке памяти |

дом из банков памяти, и данные из всех |

||||||||

хранится логический 0 и окружающая ячей- |

ячеек в этих строках считываются и запи- |

||||||||

ку подложка имеет нулевой потенциал, то |

сываются обратно. |

|

|

|

|||||

нет никакой причины для возникновения |

Для того чтобы все ячейки памяти вовре- |

||||||||

тока утечки, который мог бы изменить по- |

мя обновлялись, обращение к каждой стро- |

||||||||

тенциал ячейки (т.е. время обновления уве- |

ке должно производиться с заданным ин- |

||||||||

личивается). При более точной оценке вре- |

тервалом времени. Поскольку в процессе |

||||||||

мени обновления необходимо учитывать, |

обычной работы компьютера такая регу- |

||||||||

что вокруг данной ячейки располагаются |

лярная адресация никогда не происходит, |

||||||||

другие строки и столбцы ячеек памяти, в |

обновление памяти осуществляется с помо- |

||||||||

которых вполне могут содержаться логичес- |

щью специальной команды. Для асинхрон- |

||||||||

кие 1. Тем не менее, если ячейка была изго- |

ных DRAM |

это |

команда |

CAS before RAS |

|||||

товлена оптимальным образом и не имеет |

(CBR), |

а |

для SDRAM |

— Auto Refresh. |

|||||

случайных дефектов, предельное время об- |

В процессе выполнения этой команды ад- |

||||||||

новления данных является вполне адекват- |

реса строк не поступают извне, а генериру- |

||||||||

ной величиной. Производители микросхем |

ются встроенной логической схемой на ос- |

||||||||

DRAM обычно приводят этот параметр в |

нове счётчика. Имеется также команда |

||||||||

спецификации как собственное (внутрен- |

Self Refresh |

(иногда |

она |

называется |

|||||

нее) время обновления. |

Sleep Mode), |

вызов |

которой |

переводит |

|||||

При проектировании устройств DRAM |

DRAM в режим непрерывного, полностью |

||||||||

следует очень хорошо понимать, что при от- |

автономного обновления памяти. |

||||||||

сутствии обновления данных в течение не- |

Устройством, |

определяющим, когда и |

|||||||

которого времени, примерно через не- |

каким способом будет осуществляться об- |

||||||||

сколько миллисекунд после записи, данные |

новление DRAM, обычно является процес- |

||||||||

будут потеряны. Необходимо также стре- |

сор. Существует два стандартных подхода к |

||||||||

INFSEMI_2-Text.fm, стр. 244 из 589 (September 3, 2010, 17:05)

244 6. Память

до выхода из этого режима обновление па- |

Поэтому приходится применять тесты, |

|||||||||

мяти проводилось в последний раз. |

|

|

которые не моделируют поведение микро- |

|||||||

Характеристики внутреннего |

таймера, |

схемы во всех возможных условиях, а на- |

||||||||

управляющего процессом обновления дан- |

правлены на обнаружение физических де- |

|||||||||

ных, как и характеристики всех других эле- |

фектов ячеек памяти и соседствующих с |

|||||||||

ментов микросхемы DRAM, могут несколь- |

ними элементов. Всё это влечёт за собой не- |

|||||||||

ко изменяться вследствие технологических |

обходимость разработки специализирован- |

|||||||||

разбросов. Задать корректное значение ин- |

ного набора тестов для каждой архитектуры |

|||||||||

тервала обновления можно с помощью спе- |

микросхем памяти и для каждой из техно- |

|||||||||

циальной схемы коррекции; методика та- |

логий их производства. |

|

|

|||||||

кой коррекции аналогична |

используемой |

Если взять за основу подход, связанный |

||||||||

при подключении резервных ячеек памяти. |

с исследованием всех возможных механиз- |

|||||||||

Некоторые проблемы, связанные |

|

|

мов неисправностей, то процесс обнаруже- |

|||||||

|

|

ния дефектных ячеек и их исправления мо- |

||||||||

с процессом обновления данных в DRAM |

||||||||||

жет быть осуществлён за вполне приемле- |

||||||||||

|

|

|

|

|

|

|||||

Термин «обновление данных» относится |

мое время. Такой подход более предпочти- |

|||||||||

к процедуре и механизму обновления ин- |

телен, поскольку обеспечивает стабиль- |

|||||||||

формации, записанной в ячейках памяти. |

ность процента выхода годной продукции и |

|||||||||

Соответственно, время обновления — это |

позволяет избежать нареканий со стороны |

|||||||||

временной интервал между записью дан- |

потребителей. |

|

|

|||||||

ных в ячейку памяти и последующим их |

При оценке времени обновления памя- |

|||||||||

считыванием; в случае превышения указан- |

ти, его следует рассматривать с двух точек |

|||||||||

ного интервала возникают ошибки, связан- |

зрения. Во-первых, важную роль играет |

|||||||||

ные с потерей хранящейся в ячейке инфор- |

внутреннее время обновления. Для исправ- |

|||||||||

мации. Это время также называется време- |

ных ячеек памяти время хранения данных, |

|||||||||

нем хранения данных. |

|

|

|

|

лимитированное значением |

внутреннего |

||||

Поскольку главная задача микросхемы |

времени обновления, зависит только от фи- |

|||||||||

DRAM состоит именно в хранении данных, |

зических характеристик ячеек памяти и тех- |

|||||||||

значение такого её параметра, как время |

нологии их производства. Внутреннее вре- |

|||||||||

хранения данных, играет чрезвычайно важ- |

мя обновления в основном определяется |

|||||||||

ную роль. Оно зависит от разных факторов |

имеющим чётко выраженную температур- |

|||||||||

и может быть различным для различных |

ную зависимость процессом рекомбинации |

|||||||||

ячеек. Применительно к массиву ячеек па- |

зарядов в полупроводнике. |

|

|

|||||||

мяти это значение является великолепным |

Помимо |

использованной |

технологии, |

|||||||

«индикатором» качества технологического |

время хранения также зависит и от типа |

|||||||||

процесса. Действительно качественный |

и |

данных, хранящихся в ячейках памяти. Де- |

||||||||

отлаженный |

технологический |

процесс |

ло в том, что основные потери данных свя- |

|||||||

обеспечивает |

максимально |

высокое |

(и |

заны с утечками, которые происходят через |

||||||

практически одинаковое для всех ячеек па- |

ближайшее |

окружение ячейки |

памяти. |

|||||||

мяти) время хранения данных. |

|

|

Конденсатор ячейки, при условии, что его |

|||||||

Одна из основных проблем состоит в |

вторая обкладка имеет потенциал земли, |

|||||||||

том, что любая купленная потребителем |

может находиться в одном из двух состоя- |

|||||||||

микросхема, |

несмотря |

на |

существование |

ний: заряжен или не заряжен (что соответ- |

||||||

большого количества |

взаимонезависимых |

ствует логической 1 или логическому 0). Ес- |

||||||||

факторов, влияющих на ее функциониро- |

ли в одном из этих состояний разность по- |

|||||||||

вание, должна обеспечивать гарантирован- |

тенциалов с соседними ячейками равна ну- |

|||||||||

ное минимальное время хранения данных |

лю, то очевидно, что никакого «перетека- |

|||||||||

при любых условиях. Выполнение этого |

ния» заряда происходить не будет. Таким |

|||||||||

требования должно подтверждаться соот- |

образом, ячейки памяти, в которые записа- |

|||||||||

ветствующими тестами. Однако создавать |

ны логические данные (биты), соответству- |

|||||||||

тесты, имитирующие все возможные усло- |

ющие малому значению разности потенци- |

|||||||||

вия работы микросхемы, очень сложно. |

алов с соседними ячейками, будут характе- |

|||||||||

Кроме того, время тестирования не должно |

ризоваться |

б=ольшим временем |

хранения, |

|||||||

превышать разумные пределы. |

|

|

чем ячейки, заряд которых сильнее отлича- |

|||||||

|

|

|

|

|

|

ется от заряда соседних ячеек. |

|

|

||

INFSEMI_2-Text.fm, стр. 246 из 589 (September 3, 2010, 17:05)

246 6. Память

женные потенциально дефектные ячейки |

Чувствительность микросхем DRAM к |

|||||||

могут быть заменены на исправные. Хотя |

такого рода сбоям зависит, в основном, от |

|||||||

возможность такого ремонта ограничена, её |

топологии ячеек памяти и ёмкости конден- |

|||||||

следует использовать в полной мере. |

сатора ячейки. То есть, физическая форма |

|||||||

Частота случайных ошибок (сбоев) |

ячейки определяет б=ольшую или меньшую |

|||||||

вероятность утечки заряда при пролёте аль- |

||||||||

|

|

|

|

|||||

Данные, хранящиеся в ячейке памяти, |

фа-частицы. |

|

|

|||||

подвержены влиянию не только электри- |

Так или иначе, значение параметра SER |

|||||||

ческих и физических процессов, локализо- |

для каждой микросхемы должно быть изме- |

|||||||

ванных внутри самой микросхемы. Другим |

рено. Существуют два основных метода его |

|||||||

источником ошибок в работе ОЗУ являются |

определения. Более точный, но одновре- |

|||||||

случайные сбои (потери данных) в ячейках |

менно и более дорогой, — это метод поле- |

|||||||

памяти под воздействием альфа-частиц. |

вых испытаний. Он заключается в том, что |

|||||||

Альфа-частицы присутствуют в материале, |

тысячи микросхем работают одновременно |

|||||||

из которого изготовлен корпус микросхемы |

в течение многих часов, при этом фиксиру- |

|||||||

памяти, вследствие его неизбежного радио- |

ется реальное значение SER. Для того что- |

|||||||

активного загрязнения, например ураном |

бы получить как можно более точные дан- |

|||||||

238. Они проникают через поверхность по- |

ные, требуется большое количество микро- |

|||||||

лупроводникового кристалла и создают в |

схем и длительное время испытаний. |

|

||||||

нём более или менее длинный след из ио- |

Второй метод — метод ускоренных ис- |

|||||||

низированных молекул. Длина таких сле- |

пытаний с использованием радиоактивных |

|||||||

дов, как правило, не превышает нескольких |

материалов, или ASER (Accelerated Soft |

|||||||

микрон, но этого достаточно для создания |

Error Rate). При выполнении данного теста |

|||||||

или нейтрализации зарядов в ближайших |

непосредственно над массивом ячеек памя- |

|||||||

ячейках памяти, как и для того, чтобы иска- |

ти устанавливается радиоактивный |

зонд. |

||||||

зить значение напряжения на входе усили- |

Используя калиброванный уровень излуче- |

|||||||

теля считывания данных столбца. Эти |

ния радиоактивного пробника и соответ- |

|||||||

ошибки называются случайными сбоями, |

ствующую методику пересчёта, можно оце- |

|||||||

поскольку они генерируются |

случайным |

нить реальное значение SER. Однако такой |

||||||

образом и, как правило, не повторяются. |

пересчёт |

необходимо производить |

очень |

|||||

Сбои, вызываемые пролётом альфа-час- |

аккуратно. Существуют различные, |

часто |

||||||

тиц, не приводят к постоянным дефектам |

весьма сложные методики расчётов реаль- |

|||||||

ячеек памяти. В следующий раз, при записи |

ного значения SER. В любом случае, весьма |

|||||||

новых данных в эти же ячейки, они будут |

полезно после проведения подобной оцен- |

|||||||

работать совершенно |

корректно. Однако |

ки сравнить её результаты с реально изме- |

||||||

даже такие, возникающие время от времени |

ренным значением. |

|

|

|||||

ошибки могут в некоторых условиях вызы- |

Внешний интерфейс (входы и выходы) |

|||||||

вать существенную потерю данных в ком- |

||||||||

|

|

|

|

|||||

пьютерной системе. |

|

|

Параметры интерфейса для связи мик- |

|||||

Поскольку абсолютно чистых материа- |

росхем DRAM с внешними устройствами, |

|||||||

лов, пригодных для изготовления корпусов |

как правило, с максимальной степенью |

|||||||

микросхем, попросту не существует, всегда |

точности задаются в спецификациях ИС. |

|||||||

следует принимать в расчёт определённую |

Это делается не из абстрактной любви к на- |

|||||||

вероятность |

возникновения |

случайных |

учному прогрессу, а затем, чтобы обеспе- |

|||||

сбоев (Soft Error Rate — SER). Единицей из- |

чить как можно более высокий уровень |

|||||||

мерения частоты случайных сбоев является |

преемственности (различных |

поколений |

||||||

FIT (Failure In Time — количество ошибок в |

микросхем и модулей) и совместимости |

|||||||

единицу времени). Один FIT соответствует |

(изделий различных производителей). |

|

||||||

одной ошибке на 1 109 часов работы изде- |

Наличие «жёстких» технических стан- |

|||||||

лия. Пользователь вправе ожидать, что для |

дартов накладывает определённые ограни- |

|||||||

любой из купленных им микросхем частота |

чения на производителей микросхем, но да- |

|||||||

случайных сбоев не превысит максимально |

же если только один из конкурирующих |

|||||||

допустимое для микросхем DRAM значе- |

производителей способен выпускать про- |

|||||||

ние, которое, |

как |

правило, |

составляет |

дукцию, |

соответствующую |

требованиям |

||

500 FIT. |

|

|

|

этих стандартов, у остальных не остается |

||||

INFSEMI_2-Text.fm, стр. 248 из 589 (September 3, 2010, 17:05)

248 6. Память

широко распространенного аналогового си- |

внешним цепям, и т.д. Поскольку размеры |

|||||

мулятора SPICE. С помощью данной про- |

микросхем DRAM всегда крайне ограниче- |

|||||

граммы может быть точно промоделировано |

ны, использование любых дополнительных |

|||||

поведение схемы во времени. Предвари- |

транзисторов при их разработке должно |

|||||

тельным условием для этого является нали- |

быть сведено к минимуму (в этом состоит |

|||||

чие параметрических моделей |

элементов, |

одно из их отличий от схемотехники мик- |

||||

соответствующих используемой технологии. |

росхем предыдущих поколений, когда на- |

|||||

Если точность этих параметрических моде- |

личие одного-другого «лишнего» транзис- |

|||||

лей соответствует требованиям, то предпо- |

тора не составляло особой проблемы). |

|||||

лагаемое поведение схемы также может |

Так же как на основе принципиальной |

|||||

быть описано с достаточной точностью. Хо- |

схемы может быть сгенерирован список со- |

|||||

тя DRAM работает, в основном, в цифровом |

единений, так и на основе схемы разводки и |

|||||

режиме, использование аналогового моде- |

внутренних соединений генерируется спи- |

|||||

лирования неизбежно, поскольку обычные |

сок, |

предназначенный |

для последующего |

|||

логические симуляторы могут |

отображать |

анализа на соответствие технологическим |

||||

лишь статические изменения |

логического |

правилам. Оба этих списка сравниваются |

||||

состояния схемы, происходящие при изме- |

друг с другом; выявленные различия устра- |

|||||

нениях логических уровней сигналов. Ника- |

няются, чтобы разводка соединений в крис- |

|||||

кие динамические параметры |

(например, |

талле |

соответствовала |

принципиальной |

||

сколько времени требуется для изменения |

схеме, задуманной разработчиком. |

|||||

уровня сигнала из 1 в 0, которое не равно |

Помимо этой проверки, схема разводки |

|||||

нулю вследствие того, что коммутирующий |

соединений должна быть протестирована на |

|||||

транзистор тем или иным образом взаимо- |

соответствие |

технологическим правилам. |

||||

действует с коммутируемой им нагрузкой) |

Например, необходимо определить мини- |

|||||

логический симулятор не определяет. Меж- |

мальное расстояние до металлических про- |

|||||

ду тем, без точной оценки аналоговых ха- |

водников, а также размеры контактных от- |

|||||

рактеристик переключения используемых в |

верстий или размеры диффузионных зон у |

|||||

DRAM коммутирующих транзисторов нель- |

транзисторов. Существует немало правил, |

|||||

зя добиться максимальной, насколько это |

которым должна соответствовать разводка |

|||||

возможно с точки зрения электроники, ско- |

кристалла, поскольку |

используемый при |

||||

рости работы микросхемы и при этом сде- |

производстве |

микросхем технологический |

||||

лать размеры транзисторов как можно мень- |

процесс всегда рассчитан на изготовление |

|||||

ше, чтобы сократить пространство, занима- |

полупроводниковых структур не произволь- |

|||||

емое ими на кристалле. Кроме того, анало- |

ного, а строго определённого вида. |

|||||

говое моделирование — это единственный |

Технологический процесс |

|||||

путь к получению корректной информации |

||||||

|

|

|

|

|||

о влиянии внешних факторов, например из- |

Технологический процесс представляет |

|||||

менения температуры, на характеристики |

собой конкретную последовательность дейс- |

|||||

разрабатываемой схемы. |

|

твий при производстве кристалла микросхе- |

||||

Размещение/разводка соединений/верификация |

мы. При его реализации заготовка — пласти- |

|||||

на из чистого кремния — проходя через мно- |

||||||

|

|

|||||

Полученная в результате CAD-проекти- |

жество технологических этапов, таких как |

|||||

рования электрическая схема, все компо- |

экспозиция, травление, шлифовка, нанесе- |

|||||

ненты которой представлены в символичес- |

ние покрытия, ионная имплантация, окис- |

|||||

ком виде, должна быть преобразована к ви- |

ление и т.д., превращается в готовый чип. |

|||||

ду, соответствующему реальным физичес- |

Сборка |

|

|

|||

ким характеристикам используемых компо- |

|

|

||||

|

|

|

|

|||

нентов. Первый шаг на пути к этому — |

После того как кремниевая заготовка ус- |

|||||

создание для каждого отдельного компо- |

пешно прошла все стадии технологического |

|||||

нента его графического изображения (при- |

процесса, и на ней были отобраны чипы, |

|||||

митива) в соответствии с определёнными |

квалифицированные как годные, заготовка |

|||||

правилами. Так, транзистор рисуется в точ- |

распиливается |

при помощи специальной |

||||

ности со всеми его элементами: диффузи- |

пилы с алмазным напылением. Если пред- |

|||||

онными зонами, областью затвора, элект- |

полагается использовать наиболее распро- |

|||||

родами, служащими для подключения к

INFSEMI_2-Text.fm, стр. 250 из 589 (September 3, 2010, 17:05)

250 6. Память

Программа такого тестирования может |

ются, вместе составляют измерительную |

||||||

меняться с появлением каждого нового по- |

станцию. С помощью микроскопа зонд та- |

||||||

коления микросхем DRAM, чтобы соот- |

кой измерительной станции можно под- |

||||||

ветствовать новым рабочим характеристи- |

ключить к любой точке кристалла, что даёт |

||||||

кам (и/или рабочим режимам). Результаты |

возможность измерять временные характе- |

||||||

анализа схемных решений и контроля ка- |

ристики внутренних сигналов. Кроме того, |

||||||

чества также могут дать повод для измене- |

с помощью такой установки можно опреде- |

||||||

ния программы испытаний. Каждое схем- |

лить пределы, в которых микросхема сохра- |

||||||

ное решение или технология создания по- |

няет работоспособность, и, в том случае, |

||||||

лупроводниковых |

элементов |

имеют свои |

когда обнаруживается сбой, выяснить, в ка- |

||||

слабые места, которые должны быть обна- |

ком именно месте сигнал обрабатывается |

||||||

ружены, изучены и устранены. В результа- |

некорректно. |

|

|||||

те, несмотря на то, что различные поколе- |

Для того чтобы использовать микрозон- |

||||||

ния DRAM имеют близкие характеристики, |

ды для измерений внутри кристалла, следу- |

||||||

программа испытаний для каждого из них |

ет обеспечить возможность подключения к |

||||||

достаточно индивидуальна. |

|

требуемой |

дорожке. Обычно внутренняя |

||||

Схемные решения и анализ |

|

схема кристалла защищена слоями поли- |

|||||

|

амида, оксида и нитрида кремния, поэтому |

||||||

неисправностей |

|

|

|||||

|

|

необходимо либо не создавать эти слои в |

|||||

|

|

|

|

||||

В отличие от технологии испытаний се- |

процессе изготовления микросхемы, либо |

||||||

рийной продукции, при которых тестирую- |

удалить их впоследствии химическим мето- |

||||||

щие автоматы измеряют параметры тысяч |

дом. |

|

|

||||

микросхем, при анализе схемных ошибок |

Процесс поиска и анализа неисправнос- |

||||||

или неисправностей каждая |

микросхема |

тей, как правило, начинается с тестирова- |

|||||

рассматривается как нечто индивидуаль- |

ния серийной продукции на отказ и с попы- |

||||||

ное. Анализ схемных решений подразуме- |

ток найти причины обнаруженных отказов. |

||||||

вает как исследование работы микросхемы |

На этом этапе анализ неисправностей и |

||||||

в целом, так и изучение работы её состав- |

анализ схемотехнических решений произ- |

||||||

ных частей. Такое исследование возможно |

водятся одновременно, потому что одной |

||||||

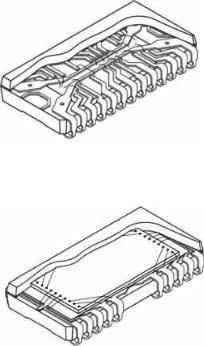

благодаря |

использованию |

микрозондов |

из причин возникновения того или иного |

||||

(подобный зонд представляет собой очень |

дефекта |

может |

быть схемотехническая |

||||

острую иглу), с помощью которых сигналы |

ошибка. Во всех остальных случаях основ- |

||||||

могут быть измерены прямо на алюминие- |

ное внимание при анализе неисправностей |

||||||

вых проводящих дорожках субмикронной |

обращается на возможные погрешности в |

||||||

ширины |

внутри |

кристалла |

микросхемы |

технологии производства. |

|||

(Рис. 6.13). Микрозонды и микроманипу- |

Анализ схемотехнических решений про- |

||||||

ляторы, с помощью которых они управля- |

изводится довольно просто. Искусственно |

||||||

|

|

|

|

создаются условия для возникновения оши- |

|||

|

|

|

|

бок, и исследуется прохождение сигналов |

|||

|

|

|

|

внутри микросхемы в данных условиях. При |

|||

|

|

|

|

этом, по большому счёту, неважно, работо- |

|||

|

|

|

|

способна ли микросхема в целом или нет. |

|||

|

|

|

|

Вполне достаточно функционирования от- |

|||

|

|

|

|

дельных её блоков. Если же речь идёт об |

|||

|

|

|

|

анализе неисправностей микросхемы в це- |

|||

|

|

|

|

лом, обычно нет возможности проконтро- |

|||

|

|

|

|

лировать качество её внутренних сигналов. |

|||

|

|

|

|

В этом случае необходимо поместить мик- |

|||

|

|

|

|

росхему в такие условия, когда её внутрен- |

|||

|

|

|

|

ние неисправности проявятся в виде оши- |

|||

|

|

|

|

бочных данных на её выходах. Если микро- |

|||

|

|

|

|

схема уже смонтирована в корпусе, един- |

|||

Рис. 6.13. Измерительная станция с микро- |

ственное, что можно сделать для обнаруже- |

||||||

ния внутренних |

неисправностей, — это |

||||||

зондами и микроманипуляторами. |

|||||||

проконтролировать соответствие информа- |

|||||||

|

|

|

|

||||