- •Вопросы

- •Виды параллельной обработки данных на эвм

- •Параллелизм на уровне машинных команд.

- •Структура оперативной памяти.

- •Секция ввода/вывода

- •Секция межпроцессорного взаимодействия

- •Регистровая структура Cray c90

- •Понятие векторн обр-ки, зацепл фу(Cray c90) Векторная обработка

- •Функциональные устройства

- •Независимость функциональных устройств

- •Зацепление функциональных устройств

- •Закон Амдала .Время разгона конвейера Закон Амдала и его следствия

- •Причины уменьшения производительности Cray c90

- •Суммарное влияние отрицательных факторов на производительность компьютера

- •Архитектура компьютера EarthSimulator.

- •Массивно-параллельные компьютеры, общие черты

- •Общая структура компьютера cray t3d

- •Вычислительные узлы и процессорные элементы

- •Коммуникационная сеть

- •Топология сети, чередование вычислительных узлов

- •Маршрутизация в сети и сетевые маршрутизаторы.

- •Нумерация вычислительных узлов.

- •Особенности синхронизации процессорных элементов

- •Причины уменьшения производительности компьютера Cray t3e/d.

- •Вычислительные кластеры:узлы,коммуникационная сеть (латентность, пропускная способность).

- •История проекта Beowulf

- •Общая характеристика Hewlett-PackardSuperdome.

- •Предсказание ветвлений

- •Причины уменьшения производительности

- •Графовые модели программ, их взаимосвязь.

- •Mpi. Терминология и обозначения

- •Общие процедуры mpi

- •Mpi: синхронное и асинхронное взаимодействие процессов. Прием/передача сообщений между отдельными процессами

- •Прием/передача сообщений с блокировкой

- •Совмещенные прием/передача сообщений

- •Mpi: коммуникаторы

- •Коллективные взаимодействия процессов

- •Mpi: глобальные операции, барьеры Синхронизация процессов в mpi происходит посредством единственной функции

- •Транспьютер: основы архитектуры и его характеристика.

- •Оценки быстродействия вычислительных систем. Тесты производительности сети. Тесты производительности файловой системы. Тесты производительности процессора. Комбинированные тесты

- •Тесты производительности сети

- •Тесты производительности файловой системы

- •Тесты производительности процессора

- •Комбинированные тесты

- •Терминология

- •Классификация Флинна

- •Дополнения Ванга и Бриггса к классификации Флинна

- •Классификация Фенга

- •Классификация Шора

- •Классификация Хендлера

- •Классификация Хокни

- •Классификация Шнайдера

- •Классификация Джонсона

- •Классификация Базу

- •Классификация Кришнамарфи

- •Классификация Скилликорна

- •Классификация Дазгупты

- •Классификация Дункана

- •Принципы разработки современных парраллельных компьютеров.

- •Конвейерная организация Простейшая организация конвейера и оценка его производительности

- •Структурные конфликты и способы их минимизации

- •Конфликты по данным, остановы конвейера и реализация механизма обходов

- •Сокращение потерь на выполнение команд перехода и минимизация конфликтов по управлению

- •Ожидающие функции

- •Виды функций активации

- •Алгоритм решения задач с помощью мсп

- •Формализация задачи

- •Методы обучения

- •Сеть с линейным поощрением

- •Место нейронных сетей среди других методов решения задач

Общая характеристика Hewlett-PackardSuperdome.

Как известно класс параллельных компьют с общ памятью облад след особ - (+) этого класса – простота программирования, (-)-малое число процессоров. Один из способов разрешения проблемы – исп компьют с распр памятью, у кот память на уровне программиста (логически) в той или иной степени однородна (смотри ccNUMA,NUMA).

Проведем исследование архитектуры данного класса на примере НР Superdome.

Число проц 2-64, возможно расширение. Все проц имеют доступ к памяти(до 256 Гбайт в будущем 1Тбайт) организ в соотв с концепц ccNUMA. Следоват

-проц работают в един адр простр-ве

-доступ к лок памяти быстрее

-необходимо вести согласование КЭШ-ей с памятью(решено на ур-не аппар-ры)

В комп-ре одновр могут быть использ процессоры из семейств

-РА-8600(HP)

-РА-8700(HP)

-В будущем IA-64 (HP&Intel)

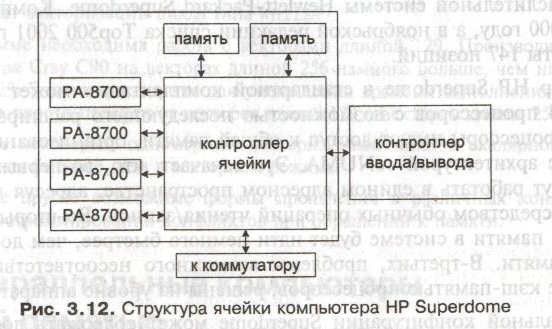

Основа арх-ры –вычислит ячейки (cells), связанные иерархич системой переключателей. Каждая ячейка – симметричный мультипроцессор, реализ на одной плате, в кот присутствует

-проц-ры(до 4шт)

-опер пам-ть(до 16 Гбайт)

-контроллер ячейки

-преобраз-ли питания

-связь с подсистемой вв/выв

Центр место в арх-ре заним контроллер ячейки(24 млн транзист). Для каждого процессора ячейки есть собств порт в контроллере. Обмен данными межд проц и контр-ом происходит со скор-тью 2 Гбайт/сек.

Память ячейки-2-16Гбайт. Разделена на 2 банка, кажд из кот имеет свой порт в контроллере ячейки. Ск-ть обмена данными межд конт-ом и кажд банком составляет 2 Гбайт/сек, что дает макс проп сп-ть тракта “контроллер-память” 4 Гбайт/сек.

Соединение контр-ра ячейки с контр-ом УВВ (12 слотов PCI) уста-ся опционно. Один порт контр-ра ячейки всегда связан с внешн коммут-ом. Он предназн для обмена проц-ов ячейки с друг проц-ами системы. Ск-ть работы порта равна 8 Гбайт/сек. Контр-р ячейки отвечает и за коггерентность КЭШ-ей.

В 64 процессорн конфигурации Superdome состоит из 2 стоек, в кажд из кот по 32 проц-ра.

Кажд стойка содерж по 2 8-портовых неблокирующих коммутатора. Все порты работают со ск-тью 8 Гбайт/сек. К кажд ком-ру подкл 4 ячейки. 3 порта задейств для взаимод с друг коммутатор системы(один в той же стойке, два других-в другой). Оставш порт предназн для связи с друг системами HPSupperdom.

Программно-аппар часть компьютера позволяет настроить HPSd как единый компьютер с общей памятью, так и совокупность независимых разделов, работающих под различными ОС.

Характеристика PA-8200(сходное семейство)

PA-8200 представляет собой суперскалярный 64-битный RISC-процессор и реализует архитектуру PA-RISC 2.0. В настоящее время существуют две версии этого процессора, работающие на частотах 200 и 240 MHz. При тактовой частоте в 240MHz процессор обеспечивает пиковую производительность в 960 MFLOPS, за счет одновременного исполнения 4 инструкций с плавающей точкой.

Процессор PA-8200 включает следующие архитектурные особенности

Раздельные первичные кэши кода и данных, каждый по 2MB. Особенностью архитектуры PA-RISC является внекристальная реализация кэша, что позволяет увеличивать его объем при необходимости. Кэш-память второго уровня не используется.

10 независимых функциональных устройств:

Два 64-разрядных целочисленных АЛУ

Два целочисленных устройства сдвига

Два устройства умножения и сложения для чисел с плавающей точкой

Два устройства деления и извлечения корня для чисел с плавающей точкой

Два устройства чтения/записи данных

Буфер переупорядочения инструкций на 56 позиций; переупорядоченное выполнение инструкций позволяет постоянно поддерживать суперскалярный режим работы процессора. Устройство считывания инструкций доставляет в буфер 4 инструкции за такт.

Управляемая предвыборка данных из основной памяти в кэш

Статическое и динамическое предсказание ветвлений

64-битная адресация памяти

Встроенная программируемая аппаратура мониторинга производительности; позволяет отслеживать такие события как кэш-попадания (промахи), ошибки в предсказании ветвлений, и т.д.

На следующем рисунке представлена блок-схема процессора PA-8200:

Процессор PA-8200 - это вторая после PA-8000 реализация архитектуры PA-RISC 2.0. Главное нововедение в PA-RISC версии 2.0 - 64-битная целочисленная арифметика и 64-битная адресация. Версия 2.0 также добавила страницы переменного размера, несколько новых операций с плавающей точкой и ряд других преимуществ по сравнению с PA-RISC 1.1. При этом процессоры PA-8000/8200 сохраняют полную двоичную совместимость с процессорами PA-7100/7200.

Как было уже отмечено, PA-8200 поддерживает плоское 64-битное адресное пространство; хотя чип экспортирует 40-битные физические адреса (т.е. такие адреса используются для общения с физической памятью). Это соответствует 1 терабайту непосредственно адресуемой памяти.