Цифровые компараторы (устройства сравнения)

Цифровые компараторы (compare – сравнивать) выполняют сравнение двух чисел, заданных двоичным (двоично - десятичным) коде.

В зависимости от схемного выполнения компараторы могут определять равенства либо вид неравенства: A = B, A > B или A > B, где A и B – независимые числа с равным количеством разрядов. Результат сравнения отображается соответствующим логическим уровням на выходе.

Как правило, микросхемы цифровых компараторов выполняют все эти операции и имеют три выхода.

Применение:

-

Для выявления нужного числа (слова) в потоке цифровой информации.

-

Для отметки времени в часовых приборах.

-

Для выполнения условных переходов в вычислительных устройствах.

Как одноразрядный компаратор может

быть использована логическая схема,

выполняющая операцию эквивалентность

![]() (исключающие ИЛИ - НЕ). Чаще всего строится

на базе “исключающее - ИЛИ”.

(исключающие ИЛИ - НЕ). Чаще всего строится

на базе “исключающее - ИЛИ”.

Развернутая логическая структура одноразрядного компаратора имеет вид:

![]()

при А>В (т.е А=1, В=0)

![]()

при А<В (т.е А=0, В=1)

![]()

Два n – разрядных двоичных числа равны, когда попарно равны между собой все разряды этих чисел. Если числа A и B – четырехразрядные, то признаком равности будет:A3=B3; A2=B2; A1'=B1; A0=B0 ,или A = B при F=F3 F2 F1 F0=1, если F = 0, то A≠B.

Неравенство A > B обеспечивается в одном из четырех случаях:

-

A3>B3

-

A3=B3; A2>B2;

-

A3=B3; A2=B2; A1>B1;

-

A3=B3; A2=B2; A1=B1; A0>B0.

Примером цифрового компаратора может служить ИС К561ИП2.

Микросхема имеет расширяющие входы, которые позволяют наращивать разрядность обоих чисел без дополнительных логических элементов. (A = B, A > B, A > B)

Компараторы можно соединять каскадно и параллельно.

При параллельном (пирамидальном) соединении время задержки меньше (т. е. быстродействие компараторов выше.)

Каскадное включение цифровых компараторов:

Выходы A = B и A < B предыдущей ИС (младшие разряды) подключают к соответствующим входам последующий. На выходы A = B, A > B,A > B подают потенциалы “0”, “1”, “1”. В последующих ИС на входе A > B поддерживает уровень “1”.

Контроль четности.

Эта операция позволяет повысить надежность передачи двоичной информации.

Простой и эффективный способ обнаружения ошибок основан на допущении, что в каждый момент времени ошибка может возникнуть только в одном разряде, и проявляется она в лишней единице или в потере единицы.

Т. о., если передаваемое слово содержит четное число единиц по всем разрядам, а на конце линии передачи это число окажется нечетным, значит, появилась ошибка.

Реализация этого метода осуществляется с помощью специальных схем контроля четности.

На основе информации на выходе предыдущего элемента схема формирует дополнительный бит (паритетный или контрольный бит), т. е. “1” или “0” который добавляется к выходной информации.

Назначение паритетного бита – доводить число единиц в каждом передаваемом слове до четного или нечетного в зависимости от принятой системы кодирования.

На приемном конце линии происходит проверка паритета (parity - соответствие). Если он правилен разрешается прием, если нет – происходит включение сигнализатора ошибок.

Паритет может быть четным и нечетным.

В случае нечетного паритета - сумма единиц вместе с контрольным битом – должна быть нечетной, а для четного – наоборот. На практике нечетный паритет используется чаще, так как контроль нечетности позволяет фиксировать полное пропадание информации.

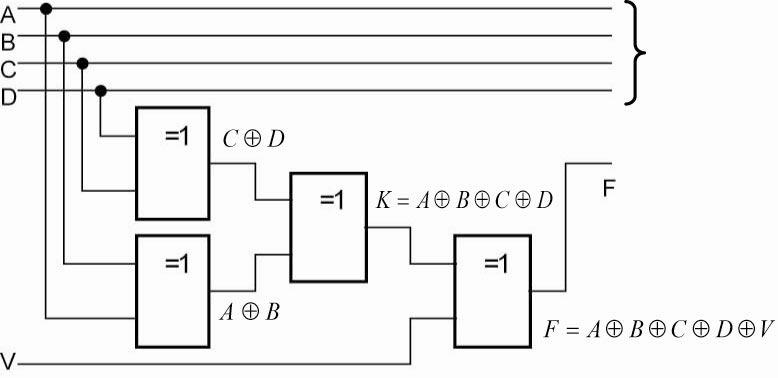

Структура схема проверки четности – многоступенчатая. В первой ступени (ярусе) попарно суммируются все биты слова. Выходные сигналы первого яруса являются входными для второго и так далее последовательно до окончания определения четности или нечетности всего слова.

Полученный результат на последнем этапе сравнивается с контрольным сигналом, задающим вид используемого паритета.

Если паритет четный, т. е. число единиц в слове, включая паритетный бит, должно быть четным, то контрольный сигнал должен быть равен сумме по модулю 2 всех информационных разрядов слова. Для нечетного паритета контрольный сигнал является инверсией указанной суммы.

Т. е. независимо от паритета четырех разрядного слова ABCD паритет пятиразрядного кода ABCDF будет всегда одинаков.

Потенциал на входе V определяет вид используемого паритета.

Примером самостоятельных изделий могут служить КМОП ИС К561СА1 и ТТЛ К155ИП2.

|

Входы |

Выход F |

||||

|

A |

B |

C |

D |

V=0 |

V=1 |

|

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

0 |

0 |

1 |

1 |

0 |

|

0 |

0 |

1 |

0 |

1 |

0 |

|

0 |

0 |

1 |

1 |

0 |

1 |

|

0 |

1 |

0 |

0 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

1 |

|

0 |

1 |

1 |

0 |

0 |

1 |

|

0 |

1 |

1 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

1 |

|

1 |

0 |

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

1 |

0 |

|

1 |

1 |

0 |

0 |

0 |

1 |

|

1 |

1 |

0 |

1 |

1 |

0 |

|

1 |

1 |

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

1 |

0 |

1 |