Схемотехника / Дешифраторы

.docДешифраторы

Дешифратор – комбинационная логическая схема, у которой каждой комбинации ее входных сигналов соответствует только один избранный выход системы.

Иногда называют декодерами – т. е. устройствами, распознающими (декодирующими) входные кодовые комбинации.

Избранным считают тот выход дешифратора, на котором при данной комбинации входных сигналов формируется активный уровень выходного сигнала. Выходы дешифратора могут быть прямые либо инверсные.

Число входов дешифратора равно числу двоичных разрядов во входных кодовых комбинациях.

Число выходов равно числу возможных входных кодовых комбинаций сигналов.

Дешифратор, который имеет

![]() -

входов и

-

входов и

![]() -

выходов, называют полным.

-

выходов, называют полным.

Функционирование полного дешифратора

описывается системой, состоящей из

![]() двоичных логических функций:

двоичных логических функций:

![]()

![]()

. . . . . . . . . . . . . . . .

![]()

![]()

![]() – функции, реализуемые на соответствующих

выходах дешифратора

– функции, реализуемые на соответствующих

выходах дешифратора

![]()

![]() – двоичные логические переменные,

поступающие на входы дешифратора

– двоичные логические переменные,

поступающие на входы дешифратора

![]()

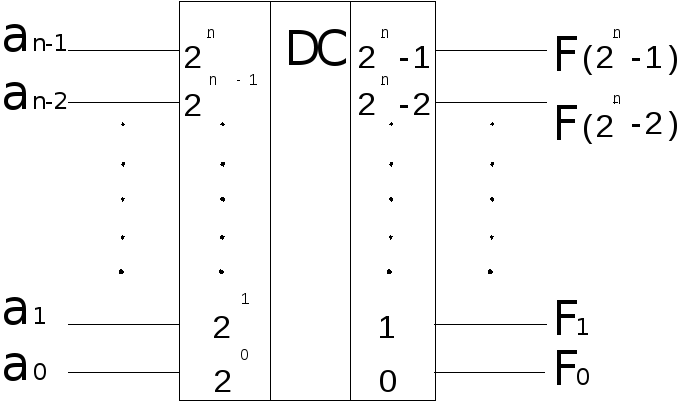

Условное графическое изображение дешифратора:

В левом поле даны двоичные веса

входных сигналов

![]() ,

комбинации которых образуют двоичные

коды (числа).

,

комбинации которых образуют двоичные

коды (числа).

В центральном поле

![]() – (decoder).

– (decoder).

В правом поле – порядковые номера выходов дешифратора.

Дешифратор, имеющий

![]() -

входов и

-

входов и

![]() -

выходов называется полным, если же у

дешифратора

-

выходов называется полным, если же у

дешифратора

![]() -

входов, а выходов меньше, чем

-

входов, а выходов меньше, чем

![]() ,

то такой дешифратор называется неполным.

,

то такой дешифратор называется неполным.

Пример неполного дешифратора – преобразователь двоичного кода в код управления десятичным индикатором (дешифраторы 4*10).

Дешифратор может быть синхронным и асинхронным.

Синхронный (тактируемый) выполняет свои функции только при наличии активного уровня сигнала на синхровыходе.

Кроме того,

![]() может иметь еще и вход разрешения

может иметь еще и вход разрешения

![]() ,

активный уровень сигнала на котором

разрешает работу дешифратора (этот вход

позволяет работать в режиме демультиплексра

– вход разрешения

,

активный уровень сигнала на котором

разрешает работу дешифратора (этот вход

позволяет работать в режиме демультиплексра

– вход разрешения

![]() при этом используют для приема данных).

при этом используют для приема данных).

![]()

![]()

![]()

![]()

. . . . . . . . . . . . . . . .

![]()

![]()

![]()

![]()

![]() с входом синхронизации

с входом синхронизации![]()

![]() с входом разрешения

с входом разрешения![]()

и входом синхронизации

![]()

Логическая структура дешифратора

Пример синхронного дешифратора 2*4 на

элементах

![]() .

.

Функционирование описывается следующей системой логических функций:

![]()

![]()

![]()

![]()

Дешифратор-демультиплексор

Это дешифратор, который наряду с его обычными входами и выходами имеет входы демультиплексирования, предназначенные для приема данных, либо для разрешения выполнения операции дешифрования.

![]()

![]()

![]()

![]()

![]() – входы демультиплексирования,

объединенные функцией логического

умножения.

– входы демультиплексирования,

объединенные функцией логического

умножения.

Таблица истинности

|

Входные сигналы |

Выходные сигналы |

|||||

|

|

|

|

|

|

|

|

|

0 0 1 1

|

0 1 0 1

|

1 1 1 1 0

|

1 0 0 0 0 |

0 1 0 0 0

|

0 0 1 0 0

|

0 0 0 1 0

|

Сдвоенные дешифратры-демультиплексоры

В таких

![]() имеется две группы выходов: группа

имеется две группы выходов: группа

![]() и группа выходов

и группа выходов

![]() .

.

Для каждой группы указанных выходов

разрешение на избрание одного из выходов

группы

![]() получают

получают

![]() дополнительных

входов демультиплексирования:

дополнительных

входов демультиплексирования:

-

Для группы

-выходов от входов

-выходов от входов

-

Для группы

-выходов

от входов

-выходов

от входов

При этом выходы выбора

![]() и

и

![]() являются общими для

являются общими для

![]() и

и

![]() -

группы выходов дешифратора.

-

группы выходов дешифратора.

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

Методы построения многоканальных дешифраторов

Наиболее распространенными являются следующие методы наращивания числа каналов дешифраторных схем:

-

каскадное соединение дешифраторов.

-

применение дополнительной входной лычки, объединяющей несколько ИМС дешифраторов в однокаскадную многоканальную дешифраторную схему.

-

матричное построение дешифраторной схемы.

Каскадное соединение дешифраторов

В первом каскаде работает

![]()

![]() ,

на входы которого подаются старшие

разряды

,

на входы которого подаются старшие

разряды

![]() .

Второй каскад включает

.

Второй каскад включает

![]()

![]() .

На входы каждого из

.

На входы каждого из

![]() второго каскада поданы младшие разряды

второго каскада поданы младшие разряды

![]() .

Выходы

.

Выходы

![]() соединены с синхровходами

соединены с синхровходами

![]() ,

т. е.

,

т. е.

![]() управляет

их работой.

управляет

их работой.

Число каскадов дешифраторной схемы:

![]()

Где

![]() – число выходных линий.

– число выходных линий.

![]() – число выходов ИМС.

– число выходов ИМС.

Количество ИМС в выходном каскаде:

![]()

Количество ИМС в каждом из предыдущих каскадов соответственно равно:

![]()

Где

![]() – число

– число

![]() в

последующем каскаде.

в

последующем каскаде.

Оценка быстродействия определяется по

времени задержки распространения

![]() по самому длинному пути.

по самому длинному пути.

![]() – для идентичных

– для идентичных

![]() ,

где

,

где

![]() – среднее время задержки распространения

сигнала в ИМС

– среднее время задержки распространения

сигнала в ИМС

![]() .

.

Применение дополнительной входной логики

Дополнительный метод обеспечивает построение многоканальной линейной (однокаскадной) дешифраторной схемы.

Для этого дополнительно используют 4

инвертора, образующие дополнительную.

Входную логику и сдвоенные

дешифраторы-демультиплексоры

![]() .

.

На входы схемы поступает четырех

разрядный двоичный код

![]() ,

подлежащий декодированию.

,

подлежащий декодированию.

В качестве дополнительных входов выбора

используют входы демультиплексирования

![]() и

и

![]() ,

на которые подаю старшие разряды

,

на которые подаю старшие разряды

![]() декодируемого числа с использованием

дополнительной входной логики.

декодируемого числа с использованием

дополнительной входной логики.

Для

![]() :

:

![]() для

для

![]()

![]()

![]()

![]()

Окончательное избрание выхода в группе осуществляется кодом младших разрядов числа

![]()

Максимальное число входных линий:

![]()

Где

![]() – для сдвоенных

– для сдвоенных

![]() .

.

![]() – для несдвоенных

– для несдвоенных

![]() .

.

![]() – количество входов выбора

– количество входов выбора

![]() – число входов демультиплексирования

– число входов демультиплексирования

Матричное построение дешифраторных схем

Особенностью построения матричных схем является то, что выходная ступень образована двухвходовыми логическими элементами И.

Входной четырехразрядный двоичный код

поступает на входы дешифраторов

![]() и

и

![]() ,

образующих первую ступень дешифратора.

Старшие разряды

,

образующих первую ступень дешифратора.

Старшие разряды

![]() – дешифруются

– дешифруются

![]() ,

а код младших разрядов

,

а код младших разрядов

![]() –

–

![]() независимо друг от друга.

независимо друг от друга.

Входы логических элементов И подключают

к выходным линиям дешифраторов

![]() и

и

![]() .

.

Число выходных каналов дешифраторной

схемы

![]() :

:

![]()

Здесь

![]() и

и

![]() – число выходов дешифраторов

– число выходов дешифраторов

![]() и

и

![]() соответственно.

соответственно.

![]() ;

;

![]()

Где

![]() и

и

![]() – число двоичных разрядов, поданных на

входы дешифраторов

– число двоичных разрядов, поданных на

входы дешифраторов

![]() и

и

![]() соответственно (

соответственно (![]() ).

).