- •Логические элементы ттл.

- •Основные электрические параметры

- •Основные характеристики серии ис ттл

- •Логические элементы ттлш

- •Логические элементы с тремя выходными состояниями.

- •Практические рекомендации:

- •Логические элементы кмоп

- •Основные характеристики серии кмоп

- •Базовые элементы кмоп

- •Инверторы кмоп с тремя выходными состояниями

- •Двунаправленный ключ.

- •Логические элементы кмоп.

- •Практические рекомендации.

Инверторы кмоп с тремя выходными состояниями

Такие инверторы имеют дополнительные ключевые транзисторы, управление которыми осуществляется по независимой цепи ЕО. Если оба этих ключа открыты, инвертор

|

а |

ЕО |

F |

|

0 1 0 1 |

0 0 1 1 |

Z Z 1 0 |

Двунаправленный ключ.

Эта специфический узел, состоящий из КМОП – транзисторов и не имеет функциональных аналогов среди микросхем других видов логики.

Ключ состоит из двух МОП транзисторов

с каналами разных типов проводимости.

Истоки и стоки обоих приборов соединены

между собой и выведены наружу. Управление

осуществляется двумя взаимоинверсными

сигналами Vи![]() ,

которые поступают на затворы транзисторов

от управляющего инвертора.

,

которые поступают на затворы транзисторов

от управляющего инвертора.

При V=![]() транзисторы

транзисторы![]() и

и![]() ключе открыты.

ключе открыты.

При V=![]() -

-![]() ,

,![]() - заперты.

- заперты.

условное изображение

Проводящие каналы обоих транзисторов

имеют сопротивление 20 – 500 Ом, носит

активный характер, а линейно в рабочем

диапазоне входных напряжений, и обладают

двуобгонной проводимостью. По этим

причинам двунаправленные ключи используют

для коммутации как дискретных так и

аналоговых сигналов. В закрытом состоянии

сопротивление между выводами xиyсоставляет![]() Ом.

Ом.

Логические элементы кмоп.

На основе инверторов КМОП реализуются многие функциональные логические схемы. Для реализации логических элементов И – НЕ в положительной логике транзисторы с n- каналом включаются последовательно друг с другом, с р- каналом параллельно, а для операции ИЛИ – НЕ наоборот.

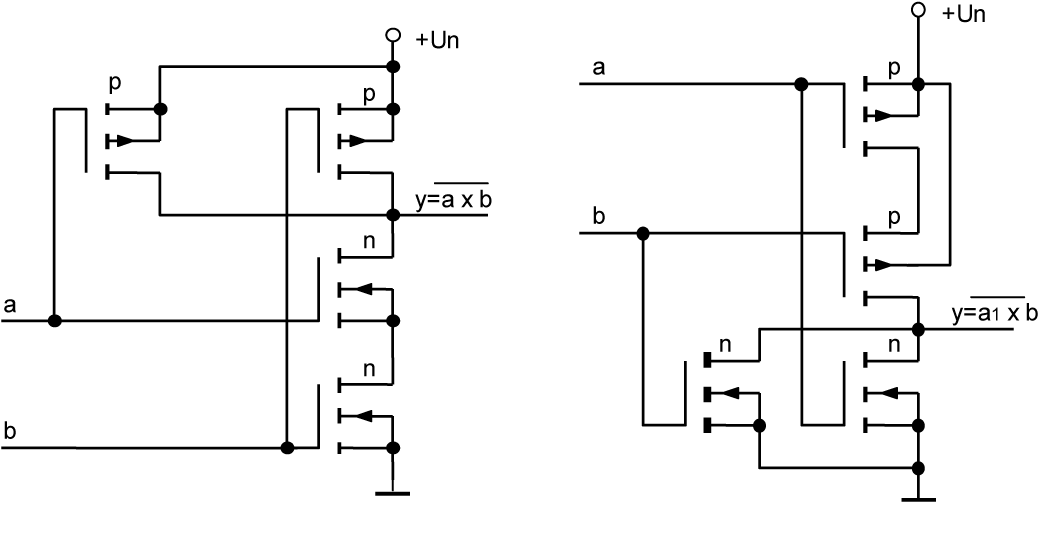

Принципиальная схема логического Принципиальная схема логического

элемента 2И - НЕ элемента 2ИЛИ - НЕ

Для И – НЕ при a=b= 1 обаn- канальных транзистора открыты, а для р- канальные заперты, на выходеy= 0. Если хотя бы один входной сигнал равен 0, то один из р- транзисторов откроется, а спаренный с нимn- канальный транзистор закроется иy= 1.

Аналогично для элемента ИЛИ – НЕ, когда a=b= 0 оба р- канальных транзистора открыты, аn- канальные закрыты.

На выходе

![]() .

Если хотя бы на один входaилиbили оба сразу

поступает

.

Если хотя бы на один входaилиbили оба сразу

поступает![]() ,

соответствующийn- канальный

открывается, парный р- канальный закроется

и на выходе

,

соответствующийn- канальный

открывается, парный р- канальный закроется

и на выходе![]() .

.

Логические элементы КМОП с большим числом входов организованы подобным образом.

Практические рекомендации.

Затвор и подложка МОП транзистора, разделенные диэлектриком образуют конденсатор (С = 5 пФ). Электрическая прочность не превышает 150 – 200 В. На теле человека и на оборудовании за счет электризации могут возникать заряды статического электричества в несколько киловольт.

Для защиты транзисторов от повреждения высоким напряжением каждый вход ИС КМОВ снабжают диодно защитной цепью.

R= 0,5 – 1,5 кОм

В зависимости от значения и полярности

перегрузочного напряжения диоды либо

проводят в прямом направлении

![]() В, либо находятся в режиме лавинного

пробоя, который наступает при обратном

напряжении 30 – 35 В. Лавинный пробой

диодов имеет обратимый характер и на

работоспособности ИС не отражается.

В, либо находятся в режиме лавинного

пробоя, который наступает при обратном

напряжении 30 – 35 В. Лавинный пробой

диодов имеет обратимый характер и на

работоспособности ИС не отражается.

В нормальных условиях, когда амплитуда

входного напряжения не выходит за

пределы – 0,7 В

![]() В отпирания входных диодов не происходит.

В отпирания входных диодов не происходит.

Предельный допустимый ток охранных

диодов

![]() мА (

мА (![]() мА).

мА).

Если на вход поступают большие напряжения, то на вход подключают дополнительный ограничивающий резистор для ограничения тока через диоды (до 1 – 2 мА)

![]() .

.

При работе ИС на большую емкостную нагрузку (С > 500 пФ) для защиты выходных транзисторов и выходу добавляется ограничивающий резистор.

Входы КМОП микросхем (в отличие от ТТЛ) недопустимо оставлять свободными на не подсоединенных входах могут возникнут непредсказуемые напряжения за счет наводок и связей через паразитные ёмкости.

Микросхемы КМОП при

В допускают короткие замыкания выхода

с шины питания или общей шиной.

В допускают короткие замыкания выхода

с шины питания или общей шиной.Для создания уровней логических “1” и “0” входы непосредственно соединяют с шинами питания и общей шиной соответственно.

Для согласования выходных уровней КМОП структур со входами ТТЛ схем применяются ИСК561ЛН2 и К561ПУ4. ЛН2 содержит 6 инверторов, а ПУ4 6 повторителей с повышенной нагрузочной способностью по току.

Для согласования выхода ТТЛ со входом

КМОП при питании последних повышенным

напряжением

![]() >5

В применяют ИС К561ПУ7, ПУ8, содержащих по

шесть преобразователей уровня. ПУ8

выполняет эту операцию без инверсии, а

ПУ7 с инверсией.

>5

В применяют ИС К561ПУ7, ПУ8, содержащих по

шесть преобразователей уровня. ПУ8

выполняет эту операцию без инверсии, а

ПУ7 с инверсией.