- •Логические элементы ттл.

- •Основные электрические параметры

- •Основные характеристики серии ис ттл

- •Логические элементы ттлш

- •Логические элементы с тремя выходными состояниями.

- •Практические рекомендации:

- •Логические элементы кмоп

- •Основные характеристики серии кмоп

- •Базовые элементы кмоп

- •Инверторы кмоп с тремя выходными состояниями

- •Двунаправленный ключ.

- •Логические элементы кмоп.

- •Практические рекомендации.

Логические элементы ттл.

В ИС ТТЛ логики удачно сочетаются хорошие функциональные показатели: быстродействие, помехоустойчивость, нагрузочная способность, умеренное потребление энергии, невысокая стоимость.

Принцип действия различных модификаций ТТЛ одинаков и различаются они главным образом временем задержки сигнала и потребляемой мощностью.

Основные электрические параметры для всех серий ТТЛ согласованы, поэтому элементы различных серий: могут непосредственно соединятся друг с другом.

Основные электрические параметры

Напряжение питания:

![]() В

В

Выходное напряжение

Высокий уровень

![]() В

В

Низкий уровень

![]() В

В

Входное напряжение

Высокий уровень

![]() В

В

Низкий уровень

![]() В

В

Основные характеристики серии ис ттл

|

Микросхема |

Номер серии |

один элемент, НС |

потребления) на 1 эл. мВт |

Эл, пДж |

|

Универсальная (стандартная) |

133 135 |

10 |

10 |

90 |

|

Быстродействующая |

130 К131 |

6 |

23 |

200 |

|

Микромощная |

134, КР134 |

33 |

1 |

30 |

|

На транзисторах Шоттки (маломощная) |

530, К531 533, К555 1533 1531 |

3 9,5 4 3 |

19 2 1,2 4 |

57 19 4,8 12 |

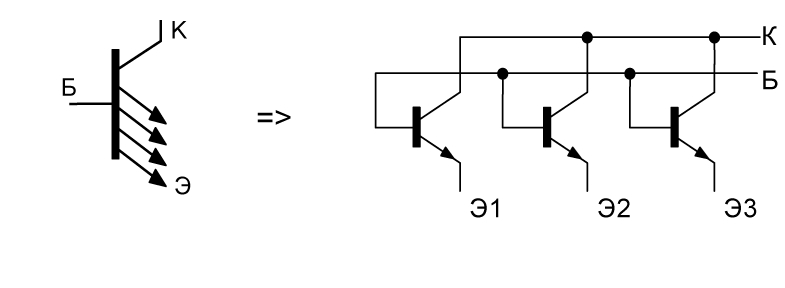

Основная особенность ИС ТТЛ состоит в том, что во входной цепи используется специфический интегральный прибор – многоэмиттерный транзистор – он имеет несколько эмиттеров, объединенных общей базой.

Эквивалентен нескольким независимым транзистором с объединенными базами и коллекторами.

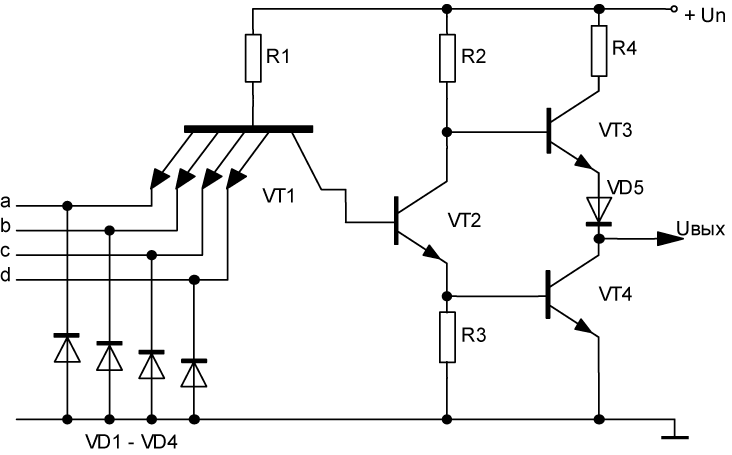

Рассмотрим принципиальную схему базового элемента И – НЕ 155 серии.

Схема содериний три каскада:

Входной

Фазорасщепительный

Выходной

.

.

![]() - смещены в обратном направлении и не

влияют на работу при нормальном

использовании.

- смещены в обратном направлении и не

влияют на работу при нормальном

использовании.

Когда один или несколько входов соединены

с ”землей” (лог. ”0”) то переход Б – Э

смещен в прямом направлении. Напряжение

по базе ~ 0,7 В недостаточно для открывания

трех переходов – коллекторного

![]() и двух эмиттерных

и двух эмиттерных![]() .

Так как

.

Так как![]() заперт,

на его коллекторе – высокое напряжение.

Транзистор

заперт,

на его коллекторе – высокое напряжение.

Транзистор![]() и диод

и диод![]() открыты. Выходное напряжение

открыты. Выходное напряжение![]() В

(без нагрузки)

В

(без нагрузки)

Когда на все входы действует напряжение

высокого уровня, транзистор

![]() работает в инверсном режиме (переход Б

– Э смещен в обратном направлении, а Б

– К - в прямом.) Ток, протекающий через

работает в инверсном режиме (переход Б

– Э смещен в обратном направлении, а Б

– К - в прямом.) Ток, протекающий через![]() ,

,![]()

![]() открывает

открывает![]() .

Эмиттерный ток

.

Эмиттерный ток![]() создает падение напряжения на

создает падение напряжения на![]() ,

достаточное для открывания

,

достаточное для открывания![]() .

.![]() запрет, поэтому

запрет, поэтому![]() В (напряжение насыщения

В (напряжение насыщения![]() ).

Диод

).

Диод![]() создает дополнительное смещение для

надежного запирания

создает дополнительное смещение для

надежного запирания![]() в этом режиме.

в этом режиме.

Типичная передаточная характеристика

Быстродействие ИС ТТЛ можно повысить двумя способами:

Уменьшая сопротивление резисторов и паразитные ёмкости.

Предотвращая насыщение транзисторов, а следовательно, и накопление зарядов в базах.

В сериях 130, 131 выходной каскад выполнен на составном транзисторе, который обладает меньшим выходным сопротивлением, что способствует быстродействию.

В микромощных сериях мощность потребления снижена за счет повышения номиналов используемых резисторов.

Логические элементы ттлш

Другой метод повышения быстродействия, причем более результативный и перспективный состоит в применении транзисторов с барьером Шотки.

Диод Шотки – металлополупроводниковый выпрямляющий контакт. Отличие от диодов с р - nпереходов состоит:

время выключения ДШ очень мало (100 пс) и не зависит от температуры. У обычных диодов (1 – 100 нС).

Для отпирания диодов Шотки требуется напряжение 0,2 – 0,4 В против 0,5 – 0,8 В для диодов с р – nпереходом и может регулироваться подбором металла, образующего контакт с полупроводником.

Диоды Шотки подключаются параллельно коллекторному переходу транзистора и придают ему ряд новых качеств, которые называются транзисторами Шотки.

а) Распределение напряжений б) Транзистор в) Условное изображение

в насыщенном транзисторе с барьером Шотки транзистора Шотки

Когда Tзаперт потенциал

К выше потенциала Б, диод смещен в

обратном направлении и не влияет на

работу транзистора. Когда в процессе

открывания транзистора потенциал базы

становится больше потенциала коллектора

диод открывается и на нем устанавливается

напряжение![]() .

Остаточное напряжение на коллекторе

транзистора

.

Остаточное напряжение на коллекторе

транзистора![]() .

То есть режима насыщения не возникает.

Благодаря этому при запирании транзистора

исключается задержка, выраженная

рассасыванием избыточного заряда.

.

То есть режима насыщения не возникает.

Благодаря этому при запирании транзистора

исключается задержка, выраженная

рассасыванием избыточного заряда.

На рисунке приведена принципиальная схема и передаточная характеристика базового логического элемента И – НЕ.

Фазарасщипительный каскад имеет

корректирующую цепочку

![]() ,

позволяющую получать передаточную

характеристику по форме, близкую к

прямоугольной. Благодаря применению

транзистора Дарлингтона, получается

малая выходное сопротивление,

обеспечивающее симметричную задержку

,

позволяющую получать передаточную

характеристику по форме, близкую к

прямоугольной. Благодаря применению

транзистора Дарлингтона, получается

малая выходное сопротивление,

обеспечивающее симметричную задержку![]() .

.

Логические элементы И – НЕ наиболее характерны для семейства ТТЛ . Они производятся в виде самостоятельных изделий, а также служат основой для построения других устройств.

Увеличение числа входов (расширение по И) можно организовать из нескольких схем И – НЕ, пользуясь законом Де Моргана или подключением дополнительных, внешних диодов и резистора к любому из входов И – НЕ. Значение резистора

![]() кОм.

кОм.

Существует так же специальные микросхемы расширителей по ИЛИ (экспандеры).

Существуют ИС двух типов:

ИС со входами расширения.

ИС микросхемы – расширители.

И С

со входами расширения имеют

С

со входами расширения имеют

Логические входы a,b,c,..z.

Входы расширения киэ.

Логический выход F.

Входы расширения киэявляются дополнительными внешними выводамикиэтранзистора фазорасщипительного каскада логического элемента.

Микросхемы расширители имеют группу логических входов a,b,c,.. и выходы расширения киэ.

Представляет собой многоэмиттерный транзистор, выходами которого служат открытые киэ.

На выходах

![]() и

и![]() формируются сигналы, которые зависят

как от входных сигналов

формируются сигналы, которые зависят

как от входных сигналов![]() так и от

так и от![]() .

.

![]()

В данном случае

![]() .

.

ИС с открытым коллектором.

Непосредственные соединения выхода в

разных ИС невозможно, так как если в

одном элементе будет открыт верхний, а

в другом нижний выходные транзисторы,

то с цепи потечет ток, ограниченный

только резистором

![]() ,

что вызовет пробой транзисторов.

,

что вызовет пробой транзисторов.

При соединении ИС параллельно, значение

резистора

![]() выбирают из условия обеспечения

выбирают из условия обеспечения![]() :

:

![]()

![]()

![]() - число объединенных выходов и подключенных

входов.

- число объединенных выходов и подключенных

входов.

![]() - ток утечки на выходе. Минимальное

сопротивление определяется из условия:

- ток утечки на выходе. Минимальное

сопротивление определяется из условия:

![]() ;

;

где

![]() -maxдопустимый выходной

ток лог. “0” одного элемента.

-maxдопустимый выходной

ток лог. “0” одного элемента.