- •Центральный процессор

- •1. Повышение производительности процессоров

- •2.1. Технологии многопоточности

- •2.2. Технология Hyper-Threading

- •2.3. Многоядерность

- •2.4. Технология виртуализации Hypervisor

- •2.5. Технология удаленного управления компьютерами сети

- •2.6. Технология ускорения процесса ввода-вывода данных – Acceleration Technology

- •3. Многоядерные процессоры корпорации Intel

- •3.1. Архитектурные особенности процессора Pentium d

- •3.2. Судьба системной шины

- •3.3. Производительность

- •3.4. Многоядерное будущее

- •5. Многоядерные процессоры компании ibm

- •5.1. Двухъядерный (dual-core) процессор Power 4

- •5.2. Следующий шаг - Power 5

- •5.5. Процессорный элемент Cell -"суперкомпьютер-на-кристалле"

- •7. Заключение

- •8. Планы Intel на 2009/2010 гг по выпуску процессоров

- •9. Тенденции развития средств вычислительной техники

- •1. Повышение тактовой частоты.

- •2. Увеличение объема и пропускной способности подсистемы памяти.

- •4. Системы на одном кристалле и новые технологии.

3.3. Производительность

Производительность многоядерных процессоров стала зависеть от качества работыпрограммистов. Успехмассовогопрограммного обеспечения (ПО)зависит отегоспособности"распараллеливать"задачи. КорпорацияIntel взяласьза разработкуинструментария длянаписания таких программ и оптимизации существующих.

3.4. Многоядерное будущее

В сентябре 2006 годасостояласьдемонстрацияпрототипапроцессораIntel, обладающего производительностью в 1 терафлоп (1012 операций с плавающей точкой всекунду).Длятогочтобыпредставить,насколько этомного, приведем пример.

Первыйсуперкомпьютер, достигшийпроизводительности в 1 терафлоп, ASCI Red, был создан в 1996 году. В его состав входило 4,5 тысячи процессоров Pentium Pro,работавших на частоте 200 МГц.

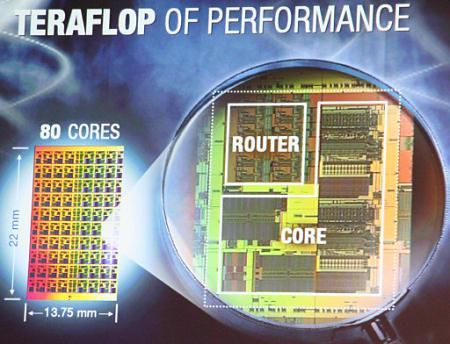

Рис.5. 80-ядерный прототип процессора Intel

Процессор имеет 80 ядер (рис.5) и интегрированную статическую память (SRAM) общим объѐмом в 20 Мб (по 256 Кб на ядро). Обмен данными между ядрамипроцессора осуществляетсясоскоростью более терабайта всекунду.

Нынешние образцы 80-ядерныхпроцессоров работаютначастоте 3,1 ГГц. Ожидается, что коммерческая доступность таких процессоров наступит в течение пятилет.

В настоящиймоментнельзя говорить о том,чтопереднамиполнофункциональная версия процессоров будущего, скорее - одно из первых воплощенийконцепта, разработанного в рамкахинициативыIntel Tera-Scale,цельюкоторой является доступность длямассовогопокупателяпроцессоров спроизводительностью терафлоп уже к 2010-му году.

5. Многоядерные процессоры компании ibm

5.1. Двухъядерный (dual-core) процессор Power 4

В 2001 г. корпорация IBM (http://www.ibm.com/) разработала свой первыйуниверсальный двухъядерный (dual-core)процессорPower 4,предназначенный длясерверов IBM eServer.

Устройство Power 4 было уникально для своего времени тем, что в нем в одномкорпусе содержалось два 64-разрядных микропроцессора.

Архитектуру кристалла Power 4 отличало несколько современных решений:

суперскалярная структура,

внеочередное исполнение команд,

большаякэш-память на кристалле,

специализированный порт для основной памяти,

высокоскоростные соединения для объединениямикропроцессоров всистемы с архитектурой распределенной разделяемой памяти.

КаждыйпроцессорPower 4имел дваконвейерных блока для работы с 64- разрядными операндами сплавающей точкой, выбирающихнаисполнениепопятькоманд каждый, и два блока для работы с памятью. Процессоры содержали раздельнуюкэш-память команд и данных 1-го уровня емкостью по 64 Кбайт каждая. Кроме того,имелась разделяемая(общая)кэш-память2-гоуровнянакристалле (емкостью 1,4 Мбайт) и внешняя кэш-память 3-го уровня (емкостью 32 Мбайт).

Наличие кэш-памяти 2-го уровня, разделяемой двумя процессорами кристалла, а также внешнимипроцессорами другихкристалловчерезмагистрали шириной 128 разрядов, работающие на тактовой частоте более 500 МГц (что обеспечиваетпропускнуюспособностьсвыше 10 Гбайт/с)стало однойиз отличительных особенностей Power 4 .

Физическикэш-память2-гоуровняемкостью около 1,4 Мбайтсостоялаизнескольких одинаковых блоков, доступ ккоторым выполнялсячерезкоммутатор спропускной способностью на уровне 100 Гбайт/с. Протокол когерентности обеспечивалразмещение данных в том блоке кэш-памяти, который использовался для размещения данных последним. Порт кристалла Power 4, предназначенный для подключения кэш-памяти3-гоуровняемкостью до 32 Мбайт,имел 128 разрядов длякаждогоиз двухнаправлений пересылки данных. Порт функционировал не на полной тактовой частотепроцессоровкристалла,но, темнеменее,припередаче обеспечивалпропускнуюспособность на уровне 13-14 Гбайт/с. Теги для адресации кэш-памяти 3-го уровня были расположены внутрикристалла,чтоускоряло реализациюпротоколакогерентности. Скорость передачи данных междукэш-памятью 3-го уровня и основной памятью могла достигать 12,8 Гбайт/с.

КаждыйсдвоенныйпроцессорPower 4 былупакован вкерамическиймультипроцессорный модуль (размером 4,5х4,5 дюйма) вместе с тремя другимикристаллами. Эта базовая строительная единица называлась MCM (MultiChip Module). Такой модуль, содержащий четыре микросхемы Power 4, объединял фактически восемьпроцессоров. Многослойный керамический корпус модуля MCM содержал магистрали,соединяющиемикросхемымеждусобой, а также смодулямикэш-памяти и высокоскоростнымкоммутатором для связи с удаленными процессорами. ЧетыремикросхемыPower4, образующие восьмипроцессорнуюконфигурацию, были расположены в модуле под углом 90° друг относительно друга, что позволяломинимизировать длину шин,соединяющихмикросхемымежду собой,что важнопри работена высоких тактовыхчастотах.Шины расширениясвязывалимеждусобой имодули МСМ. В этих шинах использовалась уникальная технология волновойконвейеризации (wave pipelining), обеспечивающаянизкие величины задержек.

Стоит отметить, что наряду с параллелизмом на уровне команд процессор Power 4использовал ипараллелизмнауровнепотоков (тредов).Базоваямногопоточностьиспользоваласьеще впроцессорахPowerPC RSIV(S-Star) -но вэтомпроцессоре вкаждый момент времени выполнялся только один поток команд. Если при выполнениикоманды одногопотока возникалазначительнаязадержка (например, вкэш-памяти отсутствовали необходимые данные), то процессор переключался на другой поток, чтоуменьшалоегопростаивание. Однако обапотокасовместноиспользовалимногиесистемные ресурсы (например,архитектурные регистры),поэтомунапереключениемежду потоками тратилось несколько тактов.

Динамическое выявлениепараллелизма вPower 4позволилопредотвращатьпростои процессора при трудно выявляемых статически ситуациях, например, промахепри обращении к кэш-памяти.

КомпанияIBMпервойинтегрировала вкристалл двапроцессорных ядра — в технологииPower 4. Присоздании этойархитектуры она ориентировалась,прежде всего,на рынок высокопроизводительныхсерверов исуперкомпьютеров,поддерживающих 32-процессорныесимметричныемногопроцессорные (SMP) -системы.

МикропроцессорPower 4создавался для работыкак скоммерческими (серверными), так и с научно-техническими приложениями.Разработка Power велась на базе RISC-архитектуры (Reduced InstructionsSetComputer).

Предусматриваетсяфиксирование длины команд, а такжеиспользованиеуниверсальных регистров. Командыупрощаются для того,чтобы онимогли выполнятьсяза одинтакт. Понятно,что эффективность вычисленийповышаетсяпри оптимизацииконвейеракоманд. ВпроцессесозданияPower разработчики решилиминимизировать не только время каждого цикла, но и полное время, необходимое для выполненияконкретнойзадачи, длячего была внедрена технологиясуперскалярной обработки данных.

Вспомним, что каждое из ядер процессора Power 4 обладает собственным кэшпервого уровня для данных и инструкций (соответственно LD 1 и LI 1) и общим кэш второго уровня (L2). Кэш память управляется тремя раздельными, автономно работающимиконтроллерами,которыеподключаются кпроцессорным ядрамчерезкоммутатор (Core Interface Unit - CIU). За такт контроллеры могут выдавать до 32 байт данных. Общий кэш для нескольких ядер хорошо сказывается на производительностипроцессора благодаря более быстрому доступу к совместно используемой информации, однако при таком способе организации велика вероятность возникновения конфликтов,многоступенчатая же организациякэшпозволяетиспользоватьегонаиболее эффективно.

Очевидно, что скорость передачи данных между процессором и памятьюсущественно влияет на потенциал многоядерных устройств. Коммуникация каждого изPower 4 осуществляется коммутатором CIU посредством двух раздельных 256-битовых шин для выборкиинструкций изагрузки данных, а также отдельной 64-битовойшины длясохранения результатов.

Для поддержкикогерентности вкэш -памяти второгоуровняL2применена расширенная версияизвестногопротокола MESI с длинойстроки 128 байт, а вL3использована модель с пятью состояниями когерентности (поддержка осуществляетсяна уровне 128-байтных секторов).

Отдельный функциональный блок, так называемый контроллер матрицы, отвечаетза обмен даннымимеждуконтроллерамикэш-памяти второго и третьегоуровней и за коммуникационные функции архитектуры Power 4. В процессоре широкоприменяютсямеханизмыпрогнозирования ветвлений. Адресноепространствосоставляет 512 Гбайт.

Отметим, что протокол MESI применяет и AMD, точнее, доработанный MESI-MOESI. Внем процессоры могут использовать данные кэш-памяти друг друга, для чего во время чтения информации происходит проверка кэш-памяти соседей и при обнаружениинеобходимыхсведенийсчитываниепроисходитпрямо оттуда. Причем эти данные в оперативнойпамятинесохраняются, а владелецинформации делаетпометку напротив обновленнойстроки. Любоеизменение строки приводит кустареваниюаналогичныхстрок вкэш другихпроцессоров, а вслучае вытеснения обновленныхстрок (Owner-строк) онизаписываются в оперативнуюпамять.

При разработкепроцессораPower 4 былапоставленазадача оптимизацииSMP-конфигурациисервера. Для тогочтобысерверна базеPower 4 был готов к работе вмногозадачныхсредах с высокими требованиями кпропускнойспособности, и былиупакованы в одинмодульчетыре двуядерныхпроцессора, образуя восьмипроцессорную SMP систему. Для соединения процессоров между собой вместоцентральногокоммутатораиспользуетсямножествонезависимых шин c топологией типа "точка—точка".